# VAX 7000 Technical Bulletin Number 4

Order Number EK-70TBA-T4. A01

This document accompanies the release of the KA7AC CPU module used in VAX 7000/10000 systems.

#### First Printing, October 1995

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright © 1995 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation: AlphaGeneration, AlphaServer, DEC, DECchip, DEC LANcontroller, OpenVMS, StorageWorks, VAX, the AlphaGeneration logo, and the DIGITAL logo.

**FCC NOTICE:** The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

# Contents

| Prefa      | cev                                                 |

|------------|-----------------------------------------------------|

| Section    | on 1 Installation                                   |

| 1.1<br>1.2 |                                                     |

| Section    | on 2 User Information                               |

| 2.1        | Registers                                           |

| Table      | S                                                   |

| 2-1        | KA7AC BIU CTL Register Bit Definitions, Revised 2-3 |

### **Preface**

#### **Intended Audience**

This document is written for system managers and service engineers.

### **Document Purpose**

This technical bulletin provides information to update the VAX 7000/10000 documentation set. Since the original documentation set was published, we have issued one other Technical Bulletin that is a part of the documentation set:

• DEC 7000 AXP VAX 7000 Technical Bulletin Number 3 EK-70TBA-T3

If you have an Internet account, you may mail us your comments on VAX 7000/DEC 7000 hardware documentation. Please mail your comments, suggestions, and corrections to **msbdoc@lando.enet.dec.com.** We will reply to all comments. Digital values your input.

## Section 1

## Installation

The KN7AC processor modules can be used to upgrade VAX 7000/10000 systems.

#### Sections include:

- Changes

- System Upgrades

### 1.1 Changes

VAX systems using KA7AC modules are currently supported by OpenVMS VAX Version 6.1 or later.

#### **VAX Systems**

The NV5 CPU chip on the KA7AC module provides improved performance over the NVAX and NVAX+ chips. The CPU chip is implemented in CMOS-5 technology. The chip speed of the KA7AC NV5 chip is 170.9 MHz compared with the chip speed of 137.5 on the KA7AB module and 91 MHz for the KA7AA NVAX+ chip.

One internal processor register has changed: the BIU Control Register.

#### **Console Revision Requirements**

KA7AC —V4.1 or later console is required.

### 1.2 System Upgrades

Upgrades can be of various types. Modules must be returned when the upgrade replaces the current CPU modules.

Upgrades can be of the following types:

- Upgrading from KA7AA or KA7AB modules to KA7AC modules

- Adding a KA7AC to an existing VAX system with KA7AC modules

Complete installation instructions are packaged with each CPU module.

## Section 2

## **User Information**

### Changes to registers:

• KA7AC BIU Control Register

### 2.1 Registers

The following register information updates that given in the KA7AA CPU Technical Manual. The registers described are onchip registers.

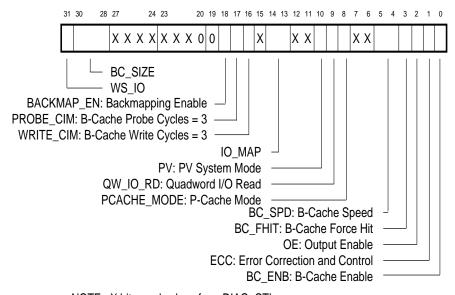

### KA7AC BIU Control Register (BIU\_CTL)

Address 00A0 Access R/W

The BIU\_CTL register controls certain operations and parameters related to the P-cache, B-cache, and I/O mapping. This register reads the complement of its contents.

NOTE: X bits read values from DIAG\_CTL. This register reads inverted.

BXB-0213A-93

Table 2-1 KA7AC BIU\_CTL Register Bit Definitions, Revised

| Name       | Bit(s) | Туре   | Function                                                                                                                                                                                                                                            |

|------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BACKMAP_EN | <18>   | R/W, 0 | Backmap Enable. Controls whether internal IRead aborts, which have been backmapped, generate invalidates to the P-cache. The console program sets this bit to 1.                                                                                    |

| PROBE_CIM  | <17>   | R/W, 0 | Probe Cache Cycle Injection Mode. Controls the number of CPU cycles for all B-cache probes when set. The console program sets this bit to 1, which allows all B-cache probe cycles to increase from 2 to 3 CPU cycles.                              |

| WRITE_CIM  | <16>   | R/W, 0 | Write Cache Cycle Injection Mode. Controls the number of CPU cycles for all B-cache writes when set. The console program sets this bit to 1, which increases the assertion duration on the dataWE_h<3:0> and tagCtWE_h pins from 2 to 3 CPU cycles. |