# 「M03 Magnetic Tape Formatter User Guide

1st Edition, May 1977 2nd Printing (Rev), July 1978 3rd Printing (Rev), July 1979

Copyright© 1977, 1978, 1979 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

# **CONTENTS**

|           |                                                             | Page |

|-----------|-------------------------------------------------------------|------|

| CHAPTER 1 | GENERAL INFORMATION                                         |      |

| 1.1       | INTRODUCTION                                                | 1-1  |

| 1.2       | GENERAL DESCRIPTION                                         |      |

| 1.3       | FUNCTIONAL DESCRIPTION                                      |      |

| 1.3.1     | Introduction                                                |      |

| 1.3.2     | System Operation                                            |      |

| 1.3.2.1   | Massbus Interface Module (M8909-YA)                         |      |

| 1.3.2.2   | Bit Fiddler Module                                          | 1-8  |

| 1.3.2.3   | Maintenance Register Module (M8905-YB)                      | 1-8  |

| 1.3.2.4   | Tape Control-NRZI Module (M8934)                            |      |

| 1.3.2.5   | Data Sync-PE Module (M8901)                                 | 1-9  |

| 1.3.2.6   | Tape Control-PE Module (M8932)                              | 1-9  |

| 1.3.2.7   | Tape Control Common Mode (TCCM) Module (M8933)              | 1-9  |

| 1.4       | RELATED DOCUMENTS                                           |      |

| 1.5       | UNIT SPECIFICATIONS                                         | 1-11 |

| CHAPTER 2 | PROGRAMMING INFORMATION                                     |      |

| 2.1       | REGISTER FUNCTIONS AND FORMATS                              | 2-1  |

| 2.1.1     | Control Register [(CS1) Register 00 <sub>8</sub> ]          |      |

| 2.1.2     | Status Register [(DS) Register 01 <sub>8</sub> ]            |      |

| 2.1.3     | Error Register [(ER) Register 02 <sub>8</sub> ]             |      |

| 2.1.4     | Maintenance Register [(MR) Register 03 <sub>8</sub> ]       |      |

| 2.1.5     | Attention Summary Register [(AS) Register 04 <sub>8</sub> ] |      |

| 2.1.6     | Frame Count Register [(FC) Register 05 <sub>8</sub> ]       |      |

| 2.1.7     | Drive Type Register [(DT) Register 06 <sub>8</sub> ]        |      |

| 2.1.8     | Check Character Register [(CK) Register 07 <sub>8</sub> ]   |      |

| 2.1.9     | Serial Number Register [(SN) Register 10 <sub>8</sub> ]     |      |

| 2.1.10    | Tape Control Register [(TC) Register 11 <sub>8</sub> ]      | 2-15 |

| 2.2       | DATA FORMATS                                                |      |

| 2.2.1     | Massbus/TM03 Transfers                                      | 2-17 |

| 2.2.2     | TM03/Tape Frame Packing                                     | 2-18 |

| 2.3       | COMMAND FUNCTIONS                                           | 2-20 |

| 2.3.1     | No-Op                                                       | 2-20 |

| 2.3.2     | Rewind, Off-Line                                            |      |

| 2.3.3     | Rewind                                                      |      |

| 2.3.4     | Drive Clear                                                 |      |

| 2.3.4.1   | Drive Clear Resets                                          |      |

| 2.3.4.2   | Drive Clear versus Initialize (INIT)                        |      |

# **CONTENTS** (Cont)

Read-In Preset ......2-24

2.3.5

2.3.6

Page

| 1-6                             | TM03 Front Panel TM03 in a System Configuration |                   |

|---------------------------------|-------------------------------------------------|-------------------|

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5 | TM03 Tape Transport System Configuration        | 1-3<br>1-4<br>1-5 |

| Figure No.                      | Title                                           | Page              |

|                                 | FIGURES                                         |                   |

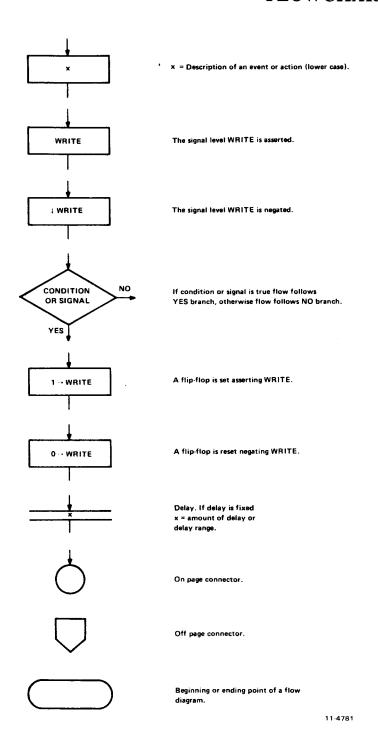

| APPENDIX B                      | FLOWCHART GLOSSARY                              |                   |

| APPENDIX A                      | GLOSSARY                                        |                   |

| 3.5                             | ACCEPTANCE TESTING                              | 3-6<br>3-8        |

| 3.4.3.2<br>3.4.3.3              | TU45 Transport TU77 Transport                   |                   |

| 3.4.3.1                         | TE16 Transport                                  |                   |

| 3.4.3                           | Slave Bus Cabling to Tape Transport             | 3-7               |

| 3.4.2.2                         | H9500 Corporate Cabinet                         |                   |

| 3.4.2.1                         | H950 Cabinet                                    |                   |

| 3.4.2                           | Massbus Cabling to Transport Cabinet            |                   |

| 3.4.1                           | TM03 Cabling                                    |                   |

| 3.4                             | INSPECTIONINSTALLATION PROCEDURES               |                   |

| 3.3                             | UNPACKING                                       |                   |

| 3.1<br>3.2                      | SITE PLANNING AND CONSIDERATIONS                |                   |

| CHAPTER 3                       | INSTALLATION                                    |                   |

| 2.5.3                           | Other Notes                                     | 2-28              |

| 2.5.2                           | Auto Density Select                             |                   |

| 2.5.1                           | NRZI Error Correction                           |                   |

| 2.5                             | PROGRAMMING NOTES                               |                   |

| 2.4                             | NRZI ERROR CORRECTION                           | 2-25              |

| 2.3.12                          | Write                                           |                   |

| 2.3.11                          | Read Reverse/Write Check Reverse                |                   |

| 2.3.10                          | Space ReverseRead Forward/Write Check Forward   | 2-2/              |

| 2.3.9                           | Space Forward                                   |                   |

| 2.3.7<br>2.3.8                  | Write Tape Mark                                 |                   |

# FIGURES (Cont)

| Figure No. | Title                                                                  | Page           |

|------------|------------------------------------------------------------------------|----------------|

| 1-7        | TM03 Basic Block Diagram                                               | 1-7            |

| 2-1        | Control Register Format                                                | 2-4            |

| 2-2        | Status Register Format                                                 | 2-6            |

| 2-3        | Error Register Format                                                  | 2-8            |

| 2-4        | Maintenance Register Format                                            | 2-11           |

| 2-5        | Drive Type Register Format                                             | 2_13           |

| 2-6        | Check Character Register Format                                        | 2-14           |

| 2-7        | Serial Number Register Format                                          |                |

| 2-8        | Tape Control Register Format                                           | 2-15           |

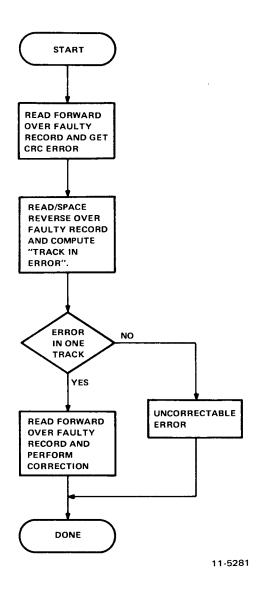

| 2-9        | Simplified NRZI Error Correction Flow Diagram                          | 2-26           |

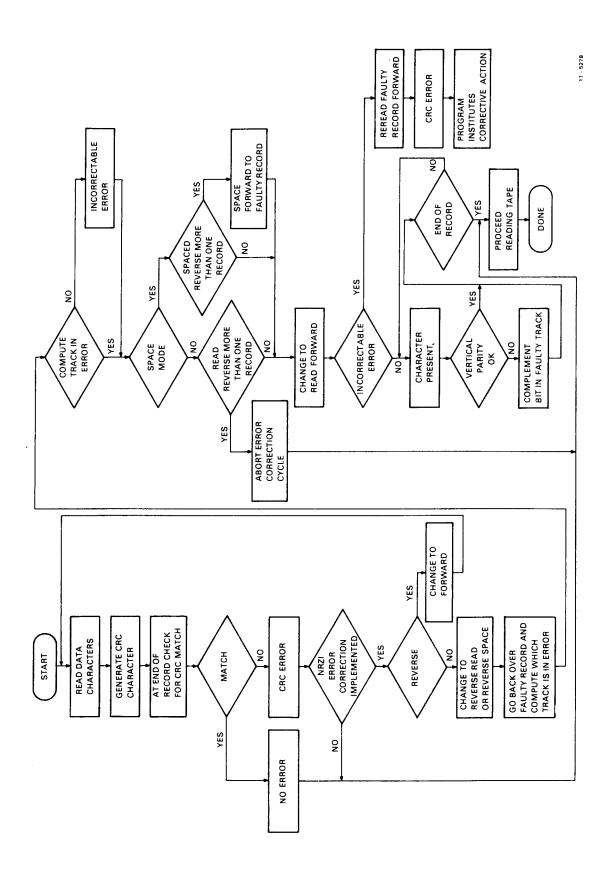

| 2-10       | NRZI Error Correction Flow Diagram                                     | 2 27           |

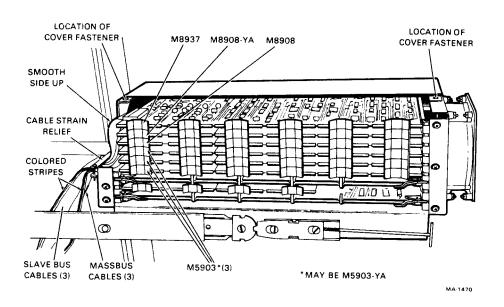

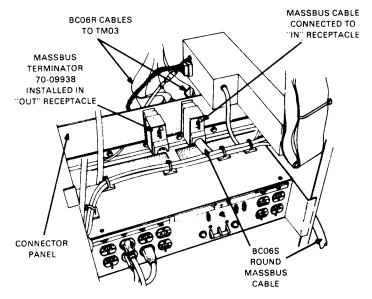

| 3-1        | TM03 Formatter with Cover Removed                                      | 3 2            |

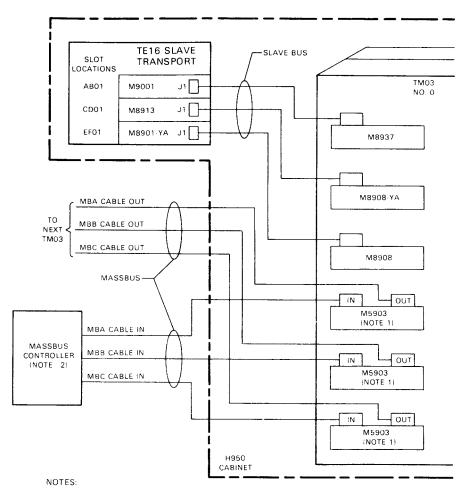

| 3-2        | TM03 Cabling to a TE16 Slave Transport in an H950 Cabinet              | 2 2            |

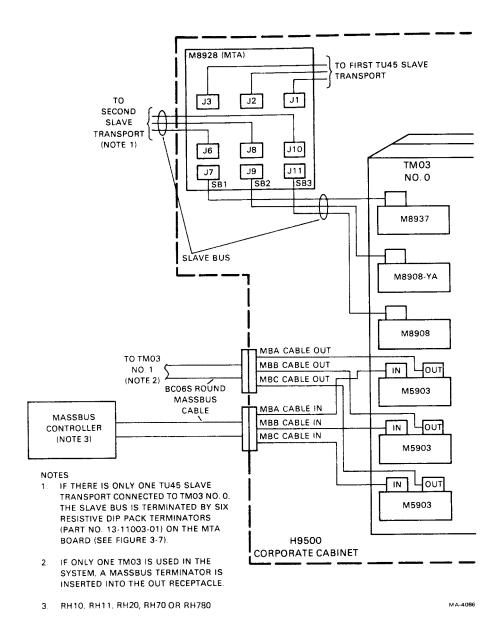

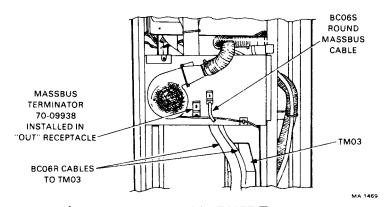

| 3-3        | TM03 Cabling to an M8928 MTA Adapter Board in a TU45 Transport         | 3-3            |

|            | in an H9500 Corporate Cabinet                                          | 2.4            |

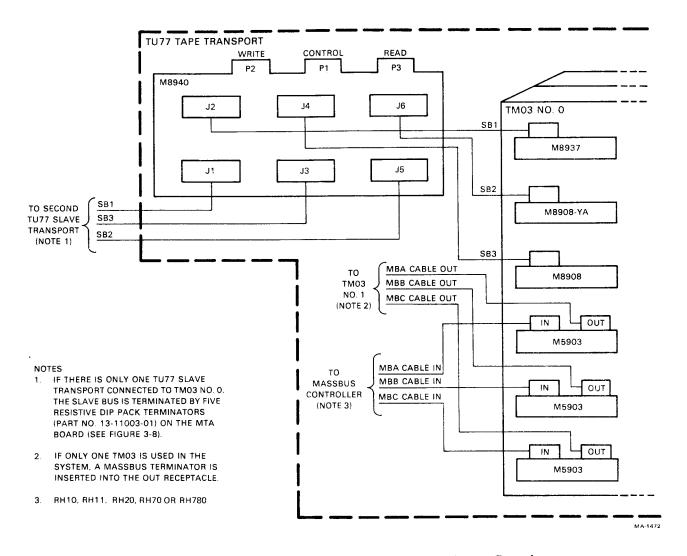

| 3-4        | TM03 Cabling to an M8940 MTA Adapter Board in a TU77 Transport         | 3-4            |

| ,          | in an H9500 Corporate Cabinet                                          | 2.5            |

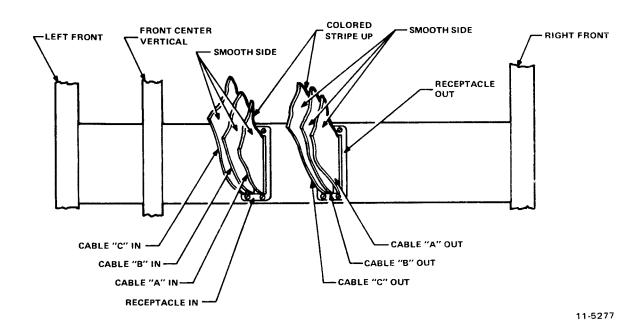

| 3-5        | External Cabling to Massbus Connector Panel in H9500 Corporate Cabinet | 3-3            |

| 3-6        | Internal Cabling to Massbus Connector Panel in H9500 Corporate Cabinet | 3-6            |

| 3-7        | Internal Cabling to Massbus Connector Panel in H9500 Corporate Cabinet | 3-/            |

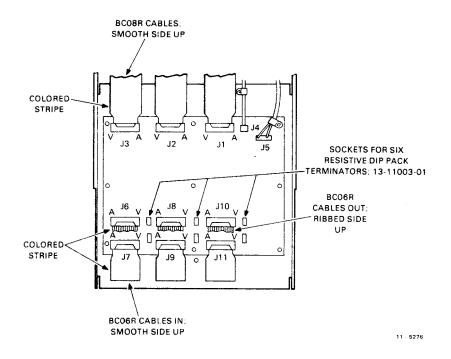

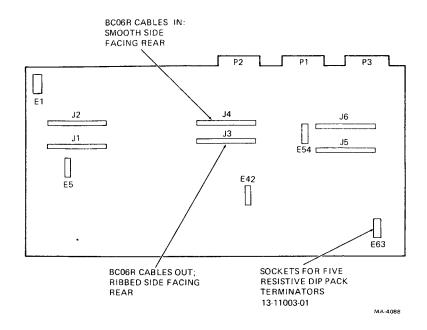

| 3-8        | Cable Orientation on M8928 MTA Module                                  | 3-8            |

|            | TABLES                                                                 |                |

| Table No.  | Title                                                                  | Page           |

| 1-1        | Related Documents                                                      | 1-10           |

| 1-2        | Unit Specifications                                                    |                |

| 2-1        | TM03 Registers                                                         |                |

| 2-2        | Command Function Codes                                                 |                |

| 2-3        | Status Register Bit Positions                                          |                |

| 2-4        | Error Register Bit Indicators                                          | 2-0<br>• • • • |

| 2-5        | Maintenance Register Bit Positions                                     | 2 11           |

| 2-6        | Drive Type Register Bit Positions                                      |                |

| 2-7        | Tape Control Register Bit Positions                                    |                |

| 2-8        | PDP-10 Massbus Word Format                                             | 2 10           |

| 2-9        | PDP-11 Massbus Word Format                                             | 2.10           |

| 2-10       | PDP-15 Massbus Word Format                                             | 2.10           |

| 2-10       | PDP-10 Compatibility Mode – Format Code 0011                           | 2-18<br>2 10   |

| 2-12       | PDP-10 Core Dump Mode – Format Code 0000                               |                |

| 2-13       | PDP-11 Normal Mode – Format Code 1100                                  |                |

| 2-14       | PDP-11 Core Dump Mode – Format Code 1101                               |                |

| 2-14       | PDP-15 Normal Mode – Format Code 1110                                  | 2-19           |

| 2-16       |                                                                        |                |

| 2-17       | PDP-15 Core Dump Mode – Format Code 0001                               |                |

| 4-1/       | Command Functions                                                      | 2-20           |

# CHAPTER 1 GENERAL INFORMATION

#### 1.1 INTRODUCTION

The TM03 Magnetic Tape Formatter serves as an interface between various magnetic tape transports and any Massbus controller. It provides control, data, status, and error information between the Massbus controller and a standard 1.27 cm (1/2 inch) magnetic tape unit (slave) operating at 114.3, 190.5, or 317.5 cm/second (45, 75, or 125 in/second). The TM03 is capable of reading and writing magnetic tape for information interchange at 800 bits/inch NRZI or 1600 bits/inch PE (phase encoded). It also has a forward and reverse read and spacing capability. The TM03 formats data from the PDP-10 and PDP-11 processors\* into tape frame characters and performs the reverse during a data read operation.

Aside from providing magnetic tape formatting, the TM03 offers the following features.

- 1. The TM03 provides automatic error correction of single-track errors in PE data (hardware controlled).

- 2. The TM03 provides automatic error correction of single-track errors in NRZI read data. (NRZI error correction is under software control and therefore does not occur automatically as does PE error correction.)

- 3. The TM03 provides automatic selection of either 800 bits/inch (NRZI) or 1600 bits/inch (PE) density during a read operation from BOT (beginning of tape).

- 4. The TM03 is capable of controlling from one to eight slaves. It should be noted that although the TM03 can handle tape speeds of 114.3, 190.5, and 317.5 cm/second (45, 75, 125 in/second), all slaves interfaced to any one TM03 must be operating at the same tape speed.

- 5. The TM03 writes an industry-compatible PE tape mark.

- 6. The TM03 performs extensive parity checking throughout all read and write data paths. In addition, the TM03 is equipped with self-contained maintenance mode operations which allow complete testing of all critical electronics under diagnostic control.

#### 1.2 GENERAL DESCRIPTION

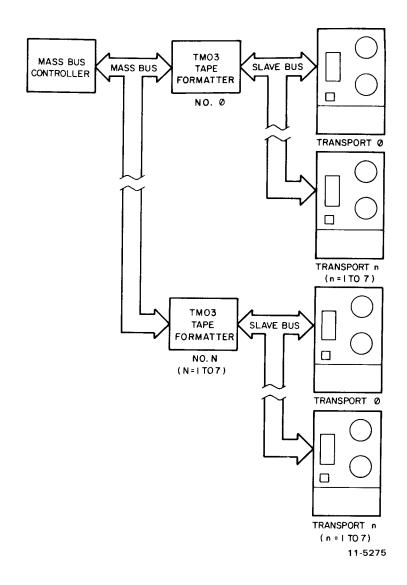

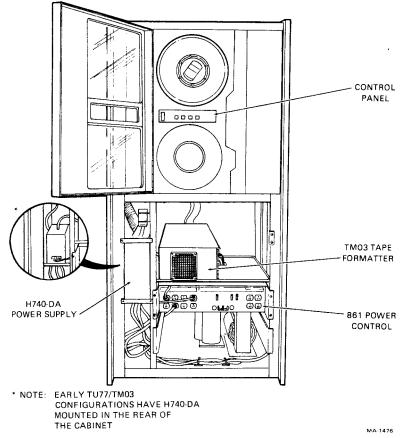

Figure 1-1 illustrates a TM03/tape transport system configuration. Each TM03 can control up to eight slave transports. In turn, each Massbus controller can control up to eight TM03 formatters. Thus, a maximum of 64 tape transports could be interfaced to a single Massbus controller.

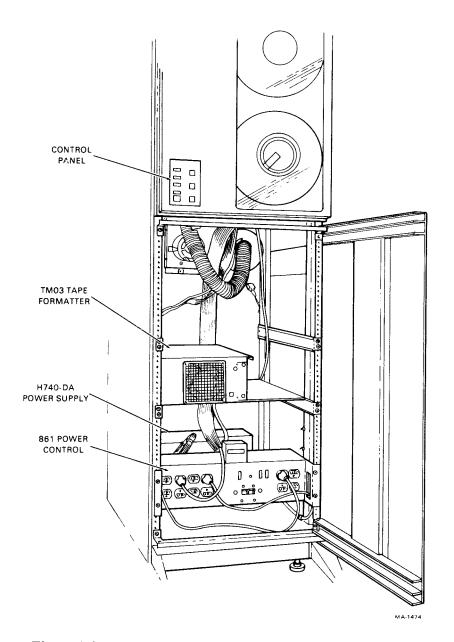

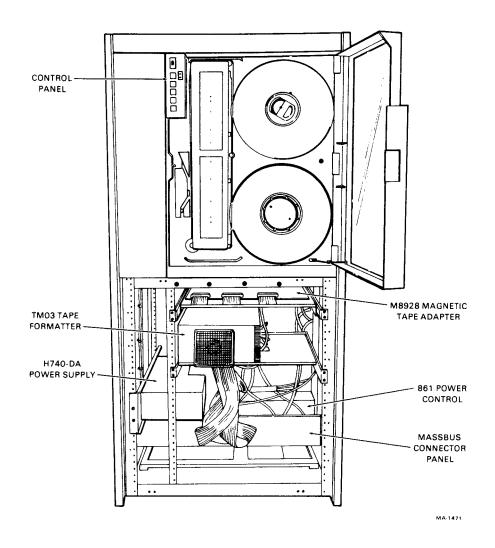

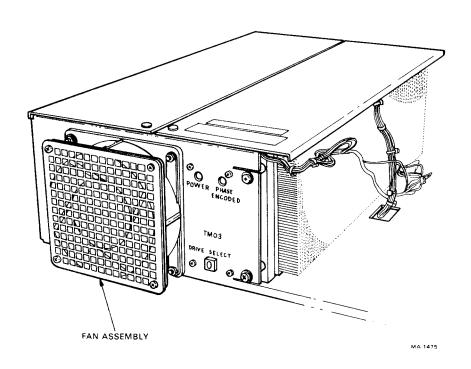

Figures 1-2, 1-3, and 1-4 show the TM03 in typical transport environments. An H740-DA power supply is required to provide power for the TM03. Figure 1-5 illustrates the TM03 front panel. A POWER indicator illuminates when power is applied to the TM03 from the H740-DA power supply. The PHASE ENCODED indicator illuminates when the TM03 is in the PE mode during a read or write operation.

<sup>\*</sup>Also the PDP-15 via a PDP-11 for interface to the Massbus (PDP-15 Unichannel).

Figure 1-1 TM03 Tape Transport System Configuration

Figure 1-2 TM03 with TE16 Tape Transport in H950 Cabinet

Figure 1-3 TM03 with TU45 Tape Transport in H9500 Corporate Cabinet

Figure 1-4 TM03 with TU77 Tape Transport in H9500 Corporate Cabinet

Figure 1-5 TM03 Front Panel

# 1.3 FUNCTIONAL DESCRIPTION

## 1.3.1 Introduction

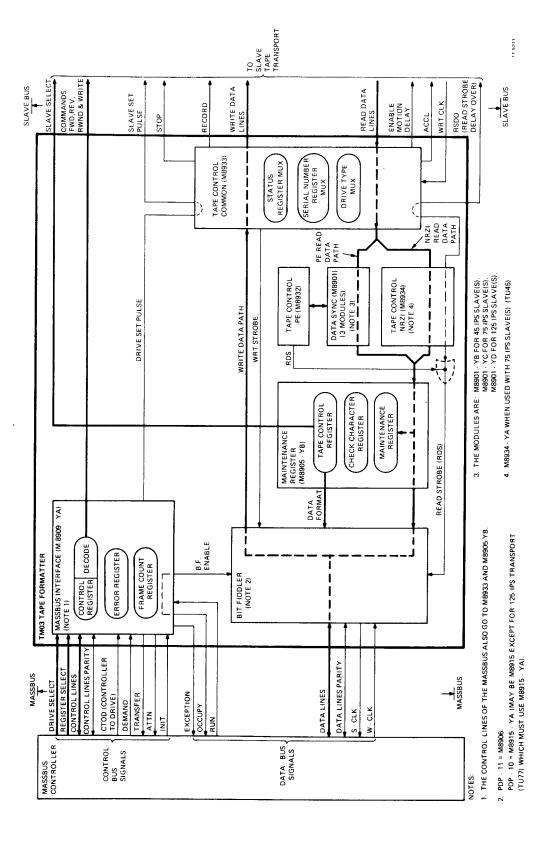

The TM03/tape transport system (Figure 1-6) interfaces with the central processor unit (CPU) via the Massbus controller. However, the Massbus controller is almost transparent to the CPU, and the CPU operates as though it were controlling the drive directly.

Figure 1-6 TM03 in a System Configuration

The TM03 interfaces with the Massbus controller via the Massbus. The Massbus consists of an asynchronous control bus with its associated control lines, and a synchronous data bus with its associated control lines. Transactions on the control bus control the TM03/transport and determine its status, while transactions on the data bus transfer data to or from the TM03/transport. Because the data and control buses operate independently, the Massbus controller can monitor drive status while a data transfer operation is being performed.

The TM03 can control up to eight tape transports via the slave bus. All transports controlled by a TM03 are "daisy-chained" on the slave bus (Figure 1-6). Essentially, this means that the transports are configured in parallel to each other. The slave bus consists of slave select lines, write data lines, read data lines, transport control lines, and various transport status lines.

#### 1.3.2 System Operation

Figure 1-7 is a block diagram of the TM03, and shows the major functional groups, control lines, and data paths. The following paragraphs describe these functional groups.

1.3.2.1 Massbus Interface Module (M8909-YA) – The Massbus interface module interfaces the TM03 with the Massbus controller. It contains circuitry that decodes the drive select signals on the Massbus. If enabled by the proper drive select address code, the Massbus interface can carry on the "handshake" operations with the Massbus controller, which read and write TM03 registers. The most important of the TM03 registers is the control register (CS1), which is located in the Massbus interface. The Massbus controller writes the function code of the next operation to be performed into the control register. The Massbus interface decodes this register and generates the appropriate control signals (FWD, REV, RWND, WRITE) to control the slave and various TM03 functions.

Figure 1-7 TM03 Basic Block Diagram

The Massbus interface module contains several other registers including an error register and a frame count register. The frame count register must be loaded prior to a space or write operation with the number (in 2's complement form) of records to be spaced or tape characters to be written. This register is incremented as the operation proceeds, and will terminate the operation with register overflow.

The Massbus interface decodes the control register to determine that a data transfer operation is to be performed. When this is the case, it generates OCC on the Massbus to notify the controller and other drives that it has occupied the data bus, and enables the bit fiddler.

1.3.2.2 Bit Fiddler Module\* The bit fiddler interfaces the TM03 data paths to the Massbus controller; it contains circuitry that performs synchronous data transfers on the data bus of the Massbus.

The bit fiddler is enabled for operation by the Massbus interface with BF ENABLE. The mode of bit fiddler operation is determined by control lines FMT0-3 (tape character format), WRITE (direction of transfer, i.e., read or write), and FWD (direction of tape motion, i.e., forward or reverse). WRITE and FWD are decodes of the control register function bits. FMT0-3 are the tape control register format bits, and are decoded in the bit fiddler.

During a write operation, the Massbus controller places a data word on the data bus. When the bit fiddler is ready to accept this data word, it issues SCLK (sync clock) to the controller, which replies with WCLK (write clock).

Upon receiving WCLK, the bit fiddler strobes in the word on the data bus, performs a data bus parity check, disassembles the data word into 8-bit characters, and generates a vertical parity bit for each 8-bit character. After generating WCLK, the controller places the next data word on the data bus. When the bit fiddler has finished disassembling the previous data word, it issues another SCLK, receives another WCLK, and strobes in the next data word for disassembly. The process continues until all the data has been transferred (precluding occurrence of data errors or other failures).

During a read operation, the bit fiddler assembles 8-bit characters into data words. When the data word has been assembled, it is placed on the data bus along with a parity bit (DPA), and the bit fiddler generates an SCLK pulse. When the Massbus controller receives SCLK, it strobes in the data on the data bus. The bit fiddler continues to assemble data characters into data words, and notifies the controller that a data word is available by generating SCLK. As in a write operation the method of assembly is determined by the FMT0-3, WRITE, and FWD signals input to the bit fiddler.

1.3.2.3 Maintenance Register Module (M8905-YB) – The maintenance register module is part of the read data path; read data is multiplexed through the maintenance register module from the PE or NRZI read circuitry (M8901 or M8934) to the bit fiddler. The maintenance register module also contains the tape control register, the check character register, and the maintenance register. The tape control register contains slave select bits, which are translated to slave bus signals (SS 0-2) and determine which slave will perform the operations specified by the Massbus controller. This register also contains tape data format information. Therefore, the tape control register must be properly loaded by the Massbus controller prior to the specification of a particular functional operation.

The maintenance register module plays an important role in maintenance mode operation. By writing into the maintenance register (R03), the Massbus controller can select one of several maintenance modes. These modes allow:

- 1. Testing of various TM03 circuits independently of the slave transport

- 2. Testing of the TM03 under tighter operation criteria.

<sup>\*</sup>M8915-YA, M8915, or M8906, depending on processor and transport.

1.3.2.4 Tape Control-NRZI Module (M8934)\* – The tape control-NRZI module performs functions relating only to NRZI data storage and retrieval. During an NRZI read operation, the tape control-NRZI module is part of the read data path. When informed by the slave that a tape character is available [RSDO (read strobe delay over) asserted], the tape control-NRZI module generates RDS (read strobe) and strobes the tape character from the tape control common mode module (M8933) into an NRZI read latch. The output of the latch, multiplexed through the maintenance register module, becomes available to the bit fiddler.

During an NRZI read operation, the tape control-NRZI module also generates and checks LRCC (longitudinal redundancy check character) and CRCC (cyclic redundancy check character), checks vertical parity, detects tape marks (file marks), performs error correction of single track errors if the software so specifies, and determines that the minimum criteria for normal termination have been met.

During an NRZI write operation, the tape control-NRZI module generates the CRCC.

1.3.2.5 Data Sync-PE Module (M8901)\* – The data sync module (one of three) is part of the PE read data path. It processes PE read data from the tape control common mode (TCCM) module (M8933), converting the PE information to binary and deskewing the data. It operates with the tape control-PE module (M8932) to detect preamble, data, postamble, and tape mark (TM). It also performs on-the-fly error correction of a single dead track based on vertical parity errors (VPE) detected by the tape control-PE module.

The data sync-PE module performs no write data path operations. However, it does a read-after-write during PE write operations.

1.3.2.6 Tape Control-PE Module (M8932) – During a PE read operation, the tape control-PE module operates with the data sync module to detect preamble, data, postamble, and TM. It also checks for vertical parity errors and PE format errors.

During a PE write operation, the tape control-PE module establishes the timing for writing preamble, data, and postamble.

1.3.2.7 Tape Control Common Mode (TCCM) Module (M8933) – The TCCM module contains tape control functions that are used by both PE and NRZI modes. The TCCM module generates clock waveforms used throughout the TM03 from a base clock frequency it receives from the selected slave transport.

When the control register is loaded with a function code requiring tape motion, the function code is decoded by the Massbus interface, and a FWD, REV, or RWND signal is applied to the slave bus. Soon after, a DRIVE SET pulse is generated by the Massbus interface to initialize TM03 circuitry. DRIVE SET pulse enters the TCCM module and produces SLAVE SET PLS and EMD (enable motion delay) – both of which are transmitted to the slave transport via the slave bus. SLAVE SET PLS initiates tape motion. EMD causes a preset to be applied on the read data lines of the slave bus by the slave transport and loads a motion delay counter in the TCCM with the preset. The counter is then upcounted to  $2^{14}$ , at which time ACCL is negated, indicating that the transport is assumed to be up to speed.

A similar motion delay is generated upon termination of a motion command, in which ACCL is asserted, and the TCCM issues STOP, causing the transport to cease tape motion.

<sup>\*</sup> M8934 and M8901-YB for 114.3 cm/second (45 inch/second) slaves (TE16). M8934-YA and M8901-YC for 190.5 cm/second (75 inch/second) slaves (TU45). M8934 and M8901-YD for 317.5 cm/second (125 inch/second) slaves (TU77).

During a read operation, read data is multiplexed from the slave bus read data lines through the TCCM module, to the data sync module (for PE) or tape control-NRZI module (for NRZI).

During a write operation, data is input to the TCCM module from the bit fiddler. The TCCM controls the timing for writing the LRCC and CRCC. It also contains a write multiplexer and write buffer, which:

- 1. Convert binary characters to PE mode

- 2. Multiplex 0s and 1s to write PE preambles and postambles

- 3. Multiplex the generated CRCC onto the write data path

- 4. Force IDB (identification burst) and TM (tape mark) character patterns onto the write data path.

Data in the TCCM write buffer is output via slave bus drivers on M8937 to the slave, along with REC. REC (record) is derived from WRT CLK, generated in the slave transport; its frequency depends on the mode (PE/NRZI) in which the write operation is performed.

#### 1.4 RELATED DOCUMENTS

Table 1-1 lists documents related to the TM03 formatter.

Table 1-1 Related Documents

| Title                                                         | Document<br>Number | Description                                                                                                                                      |

|---------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| TE16/TE10W/TE10N DECmagtape Transport Maintenance Manual      | EK-TE16-MM-001     | Theory and maintenance of TE16, TE10W, and TE10N tape transports                                                                                 |

| TE16/TE10W/TE10N<br>DECmagtape Transport<br>User Manual       | EK-TE16-OP-001     | Description, installation and maintenance of the TE16, TE10W, and TE10N tape transports as applicable to a user                                  |

| TU45A Magnetic Tape<br>Subsystem<br>Maintenance Manual        | EK-TU45A-MM-001    | Theory and maintenance of TU45A tape transport                                                                                                   |

| TU77 Magnetic Tape<br>Transport<br>Technical Manual, Volume 2 | EK-2TU77-TM-001    | Theory and maintenance of TU77 tape transport.                                                                                                   |

| TU77 Magnetic Tape<br>Transport User's Guide                  | EK-TU77-UG-001     | Description, installation, and operation of TU77 tape transport.                                                                                 |

| PDP-11 Peripherals Handbook                                   | _                  | Provides register descriptions for RH Massbus controllers                                                                                        |

| H740-D Power Supply<br>Maintenance Manual                     | DEC-11-H740A-A-D   | Theory and maintenance of H740-DA power supply. (The -DA model differs from the -D model by an ac connector used to power the TM03 cooling fan.) |

Table 1-1 Related Documents (Cont)

| Title                                                  | Document<br>Number | Description                                                                  |

|--------------------------------------------------------|--------------------|------------------------------------------------------------------------------|

| RH10 Massbus Controller<br>Maintenance Manual          | EK-RH10-MM-002     | Theory and maintenance of RH10 Massbus controller                            |

| TJU16 Magnetic Tape<br>Subsystem<br>Maintenance Manual | EK-TJU16-MM-002    | Theory and maintenance of RH11 Massbus controller                            |

| TWU16 Magnetic Tape<br>Subsystem<br>Maintenance Manual | EK-TWU16-MM-PRE    | Theory and maintenance of RH70 Massbus controller used with the PDP-11/70    |

| RH20 Massbus Controller<br>Unit Description            | EK-RH20-UD-001     | Description of RH20 Massbus controller                                       |

| TM03 Magnetic Tape<br>Formatter<br>Technical Manual    | EK-TM03-TM-001     | Description, installation, theory of operation, and maintenance of the TM03. |

| TM03 Formatter IPB                                     | EK-TM03-IP         | Illustrated parts breakdown of TM03.                                         |

| RH780 Massbus Controller<br>Technical Manual           | EK-RH780-TM-001    | Theory and maintenance of RH780 Massbus controller                           |

# 1.5 UNIT SPECIFICATIONS

Table 1-2 provides the TM03 unit specifications.

**Table 1-2** Unit Specifications

| Parameter                                    | Specification                                                     |

|----------------------------------------------|-------------------------------------------------------------------|

| Maximum transfer rate between TM03 and slave | 240K bytes/second                                                 |

| Error detection                              | CRC error detection in forward and reverse read (NRZI).           |

|                                              | Error correction of single track errors in NRZI and PE.           |

|                                              | Vertical parity error detection throughout TM03.                  |

| Maximum record length                        | 2 <sup>16</sup> bytes, PE or NRZI                                 |

| Minimum record length                        | 1 byte, PE; 13 bytes, NRZI (excluding tape mark)                  |

| Write lock                                   | Dependent upon write lock signal from slave                       |

| Environment                                  |                                                                   |

| Operating                                    | 10° to 40° C (50° to 104° F)                                      |

|                                              | 10 to 90 percent relative humidity                                |

|                                              | Wet bulb: 28° C (82° F) maximum  Dew point: 2° C (36° F), minimum |

| Non-operating                                | -40° to 66° C (-40° to 151° F)                                    |

| Tion operating                               | 0 to 95 percent relative humidity                                 |

Table 1-2 Unit Specifications (Cont)

|                            | Table 1-2 Unit Specifications (Cont)                                                                                       |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                  | Specification                                                                                                              |  |

| Altitude                   |                                                                                                                            |  |

| Operating<br>Non-operating | 2.4 km (8000 ft), maximum<br>9.1 km (30,000 ft), maximum                                                                   |  |

| Shock                      |                                                                                                                            |  |

| Operating                  | Shall withstand half-sine shock pulse of 10G, peak with 10 ± 3 ms duration                                                 |  |

| Non-operating              | Shall withstand half-sine shock pulse of 40G, peak with 30 ± 10 ms duration, applied perpendicular to each of six surfaces |  |

| Vibration                  |                                                                                                                            |  |

| Operating                  | Shall withstand vibration of 0.0508 mm (0.002 inch) double amplitude (maximum) in the frequency range of 5 to 50 Hz        |  |

| Non-operating              | Shall withstand vibration of 0.25G peak, in the frequence range of 50 to 500 Hz                                            |  |

| Power requirements         |                                                                                                                            |  |

| DC                         | None                                                                                                                       |  |

| AC                         | 90–135/180–270 Vac, 47–63 Hz<br>0.3 kW                                                                                     |  |

| Installation               | 16.83 cm (6-5/8 inch) panel height<br>48.3 cm (19 inch) rack mount                                                         |  |

| Shipping Weight            | 20.412 kg (45 lb) (uncrated)                                                                                               |  |

| Reliability                | Established by error rate of slave which is:                                                                               |  |

|                            | • Recoverable error rate*: less than one bit in 108 reads                                                                  |  |

|                            | • Non-recoverable error rate*: less than one bit in 10° reads                                                              |  |

<sup>\*</sup> A recoverable error is defined as a read error that is recovered within eight successive retries. (Retries on the same spot do not increase the soft error tally; i.e., a read error on block no. 1, record no. 1, that required three retries to recover is recorded as one soft read error.) If the data is not recovered after eight successive retries (nine successive incorrect data transfers), it is counted as one hard error.

# CHAPTER 2 PROGRAMMING INFORMATION

Chapter 2 contains programming information required by a user to program a system containing the TM03 formatter. The information provided pertains only to the TM03. Programming information pertaining to other system units can be found in the documentation applicable to these units. Table 1-1 lists the documents available on units that can interface with the TM03.

## 2.1 REGISTER FUNCTIONS AND FORMATS

The TM03 contains ten registers, some of which have been mentioned in Chapter 1. A summary of the TM03 registers is provided in Table 2-1. Any of the TM03 registers may be read to determine the status of the TM03/transport. Some of the registers may be written, thereby controlling functions and operating parameters.

The TM03 registers are read and written by performing "handshake" operations on the control bus of the Massbus. A register is loaded by the Massbus controller in the following manner.

- 1. The controller places the select code of the desired TM03 on the drive select lines.

- 2. The controller places a register select code on the register select lines.

- 3. It asserts CTOD (controller to drive).

- 4. It places data on the control lines.

- 5. The controller then asserts DEM.

The selected TM03 responds to DEM and CTOD asserted by loading the selected register with the data on the control lines. It then asserts TRA. The controller responds by negating DEM, which causes the TM03 to negate TRA; the write operation is thereby terminated.

A TM03 register is read in a similar manner except that CTOD is negated (step 3) and step 4 is eliminated. The selected TM03 responds to DEM asserted and CTOD negated by gating out the contents of the selected register onto the control lines. It then asserts TRA, which, when received by the controller, causes it to strobe in the data on the control lines and negate DEM. The TM03 responds by negating TRA, thereby terminating the operation.

The remainder of Paragraph 2.1 provides a more detailed description of the TM03 registers and their contents. It is primarily for reference, and may be skipped during a first reading.

Table 2-1 TM03 Registers

| Address<br>Code<br>(Octal) | Name                   | Туре       | Description                                                                                                                                                                |

|----------------------------|------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                         | Control 1 (CS1)        | Read/write | Contains the function code including the GO bit                                                                                                                            |

|                            |                        |            | 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00    DVA*                                                                                                                    |

| 01                         | Status (DS)            | Read only  | Contains all nonerror status information plus the error summary bit                                                                                                        |

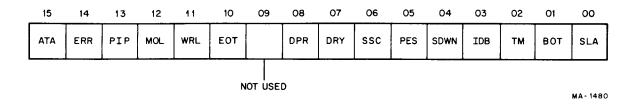

|                            |                        |            | 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00  ATA ERR PIP MOL WRL EOT DPR DRY SSC PES SDWN IDB TM BOT SLA  NOT USED                                                     |

| 02                         | Error (ER)             | Read only  | Contains all error indications                                                                                                                                             |

|                            |                        |            | 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00  COR/ UNS OPI DTE NEF CS/ ITM FCE NSG PEF/ UNC/ VPE DPAR FMT CPAR RMR ILR ILF  10-1276                                     |

| 03                         | Maintenance (MR)       | Read/write | Controls diagnostic functions                                                                                                                                              |

|                            |                        |            | 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00  MDF8 MDF7 MDF6 MDF5 MDF4 MDF3 MDF2 MDF1 MDF0 SWC2 MC MOP3 MOP2 MOP1 MOP0 MM  MAINTENANCE DATA FIELD SWC MODE OF OPERATION |

| 04                         | Attention Summary (AS) | Read/write | Indicates the attention active status of each TM03 (one bit/TM03)                                                                                                          |

|                            |                        |            | 15 08 07 06 05 04 03 02 01 00  ATA ATA ATA ATA ATA ATA ATA ATA ATA AT                                                                                                      |

| 05                         | Frame Count (FC)       | Read/write | For a write data transfer operation, contains the 2's complement of the number of tape characters to be transferred.                                                       |

|                            |                        |            | For a space operation, contains the 2's complement of the number of records to be spaced.                                                                                  |

|                            |                        |            | For a read data transfer operation, contains the 2's complement of the number of characters read.                                                                          |

|                            |                        |            | 15                                                                                                                                                                         |

Table 2-1 TM03 Registers (Cont)

| Address<br>Code<br>(Octal) | Name                 | Туре       | Description                                                                                                                                                                                                                                               |

|----------------------------|----------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06                         | Drive Type (DT)      | Read only  | Indicates the type of formatter and the type and status of the transport (e.g., existing formatter and transport with power applied)  15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00  NSA TAP MOH 7CH DRO SPR TMO2/ TMO3/ FORMATTER/TRANSPORT TYPE (0-8) |

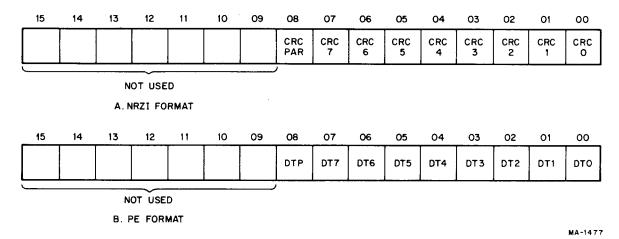

| 07                         | Check Character (CK) | Read only  | For an NRZI operation, contains the CRC error character  15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00  CRC CRC CRC CRC CRC CRC CRC CRC CRC CR                                                                                                          |

| ·                          | ·                    |            | For a PE operation, contains the dead-track indications    15   14   13   12   11   10   09   08   07   06   05   04   03   02   01   00                                                                                                                  |

| 10                         | Serial Number (SN)   | Read only  | Contains the last four digits of the transport serial number                                                                                                                                                                                              |

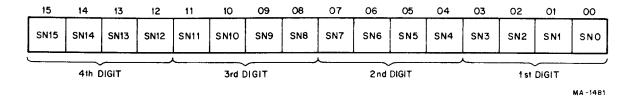

| 11                         | Tape Control (TC)    | Read/write | 15   14   13   12   11   10   09   08   07   06   05   04   03   02   01   00     SN15   SN14   SN13   SN12   SN11   SN10   SN9   SN8   SN7   SN6   SN5   SN4   SN3   SN2   SN1   SN0     41h DIGIT   3rd DIGIT   2rd DIGIT   1st DIGIT   10-1272         |

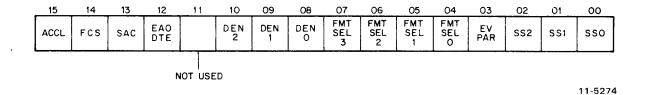

|                            | •                    | ,          | CODES  15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00  ACCL FCS SAC EAO DEN DEN DEN DEN ST FMT FMT FMT EV SS                                                                                                         |

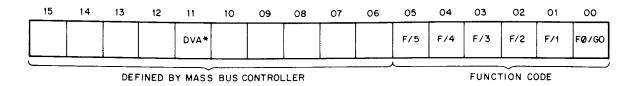

# 2.1.1 Control Register [(CS1) Register 00<sub>8</sub>]

The control register is a read/write register (Figure 2-1) which receives operational commands from the Massbus controller via the control bus. This register operates in conjunction with the tape control register to control the operation of the selected transport.

<sup>\*</sup> DRIVE AVAILABLE, HARDWIRED SET IN FORMATTER.

11-5274

Figure 2-1 Control Register Format

The control register is shared with the Massbus controller. Bits 00 through 05 and bit 11 are located in the TM03. The remaining nine bits are located in the controller.

The TM03/transport responds to the 14 function codes listed in Table 2-2. If the control register is loaded with a function code (with GO bit set) that does not agree with those listed in the table, an illegal function error (ILF) is generated. Thus, an ILF is generated for codes 05<sub>8</sub>, 13<sub>8</sub>, 15<sub>8</sub>, 17<sub>8</sub>, 23<sub>8</sub>, 35<sub>8</sub>, etc., but not for 00<sub>8</sub>, 02<sub>8</sub>, 04<sub>8</sub>, 06<sub>8</sub>, 10<sub>8</sub>, 12<sub>8</sub>, etc.

Table 2-2 Command Function Codes

| Function Code<br>F(0-5)<br>(octal) | Operation        | Description                                                                      |

|------------------------------------|------------------|----------------------------------------------------------------------------------|

| 01                                 | No Op            | Performs no operation. Clears GO bit in control register.                        |

| 03                                 | Rewind Off-Line* | 1. Initiates a rewind on selected transport and places it off-line.              |

|                                    |                  | 2. Clears GO bit.                                                                |

|                                    |                  | 3. Sets the following bits in the status register:                               |

|                                    |                  | Drive Ready (DRY) Slave Status Change (SSC) Attention Active (ATA)               |

| 07                                 | Rewind           | 1. Initiates a rewind to BOT marker on selected transport and clears the GO bit. |

|                                    |                  | 2. Sets DRY, PIP, and ATA bits in the status register during rewind.             |

|                                    |                  | 3. When BOT is sensed, sets SSC and clears PIP.                                  |

<sup>\*</sup>Requires manual intervention to return transport on-line.

Table 2-2 Command Function Codes (Cont)

| Function Code<br>F(0-5)<br>(octal) | Operation           | Description                                                                                                                                                                                                                                              |

|------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11                                 | Drive Clear         | Similar to initialize. Resets all TM03 and selected transport logic. Does not affect unselected transports.                                                                                                                                              |

| 21                                 | Read-In Preset      | Presets the tape control register (R11) to select slave 0, odd parity, PDP-10 core dump format, and 800 bits/inch NRZI; then causes slave 0 to rewind.                                                                                                   |

| 25                                 | Erase               | Erases approximately 7.6 cm (3 inches) of tape. Clears GO bit and sets ATA on termination.                                                                                                                                                               |

| 27                                 | Write Tape Mark     | Writes a special tape record on the selected transport. Clears GO bit and sets ATA bit on termination.                                                                                                                                                   |

|                                    | Space Forward       | Moves tape forward (toward EOT) on the selected transport over the number of records specified by the frame count register. Aborts space operation if TM or EOT is detected prior to specified frame count. Clears GO bit and sets ATA on termination.   |

| 33                                 | Space Reverse       | Moves tape in reverse (toward BOT) on the selected transport over the number of records specified by the frame count register. Aborts space operation if TM or BOT is detected prior to specified frame count Clears GO bit and sets ATA or termination. |

| 51                                 | Write Check Forward | Same as Read Forward.                                                                                                                                                                                                                                    |

| 57                                 | Write Check Reverse | Same as Read Reverse.                                                                                                                                                                                                                                    |

| 61                                 | Write Forward       | Writes forward one tape record on the selected transport. Record length is determined by frame count register. Clears GO bit on command termination.                                                                                                     |

| 71                                 | Read Forward        | Reads forward one tape record on the selected transport. Clears GO bit on command termination.                                                                                                                                                           |

| 77                                 | Read Reverse        | Reads reverse one tape record on the selected transport. Clears GO bit on command termination.                                                                                                                                                           |

# 2.1.2 Status Register [(DS) Register 01<sub>8</sub>]

The status register is a 16-bit, read-only register that stores the tape system status information. Figure 2-2 illustrates the status register format and Table 2-3 defines the bit positions. Although the status register multiplexer is located in the TM03, inputs to this multiplexer may be generated either by a selected transport, any transport, or the TM03 logic itself. Because of this fact, each bit position in Table 2-3 is identified by one or more of the following designators to indicate the origin of the input signal.

(SS) = Selected transport

(S) = Any transport

(M) = TM03 logic

Figure 2-2 Status Register Format

Table 2-3 Status Register Bit Positions

| Bit Position | Name                       | Description                                                                                                                               |

|--------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 00 (SS)      | Slave Attention (SLA)      | Indicates that a selected transport has come on-line.                                                                                     |

| 01 (SS)      | Beginning of Tape (BOT)    | Indicates that a selected transport has detected the BOT marker.                                                                          |

| 02 (M)       | Tape Mark (TM)             | Indicates that a tape mark has been detected. Remains asserted until the next tape motion is initiated.                                   |

| 03 (M)       | Identification Burst (IDB) | Indicates that a phase-encoded (PE) identification burst has been detected. Asserted until a subsequent tape motion command is initiated. |

| 04 (SS)      | Settle Down (SDWN)         | Indicates that tape motion on the selected transport is stopping.                                                                         |

| 05 (SS)      | Phase-Encoded Status (PES) | Indicates that the selected transport is configured for PE operation. Is negated during NRZI operation.                                   |

| 06 (S)       | Slave Status Change (SSC)  | Indicates that any transport has just gone on-line or off-line, or has completed a rewind operation.                                      |

Table 2-3 Status Register Bit Positions (Cont)

| Bit Position | Name                          | Description                                                                                                                                                                         |

|--------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07 (M)       | Drive Ready (DRY)             | Indicates that both the TM03 and the selected transport are ready to accept a command.                                                                                              |

| 08 (M)       | Drive Present (DPR)           | Hard-wired set.                                                                                                                                                                     |

| 09           | Not used                      |                                                                                                                                                                                     |

| 10 (SS)      | End of Tape (EOT)             | Indicates that the selected transport has detected the EOT marker during forward tape motion. Is negated when the EOT marker is detected during reverse tape motion.                |

| 11 (SS)      | Write Lock (WRL)              | Indicates that the selected transport is write protected.                                                                                                                           |

| 12 (SS)      | Medium On-Line (MOL)          | Indicates that the selected transport has tape loaded and is on-line.                                                                                                               |

| 13 (M/SS)    | Positioning in Progress (PIP) | Indicates that the selected transport is performing a tape motion operation. This bit is asserted by the TM03 (M) during a space or by the selected transport (SS) during a rewind. |

| 14 (M)       | Composite Error (ERR)         | Indicates that an error condition has occurred. Is asserted whenever any bit in the error register is set.                                                                          |

| 15 (M)       | Attention Active (ATA)        | Is asserted whenever the ATTN interface signal is generated. Indicates one of the following:                                                                                        |

|              |                               | 1. The TM03 and the selected transport require servicing.                                                                                                                           |

|              |                               | 2. The TM03 and the selected transport have become ready after a nontransfer operation.                                                                                             |

|              |                               | 3. A transport status change has occurred.                                                                                                                                          |

# 2.1.3 Error Register [(ER) Register 02<sub>8</sub>]

There are 16 different error conditions that can be detected in the TM03/transport system. The error register is a 16-bit, read-only register that stores all of the tape system error indications.

TM03/transport errors are categorized as Class A and Class B. A Class B error will terminate an inprogress data transfer; a Class A error will not. However, the Massbus controller is notified of any error during a data transfer by the immediate assertion of exception (EXC) on the Massbus. If the TM03/transport is not performing any operation, or is performing a rewind (i.e., the GO bit is clear), the controller is immediately notified of an error condition by the assertion of ATTN on the Massbus.

Figure 2-3 illustrates the error register format and Table 2-4 lists the error bit indicators.

| 15          | 14  | 13  | 12  | 11  | 10         | 09  | 08  | 07          | 06          | 05   | 04  | 03   | 02  | 01  | 00  |

|-------------|-----|-----|-----|-----|------------|-----|-----|-------------|-------------|------|-----|------|-----|-----|-----|

| COR/<br>CRC | UNS | OPI | DTE | NEF | CS/<br>ITM | FCE | NSG | PEF/<br>LRC | INC/<br>VPE | DPAR | FMT | CPAR | RMR | ILR | ILF |

MA -1478

Figure 2-3 Error Register Format

Table 2-4 Error Register Bit Indicators

| Bit<br>Position | Name                                  | Description                                                                                                                                                                | Туре    |

|-----------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 00              | Illegal Function (ILF)                | Indicates that an illegal function code has been transmitted.                                                                                                              | Class B |

| 01              | Illegal Register (ILR)                | Indicates that a read or write from a nonexistent register is attempted.                                                                                                   | Class A |

| 02              | Register Modification<br>Refuse (RMR) | Indicates that during a transport operation (GO = 1), a write into one of the registers is attempted. (Does not apply for the maintenance or attention summary registers.) | Class A |

| 03              | Control Bus<br>Parity (CPAR)          | Indicates that incorrect control bus parity is detected.                                                                                                                   | Class A |

| 04              | Format (FMT)                          | Indicates that a data transfer with an incorrect format code is attempted. When the M8915 bit fiddler is used, a FMT error could also indicate:                            | Class B |

|                 |                                       | <ol> <li>Microcode parity error</li> <li>M8915 data parity error</li> <li>Illegal microcode instruction</li> </ol>                                                         |         |

| 05              | Data Bus Parity<br>Error (DPAR)       | Indicates that incorrect data bus parity has occurred.                                                                                                                     | Class A |

Table 2-4 Error Register Bit Indicators (Cont)

| Bit<br>Position | Name                                                 | Description                                                                                                                                                                                            | Туре    |

|-----------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 06              | Incorrectable Data Error or Vertical                 | During a PE read operation, indicates that one of the following has occurred:                                                                                                                          | Class A |

|                 | Parity Error<br>(INC/VPE)                            | <ol> <li>Multiple dead tracks</li> <li>Dead tracks without parity errors</li> <li>Parity errors without dead tracks</li> <li>Skew overflow</li> <li>Parity error in bit fiddler.</li> </ol>            |         |

|                 |                                                      | During an NRZI read operation, indicates that a vertical parity error has occurred or that data has occurred after the skew delay is over.                                                             |         |

| 07              | Format Error or LRC<br>Error (PEF/LRC)               | During a PE read operation, indicates than an incorrect preamble or postamble is detected.                                                                                                             | Class A |

|                 |                                                      | During an NRZI write operation, indicates that the LRCC read off the tape does not match the LRCC computed from the characters read off the tape.                                                      |         |

|                 | Nonstandard<br>Gap (NSG)                             | Indicates that a tape character is detected during the first half of the end-of-record gap while a write operation is in progress. Never set during a read operation.                                  | Class A |

| 09              | Frame Count<br>Error (FCE)                           | Indicates that a space operation has terminated and the frame counter is not cleared. Also asserted when the Massbus controller fails to negate RUN when the TM03 asserts EBL.                         | Class A |

| 10              | Correctable Skew or<br>Illegal Tape Mark<br>(CS/ITM) | During a PE read operation, indicates that excessive but correctable skew is detected. (This condition is only a warning and does not indicate bad data.)  During an NRZI read, indicates that charac- | Class A |

|                 |                                                      | ters not legally a tape mark have been read<br>and recognized as a tape mark (e.g., such as a<br>record less than the 10-character minimum).                                                           |         |

| 11              | Nonexecutable<br>Function (NEF)                      | Indicates one of the following:                                                                                                                                                                        | Class B |

|                 | , ,                                                  | 1. A write operation is attempted on a write-<br>protected transport.                                                                                                                                  |         |

|                 |                                                      | 2. A space reverse, read reverse, or write check reverse is attempted when the tape is at BOT.                                                                                                         |         |

|                 |                                                      | 3. The DEN2 bit in the tape control register does not agree with the PES status bit during a write operation.                                                                                          |         |

Table 2-4 Error Register Bit Indicators (Cont)

| Bit<br>Position | Name                          | Description                                                                                                                                                                                                                              | Туре    |

|-----------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                 |                               | 4. A space or write operation is attempted when FCS = 0 in the tape control register.                                                                                                                                                    |         |

|                 |                               | 5. A write operation is attempted with DEN2 = 0 in the tape control register (NRZI mode) and the 2's complement of a number less than 13 <sub>8</sub> is in the frame count register.                                                    |         |

|                 |                               | 6. The type of phase-locked loop modules (M8901-YB, YC, or YD) do not agree with the type of transport as specified by the drive type register. This indicates that the TM03 and the transport are not operating at the same tape speed. |         |

| 12              | Drive Timing                  | Indicates one of the following:                                                                                                                                                                                                          | Class B |

|                 | Error (DTE)                   | <ol> <li>During a write operation, WCLK was not<br/>received from the Massbus controller in<br/>time to provide a valid tape character.</li> </ol>                                                                                       |         |

|                 |                               | <ol> <li>A data transfer (read/write) was attempted<br/>when the data bus of the Massbus was<br/>already occupied.</li> </ol>                                                                                                            |         |

| 13              | Operation<br>Incomplete (OPI) | During a read/write or space operation, indicates that an end of record has not been detected within 7 seconds from command initiation. Also set during a read reverse or a space reverse if BOT is detected.                            | Class B |

| 14              | Unsafe (UNS)                  | Indicates one of the following:                                                                                                                                                                                                          | Class B |

|                 |                               | <ol> <li>A program-controlled operation is<br/>attempted on a selected transport that is<br/>not on-line.</li> </ol>                                                                                                                     |         |

|                 |                               | <ol> <li>An imminent power failure is detected (AC LO).</li> </ol>                                                                                                                                                                       |         |

|                 | Correctable Data Error or CRC | During a PE read operation, indicates that a single dead track has occurred.                                                                                                                                                             | Class A |

|                 | Error (COR/CRC)               | During an NRZI operation, indicates that the CRCC read off the tape does not match the CRCC computed from the data read off the tape.                                                                                                    |         |

#### 2.1.4 Maintenance Register [(MR) Register 03<sub>8</sub>]

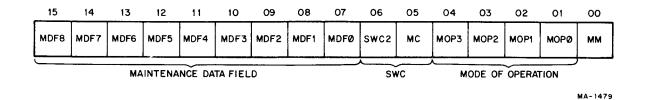

The maintenance register (M8905-YB) is a 16-bit, read/write register (Figure 2-4) that allows complete diagnostic testing of the TM03 data paths and error detection circuitry. The maintenance register can configure the data paths into five wraparound loops, each loop testing certain TM03 circuits. The maintenance register data field is part of these loops, and is used to read or write test data into the TM03. Table 2-5 briefly describes the bits of the maintenance register.

Figure 2-4 Maintenance Register Format

Table 2-5 Maintenance Register Bit Positions

| Bit Position | Name                                   | Description                                                                                                                                                  |

|--------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00           | Maintenance Mode (MM)                  | When set, configures the TM03 for maintenance mode operation.                                                                                                |

| · 01–04      | Maintenance Operation<br>Code (MOP0-3) | Controls command execution during the maintenance mode. (MM and MOP function together to alter normal command execution during maintenance mode operation.)  |

| 05           | Maintenance Clock (MC)                 | Controls data sequencing through the TM03 data path in maintenance mode.                                                                                     |

| 06           | Tape Speed Clock (SWC2)                | A clock signal generated by the selected slave. Frequency depends on the tape speed of the selected slave. Used to monitor maintenance mode read operations. |

| 07–15        | Maintenance Data<br>Field (MDF0-8)     | Buffers the data generated during wrap-<br>around operations.  At the end of normal NRZI transfers, con-<br>tains the LRC of the last record.                |

# 2.1.5 Attention Summary Register [(AS) Register 04<sub>8</sub>]

The attention summary register (M8909-YA) is a read/write "pseudo-register" that consists of from one to eight bits, depending on the number of drives (TM03s) on the Massbus. The term "pseudo-register" refers to the fact that only one register bit position is physically contained in each TM03. This bit position reflects the state of the ATA status bit for that TM03. Hence, bit position 0 of the attention summary register is generated by the ATA bit of TM03 No. 0; bit position 1 is generated by the ATA bit of TM03 No. 1, and so on to bit 7. Bits 8 through 15 are not used.

Unlike the other TM03 registers, the attention summary register is directly selected by the controller without first addressing a particular TM03. Thus, for a single attention summary register read operation, every TM03 in the system responds by placing the state of its ATA bit in the appropriate bit position on the control bus and disabling its remaining 15 control bus transmitters. This control bus configuration appears as a single register output which collectively informs the controller of all TM03s that require attention (i.e., ATA = 1). The controller can then selectively examine the error or status registers of each of the affected TM03s to determine the cause of the individual attention conditions.

The controller can also write into the attention summary register; however, the significance of the bits being written is unusual. Writing a 1 into a bit position resets the ATA bit in the TM03 assigned to that bit position; however, writing a 0 has no effect. This unique writing scheme allows the controller to reset, after inspection, all summary bits that were set, without accidentally resetting those bits that may have become set in the meantime. The following table illustrates the effects of writing into an attention summary bit position.

| ATA Bit<br>Before | Summary Bit<br>Written | ATA Bit<br>After |  |  |

|-------------------|------------------------|------------------|--|--|

| 0                 | 0                      | 0                |  |  |

| 1                 | 0                      | 1                |  |  |

| 0                 | 1                      | 0                |  |  |

| 1                 | 1                      | 0                |  |  |

# 2.1.6 Frame Count Register [(FC) Register 05<sub>8</sub>]

The frame count register (M8909-YA) is a 16-bit, read/write register that counts tape events. During a data transfer operation (read/write), this register is incremented each time a tape character is transferred to or from the tape. However, during a space operation, this register is incremented each time a record is detected. The register output may be read by the controller at any time, but the controller can only write into this register when the transport is not performing a space operation or data transfer (GO negated).

For a write operation, the frame count register is loaded, prior to write initiation, with the 2's complement of the number of tape characters to be written. During the writing process, the frame count register is incremented each time a tape character is recorded. Normal write data transfer termination is accomplished when the frame count register overflows to zero. For a space operation, the frame count register functions similarly to a write, except it is loaded with the 2's complement of the number of records to be spaced and is then incremented each time a record is detected. Space termination is accomplished when the register overflows to zero. For a read operation, this register is automatically reset prior to read initiation. The register is then incremented each time a tape character is read. Thus, at the end of the read operation, the frame count register contains a count of the number of characters read.

# 2.1.7 Drive Type Register [(DT) Register 06<sub>8</sub>]

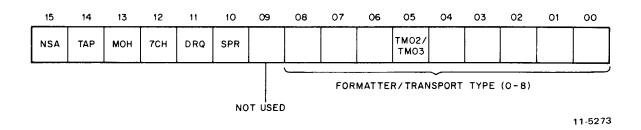

The drive type register (M8933) is a 16-bit, read-only register, the content of which identifies the particular type of formatter and transport being used. When a read from the drive type register is performed, the register output is applied to the appropriate multiplexer bit positions. Bits 0 through 8 (DT0-8) of the drive type register identify the type and status of the selected formatter and transport. If a nonexistent transport is selected or if the selected transport is not powered up, DT0-8 will contain 050<sub>8</sub>. If the selected transport is powered up, the drive type code will be 05X<sub>8</sub>, where X represents bits DT0, DT1, and DT2 and indicates the type of slave. Bits DT0 through DT8 are coded as shown below for the TM03. Neither INIT nor drive clear can affect bits DT0-8.

| DT8 | DT7 | DT6 | DT5* | DT4 | DT3 | DT2 | DT1 | DT0 |                                              |

|-----|-----|-----|------|-----|-----|-----|-----|-----|----------------------------------------------|

| 0   |     |     |      |     |     |     |     |     | = Unselected slave                           |

| 0   | 0   | 0   | 1    | 0   | 1   | 0   | 0   | 1   | = 114.3 cm/second (45 in/s), slave selected  |

| 0   | 0   | 0   | 1    | 0   | 1   | 0   | 1   | 0   | = 190.5 cm/second (75 in/s), slave selected  |

| 0   | 0   | 0   | 1    | 0   | 1   | 1   | 0   | 0   | = 317.5 cm/second (125 in/s), slave selected |

<sup>\*</sup>DT5 will indicate the type of formatter being used.

DT5 = 0 = TM02

DT5 = 1 = TM03

Figure 2-5 illustrates the drive type register format and Table 2-6 briefly describes each bit position.

Figure 2-5 Drive Type Register Format

Table 2-6 Drive Type Register Bit Positions

| Bit Position | Name                         | Description                                                                                                              |

|--------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 00-08        | Drive Type (DT0-8)           | Specifies the type of formatter and transport.                                                                           |

| 09           | _                            | Spare bit.                                                                                                               |

| 10           | Slave Present (SPR)          | Asserted when a transport is powered up and has been assigned the selection code contained in the tape control register. |

| 11           | Drive Request Required (DRQ) | Always negated to indicate that the device is a single-port unit.                                                        |

| 12           | 7-Channel (7CH)              | Always negated. The TM03 does not interface with 7-channel transports.                                                   |

| 13           | Moving Head (MOH)            | Always negated to indicate that the device is not a moving head unit.                                                    |

| 14           | Tape Drive (TAP)             | Always asserted to indicate that the device is a tape transport.                                                         |

| 15           | Not Sector Addressed (NSA)   | Always asserted to indicate that the device is not sector addressable.                                                   |

# 2.1.8 Check Character Register [(CK) Register 07<sub>8</sub>]