BASIC-11 Laboratory Extensions User's Guide

Order No. DEC-11-LBEPA-A-D

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

Digital Equipment Corporation assumes no responsibility for the use or reliability of its software on equipment that is not supplied by DIGITAL.

Copyright C 1976 by Digital Equipment Corporation

The postage prepaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist us in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

## CONTENTS

|          |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                                            |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| PREFACE  |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | v                                                                                                               |

| CHAPTER  | 1                                                                                                                                                                                                                                 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-1                                                                                                             |

| CHAPTER  | 2                                                                                                                                                                                                                                 | LABORATORY PERIPHERAL SYSTEM SUPPORT (LPS11, AR11, and DR11-K)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-1                                                                                                             |

|          | 2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.5<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.5<br>2.6.2<br>2.6.2<br>2.6.3<br>2.6.4<br>2.6.5<br>2.7<br>2.7.1<br>2.7.2<br>2.7.3<br>2.7.6<br>2.8 | GENERAL FEATURES  DESCRIPTION OF ROUTINES  MODULE LPSO (REQUIRED MODULE)  Defining the Buffer (USE)  Allowing Access to a Buffer (ACC)  Returning Data from a Buffer (RDB)  MODULE LPS1 (A/D CONVERSION AND  NUMERIC READOUT)  Analog to Digital Conversion (ADC)  Real-Time Sampling (RTS)  Display on the Light Emitting Diodes (LED)  Returning A/D Data from Buffer (CVSG)  MODULE LPS2 (REAL-TIME CLOCK)  Setting the Clock Rate (SETR)  Setting the Clock to Rate and Time (SETC)  Histograms - Timed Schmitt Trigger (HIST)  Delaying Program Execution (WAIT)  Returning Current Software Clock Tick Value (RTIM)  MODULE LPS3 (DIGITAL I/O)  Reading the Digital Input Register (DIR)  Writing to the Digital Output Register (DOR)  Digital Readout Sampling (DRS)  Relay Control (REL)  Read/Write Data From/Into Register (IPK)  MODULE LPS4 (DISPLAY)  Defining the Display Buffer (CLRD)  Putting Data into Display Buffer (PUTD)  Background Display Routine (DIS)  Display Buffer (FSH)  Displaying X,Y Data (DXY)  Flashing X,Y Data (FXY)  HARDWARE REQUIRED FOR LPS COMMANDS | 2-1 2-3 2-3 2-5 2-6 2-7 2-7 2-8 2-11 2-12 2-12 2-14 2-15 2-16 2-17 2-17 2-19 2-21 2-21 2-21 2-21 2-21 2-21 2-21 |

| APPENDIX | A                                                                                                                                                                                                                                 | COMMAND SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A-1                                                                                                             |

| APPENDIX | В                                                                                                                                                                                                                                 | BUILDING LOAD MODULES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B-1                                                                                                             |

|          | B.1<br>B.1.1<br>B.2<br>B.2.1<br>B.3<br>B.3.1                                                                                                                                                                                      | BASIC/RT-11 LPS Support BASIC/CAPS-11 LPS Support BASIC/PTS-11 LPS Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | B-1<br>B-1<br>B-11<br>B-11<br>B-23<br>B-23                                                                      |

## CONTENTS (Cont.)

| APPENDI | ХС                       | ERROR MESSAGES                                                                                               | C-1                          |

|---------|--------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------|

| GLOSSAR | Y                        |                                                                                                              | Glossary-1                   |

| INDEX   |                          |                                                                                                              | Index-1                      |

|         |                          |                                                                                                              |                              |

|         |                          | TABLES                                                                                                       |                              |

| TABLE   | 2-1<br>2-2<br>2-3<br>2-4 | Mode Options in RTS Sampling<br>Mode for Values of m<br>Selecting the Clock Rate<br>Selecting the Clock Mode | 2-10<br>2-10<br>2-13<br>2-14 |

#### PREFACE

This manual describes the extensions for use with the BASIC/RT-11, BASIC/PTS-11, and BASIC/CAPS-11 systems. The extensions enable you to utilize PDP-11 lab peripherals such as LPS11, AR11, and DR11-K. Unless stated otherwise, the descriptions of all routines in this manual apply to the systems mentioned above.

The routines for these peripherals are provided in library form that can be linked with a user program. The user should have a programming knowledge of BASIC and some understanding of the peripherals.

The following table describes the documentation conventions used in this manual.

|                                                                        | •                                                                                                  |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| <lf></lf>                                                              | Line feed                                                                                          |

| <cr></cr>                                                              | Carriage return                                                                                    |

| or CTRL                                                                | Used with special system control characters. Depress CTRL key while striking designated character. |

| \$                                                                     | Altmode                                                                                            |

| Square Brackets [ ]                                                    | Optional arguments are enclosed.                                                                   |

| Lower case letter or lower case letter followed by a digit (a,b,x0,y1) | Value to be supplied by user. May be any valid arithmetic expression.                              |

| Lower case letter followed by a dollar sign (a\$,x\$)                  | String to be supplied by user. May be string constant (enclosed in quotes) or variable (A\$).      |

| Upper case letter (A,B,X,Y)                                            | Numeric variable whose value will be determined by call or an array name.                          |

| Y axis                                                                 | The vertical axis.                                                                                 |

| X axis                                                                 | The horizontal axis.                                                                               |

Meaning

The following manuals are necessary references for this manual:

RT-11 System Reference Manual DEC-11-ORUGA-C-D

Convention

BASIC-11 Language Reference Manual DEC-11-LIBBA-B-D

BASIC/PTS User's Manual DEC-11-LPTBA-A-D

BASIC/CAPS-11 User's Manual DEC-11-LIBCA-A-D

LPS11 User's Guide DEC-11-HLPGA-C-D

ARll User's Guide DEC-11-HARUG

DR11-K Interface User's Guide and Maintenance Manual  ${\tt EK-DR11K-MM-001}$

#### CHAPTER 1

#### INTRODUCTION

BASIC Extensions support the RT-11, CAPS-11, and PTS-11 systems, and the following hardware:

LPS11 Laboratory Peripheral System AR11 Analog Real-Time·Interface DR11-K Digital Input/Output Interface

The Laboratory Peripheral System (LPS) support can utilize LPS11, AR11 and DR11-K to sample and display data from analog to digital converters, digital input/output, or external events. LPS support contains 23 routines to control LPS11, AR11 and DR11-K. These 23 routines are divided into five categories according to their function. Each category is supplied as a module. The first module, LPS0, is the main module which contains all necessary support routines for using the other four modules. This module is required but the other four are optional.

The support for the peripherals consists of a library of routines that can be controlled by a user program through a CALL statement. The format of the CALL statement is:

CALL "name" (argument list)

Under BASIC/CAPS-11, the routines can also be called by a statement of the form:

name(argument list)

The function and limitation of each routine is described in detail in the following chapter.

| • |  |   |  |   |  |

|---|--|---|--|---|--|

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  | • |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  | · |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

|   |  |   |  |   |  |

#### CHAPTER 2

## LABORATORY PERIPHERAL SYSTEM SUPPORT (LPS11, AR11, DR11-K)

### 2.1 GENERAL FEATURES

Laboratory Peripheral System support for BASIC-11 allows a user to utilize the LPS hardware which includes LPS11, AR11 and up to 16 DR11-K. LPS support enables the sampling and displaying in a real-time environment of a variety of data from analog to digital converters, digital input/output, and external events. Sampling is controlled by crystal clocks and/or Schmitt triggers; it is possible to specify such parameters as sampling rate and response time thus allowing maximum flexibility.

#### NOTE

In a multiple DR11-K system, there must be a difference of 10(octal) between each unit in the interrupt and vector address. The status register address decreases by 10(octal) while the vector address increases by 10(octal).

All LPS routines are issued by the BASIC CALL statement allowing experienced PDP-11 assembly language programmers to easily include or modify the routines to meet particular (or special) requirements.

#### 2.2 DESCRIPTION OF ROUTINES

The BASIC Extensions contain 23 routines to control the following options on the LPS11 hardware:

LPSAD-12 12-bit ADC, sample and hold, 8-channel multiplexer, and LED (light emitting diodes) 6-digit programmable decimal readout display.

LPSAD-NP Direct memory access (DMA) option for the LPSAD-12 ADC.

LPSAG Four differential preamplifiers with +or-lV input.

Maximum of 4 LPSAGs per LPS11-S system.

LPSAG-VG Four independently selectable multigain differential preamplifiers.

LPSAM 8-channel expansion multiplexer.

LPSSH Second sample and hold for a dual sample and hold configuration.

LPSKW Programmable real-time clock and two Schmitt triggers.

LPSVC Display control including two 12-bit DACS. This

controller is capable of handling Digital's VR14 and VR20 scopes.

LPSDR

16-bit buffered digital I/O with drive capabilities and two programmable normally open (n.o.) relays. LPSDR cannot be used if DR11-K is used.

The 23 routines are divided into 5 categories according to their function. Each category is supplied as a separate module.

The following list is a summary of the routines available for controlling LPS hardware and a brief description of each:

#### MODULE LPSO (This module is always required.)

| USE | Defines | array(s) | to | be | used | for | storage | οf |

|-----|---------|----------|----|----|------|-----|---------|----|

|     | data.   |          |    |    |      |     |         |    |

ACC Allows access to an entire array.

RDB Returns the next data point from a specified buffer.

#### MODULE LPS1 (ANALOG TO DIGITAL CONVERSION)

| ADC | Initiates  | an A/D  | conversi  | on on    | a specified |  |

|-----|------------|---------|-----------|----------|-------------|--|

|     | channel ar | nd retu | rns the r | esult to | the user.   |  |

RTS Performs real-time buffered/clocked sampling

of the A/D.

LED Displays a numeric value on the Light

Emitting Diodes.

CVSG Returns the next data value and gain in two separate variables.

#### MODULE LPS2 (REAL-TIME CLOCK)

| SETR | Sets  | clock | running | at | а | designated | rate | and |

|------|-------|-------|---------|----|---|------------|------|-----|

|      | a bom |       |         |    |   |            |      |     |

SETC Sets clock running at a designated rate and initiates some action after a specified number of seconds have elapsed.

HIST Performs histogram sampling using a timed Schmitt trigger.

WAIT Waits for a specified event to occur.

RTIM Returns the value of the internal software clock counter.

#### MODULE LPS3 (DIGITAL I/O)

DIR Reads Digital Input register.

DOR Writes Digital Output register.

DRS Performs sampling of the Digital Input register.

REL Closes or opens one of two relays.

IPK Reads a value from a register or writes a value into a register.

#### MODULE LPS4 (DISPLAY)

CLRD Defines display buffer and optionally clear or scale the data in it.

PUTD Puts data into data buffer.

| DIS | Displays data with incrementing x and              |

|-----|----------------------------------------------------|

|     | variable y whenever BASIC is waiting for I/O.      |

| FSH | Displays a single complete sweep of data with      |

|     | incrementing x and variable y.                     |

| DXY | Displays data with variable $\hat{x}$ and y values |

|     | whenever BASIC is waiting for I/O.                 |

| FXY | Displays a single complete sweep of data with      |

|     | variable x and v values.                           |

Module LPSO is the main module and contains not only the USE, ACC, and RDB routines, but also all necessary support routines for the other modules. Therefore, it must be included, although the other modules are optional.

Data buffers used by the LPS routines differ from the normal arrays in BASIC in that they use only one word of storage per data element rather than two. This is because all LPS data is no larger than 2\*\*16-1 and can be stored as unsigned 16-bit data. All data buffers must be defined by a USE routine before they are accessed by any other LPS routines. The USE routine allows the user to partition and make equivalent arrays for ease in displaying and manipulating common data. All data buffers defined in the USE routine are circular with internal pointers keeping track of where data is to be placed next and/or retrieved.

#### 2.3 MODULE LPSO (REQUIRED MODULE)

## 2.3.1 Defining the Buffer (USE)

USE

The USE routine defines buffer areas for use with the ACC, RDB, RTS, HIST, DRS, CLRD, PUTD, DIS, FSH, DXY and FXY routines. This routine sets up internal pointers allowing circular buffering and data overrun and/or nonexistent data checking. A maximum of five buffers may be specified, all of which must be given in a single USE statement. All areas defined in the USE statement must have been previously dimensioned in a DIM statement.

The format of the USE call is:

CALL "USE" (A[(i)], [B[(j)], ..., C[(f)]])

where

A,B,C are the names of previously dimensioned array(s). May be 5 different arrays or array names may be repeated.

i,j,f represents a valid subscript for the array or 0

which indicates the entire array.

The USE routine defines buffer areas required for storage of data. These areas may be a partitioned array which can be made equivalent to one large array. The following examples illustrate all aspects of the USE routine. Note that the size of an area defined in a DIM statement is one half that desired. This is because BASIC uses two words to store data whereas the LPS data is stored in one word.

#### Example:

Define areas A, B, and C to have 100, 200, and 300 data points respectively.

10 DIM A(50),B(100),C(150) 20 CALL "USE"(A,B,C)

#### Example:

Define area A to consist of three parts, the first having 10 data points and the second and third having 20 each. Then define a final area having access to all of the array A (including the zero subscript element).

#### NOTE

Read the USE statement from left to right establishing the separate areas based on previously defined members of the same array. Only when the starting address of the next array is less than the previous one will entire access to the array be allowed by the following array.

The subscripts in the declaration are used to define pseudo partition names which can be used in other LPS statements which require arrays.

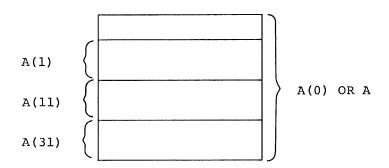

10 DIM A(25) 20 CALL "USE"(A(1),A(11),A(31),A)

In this example, each declaration of the array A has a unique description. A, which is equivalent to A(0), is different than A(1), A(11), and A(31). The following figure illustrates the partitioning of the array A due to the preceding example.

In the example, the partitioning occurs as follows: A(1) defines a buffer array starting at position A(1) in the array A and ending at the last position in the array. Since A(11) is declared immediately following it, the end of the array for A(1) is redefined to be one less than the A(11) position. At this point, A(1) goes from the 1st position in the array to the 10th, and A(11) goes from the 11th

position in the array to the 50th. When A(31) is declared immediately following A(11), A(11) is redefined to go from the 11th position in the array to the 30th and A(31) goes from the 31st position to the Now the partitioned array consists of three parts. The first part is called A(1) and is 10 locations in size. The second part is called A(ll) and is 20 locations in size. The third part is called A(31) and is also 20 locations in size. The final declaration in the example is A or A(0) (both are equivalent), which allows access to the entire array A. This happens because the position in the array A of A(0) is less than the last declaration in the USE statement, i.e., A(31), and a new partitioning is started. This new partitioning begins at A(0) and proceeds until the end of the array A. The rules to continue from this point are the same as previously discussed and further partitioning could be defined if necessary. Note that every declaration in the USE statement must be unique, i.e., a statement of the form USE(A,A(0)) results in the first array A having an area of zero length. Since the second array is not unique in name, any reference to it later by other LPS statements actually refers to the array A and not A(0). Since A has zero length, the buffer declaration is useless.

#### 2.3.2 Allowing Access to a Buffer (ACC)

ACC

The ACC routine allows full access to the specified array by the RDB routine. The form of the call is:

CALL "ACC"(A[(i)])

where

A[(i)] is a buffer previously declared in a call to the USE routine.

A call to ACC resets all buffer pointers of the array A to allow full access to it by the RDB and PUTD routines. The PUTD pointer is placed at the end of the array and the RDB pointer is placed at the beginning. Since the PUTD pointer is placed at the end of the array, the buffer is considered full.

#### Example:

Allow full access to the array H and the buffer area of array A.

```

10 DIM A(25), H(20)

20 CALL "USE"(A(1), A(11), A(31), A, H)

30 ....

40 ....

...

100 CALL "ACC"(H)

110 CALL "ACC"(A(11))

120 ....

130 ....

```

#### 2.3.3 Returning Data from a Buffer (RDB)

## **RDB**

A call to the RDB routine returns the next data value from the specified buffer in the target variable. The value returned from RDB contains the data value with the gain in the most significant digits. The returned data is formatted. The form of the call is:

CALL "RDB" (A[(i)],B)

where

A[(i)] is a buffer previously defined in a call to the USE routine.

B is the target variable.

A call to the RDB routine returns values in B of 65535 to 0 for good data. A -1 will be returned if the data is bad (defined as software data overrun). A -2 will be returned if there is no data. A -3 will be returned if a hardware data overrun occurs.

A ring buffer is the specified buffer used by the RDB, RTS, HIST, PUTD, and DRS routines. Data is withdrawn from the ring buffer by the RDB routine but inserted into the ring buffer by the RTS, HIST, PUTD, or DRS routine. Two pointers which are invisible to the users point to the last data added and the next to be withdrawn.

If either pointer passes beyond the buffer, it is reset to the beginning of the buffer. If a RDB routine is executed when no data is available, the pointer is not advanced.

If a software data overrun occurs (that is, when there is no room in the ring buffer for data from the RTS, HIST, PUTD or DRS routine), then all subsequent calls on the RDB routine will return a -1. This will occur if the ring buffer is not large enough to contain all the data or the data is not removed from the ring buffer as fast as it is added.

When the referenced buffer contains analog sampling data (RTS function), the values returned in B are in the range 0 to 4095 for the LPS11 and 0 to 1023 for the AR11, with the gain in the most significant bits.

When the referenced buffer contains a clocked histogram sampling (HIST function), the values returned in B are in the range 0 to 65535. These values are either the number of ticks accumulated or the number remaining depending on the clock mode.

When the referenced buffer refers to digital I/O data (DRS function), a value between 0 to 65535 is returned in B from the next position in the specified buffer.

#### Example:

Assume that the array X has 100 data values previously entered by an RTS routine. Print out the data making sure that data overrun did not occur and that 100 data points were indeed taken.

10 FOR I=1 TO 100

20 CALL "RDB"(X.Z)

30 [F Z>=0 THFN 130

40 [F Z=-1 THEN 70

50 IF Z=-2 THEN 90

```

60 IF Z=-3 THEN 110

70 PRINT "RING RUFFER OVERRUN, SAMPLING TOO FAST"; I

80 GO TO 150

90 PRINT "NO DATA AT EVENT YET"; I

100 GO TO 140

110 PRINT "HARDWARE DATA OVERRUN, SAMPLING TOO FAST"; I

120 GO TO 150

130 PRINT Z

140 NEXT I

150 CONTINUE

160 END

```

#### 2.4 MODULE LPS1 (A/D CONVERSION AND NUMERIC READOUTS)

## 2.4.1 Analog to Digital Conversion (ADC)

ADC

The ADC routine initiates an A/D conversion from the specified channel, waits for it to complete, and returns the conversion as a floating point result in A (in the range 0 to 4095 for the LPS11 and 1023 for the AR11). The A/D cannot be currently involved in a real-time sampling (RTS) operation.

The form of the call is:

CALL "ADC" (b, A[,i])

where

- b specifies the channel and must be in the range from 0 to 63 for LPS11 and 0 to 15 for AR11.

- A is the target variable and will contain the floating point conversion from the analog input.

The value returned is as follows:

A=data/gain (where gain=1,4,16,64) For LPS11 with gain.

A=data When the AR11 is in bipolar mode. A is always positive.

A=-data When the AR11 is in unipolar mode. A is always negative.

i specifies the gain setting for the requested A/D conversion on an LPS11, or the range (bipolar or unipolar) on an AR11.

### when

- i=0 software auto-gain ranging

- =1 gain of 1 for LPS11 (-5V to +5V); bipolar range for AR11 (-2.5V to +2.5V).

- =2 gain of 4 for LPS11 (-1.25V to +1.24V); unipolar range for AR11 (0 to +5V).

- =3 gain of 16 for LPS11 (-0.3V to +0.3V); illegal for AR11.

- =4 gain of 64 for LPS11 (-0.078V to +0.078V); illegal for AR11.

The default value is 1.

#### NOTE

On an LPS11, the LPSAG option must be present when i is not equal to 1, otherwise the value returned in the target variable will be unspecified (i.e., dependent on hardware).

### Example:

Sample the A/D from channels 4 and 5, use a gain of 1, and save the results in arrays A4 and A5 respectively. Assume 100 samples are to be taken.

- 10 DIM A4(100), A5(100)

- 20 FOR I=1 TO 100

- 30 CALL "ADC"(4,A4(I))

- 40 CALL "ADC"(5,A5(I))

- 50 NEXT I

#### 2.4.2 Real-Time Sampling (RTS)

## RTS

The RTS routine performs real time buffered/clocked sampling of the A/D.

The form of the call is:

CALL "RTS"(A[(i)],cl,c2,n,m[,i])

#### where

- A[(i)] is a buffer previously defined in a call to the USE routine. The sampling will be stored in this buffer. The data pointers in the ring buffer will be reset before sampling is begun.

- cl determines the first channel to be sampled. Must have a value between 0 and 15 for AR11 or LPS11 with gain other than 1 specified; or 0 to 63 for LPS11 with no gain or gain equal to 1. This value must be between 0 and 7 when dual sample and hold is required.

- c2 determines the number (or number of pairs) of sequential channels which will be sampled. The maximum is 16 for AR11 or LPS11 with gain other

than 1 specified; and 64 for LPS11 with no gain or gain equal to 1.

#### NOTE

The sum of C1 and C2 cannot be greater the 64.

- n determines the total number of samplings.

- m determines the mode of sampling.

- i specifies the gain setting for the requested  $\mbox{A/D}$  conversion.

#### when

- i=0 software auto-gain ranging

- =1 gain of 1 for LPS11 (-5V to +5V); bipolar range for AR11 (-2.5V to +2.5V).

- =2 gain of 4 for LPS11 (-1.25V) to +1.25V; unipolar range for AR11 (0 to +5V).

- =3 gain of 16 for LPS11 (-0.3V to +0.3V); illegal for AR11.

- =4 gain of 64 for LPS11 (-0.078V to +0.078V); illegal for AR11.

The default value is 1. When (cl + c2) is greater than 16, it is illegal for i to be equal to zero or greater than 1.

#### NOTE

On an LPS11, the LPSAG option must be present when i is not equal to 1, otherwise the value returned in the target variable will be unspecified (i.e., dependent on hardware).

The A/D can be enabled in a variety of modes depending on the options specified. The normal mode of operation (m=0) causes the A/D to sample whenever Schmitt trigger 1 fires for the LPS11 or external start for the AR11. To enable other options, merely add their code number to the mode. The following table describes options available (all options are normally disabled):

Table 2-1 Mode Options in RTS Sampling

| Code | Option                                                                             |

|------|------------------------------------------------------------------------------------|

| 0    | Normal operation, reads on Schmitt trigger 1 for LPS11 or external start for AR11. |

| +1   | Enable burst mode (used only with DMA)                                             |

| +2   | Enable clock, disable Schmitt trigger 1 (used with LPSAD12, LPSKW or AR11)         |

| +4   | Enable dual sample and hold for LPS11 only (used with LPSSH)                       |

| +8   | Enable DMA for LPS11 only (used with LPSAD-NP)                                     |

The burst mode can be used with Direct Memory Access only and the dual sample and hold mode can be used with the Direct Memory Access. The dual sample and hold, and DMA options can only be used on the LPS11. The following table lists all possible values for m and the modes enabled.

Table 2-2 Mode for Values of m

|                                                                | m    | Mode                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPS11                                                          | AR11 |                                                                                                                                                                                                                                                                                                                               |

| 0<br>2<br>4<br>6<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | 0 2  | Schmitt trigger 1 or external start Clock Dual Sample and Schmitt trigger 1 Dual Sample and Clock DMA and Schmitt trigger 1 DMA and Burst DMA and Clock DMA and Burst DMA, Dual Sample, and Schmitt trigger 1 DMA, Dual Sample, and Burst DMA, Dual Sample, and Burst DMA, Dual Sample, and Clock DMA, Dual Sample, and Burst |

The A/D is started by a clock overflow or the firing of Schmitt trigger 1 (external start for AR11). Pointers are used to determine if data exists in the buffer arrays or if data wrap-around occurs. Since data is stored in circular buffers (excluding DMA operations), pointers are used to ensure that the incoming data rate does not exceed the removal rate. Data returned as -1 indicates ring buffer overrun; data returned as -2 indicates no data exist; data returned as -3 indicates hardware overrrun (interrupt service too slow). The buffer pointers are reset initially before the sampling operation begins.

A/D channels are sampled on every clock overflow or firing of Schmitt trigger 1 (external start for AR11) with the result stored in consecutive data cells. Data is stored in a format identical to that read from the A/D (bits 0-11 for data and bits 11-12 for gain). When a clock overflow or Schmitt trigger firing occurs, the A/D samples the first channel specified by cl and then samples the next c2 minus 1 consecutive channels. Sampling then continues until n clock overflows or Schmitt triggers have been received. If n is specified as zero, any previous RTS sampling will be disabled.

In dual sample and hold mode, parameter c2 is the number of pairs of channels to read per sampling. Parameter n defines the number of samplings. There are 2\*C2 elements per sampling.

DMA operations may use dual sample and hold. DMA allows direct hardware storage of A/D results from only one channel into a specified buffer array. A maximum of 4096 data may be taken at any one time with removal of data allowed only when the buffer is completely filled.

NOTE

When DMA is used with dual sample and hold, the parameter C2 must be 1, BASIC automatically assigns the value of 1 to C2 and any other number that is assigned to C2 will be ignored.

RTS operations do not interfere with sampling operations other than ADC (i.e., DRS and HIST routines) and all can be in progress simultaneously. You must set up the clock by making a call to the SETR routine before calling the RTS routine.

#### Example:

Set up the A/D to read data from channels 0 through 3 and store the results in the array A. Schmitt triggers are to be used to fire the A/D. Note that a dimension of 100 allows 200 data points. Since 4 channels are to be sampled, 50 Schmitt triggers will be required to complete the request.

- 10 DIM A(100)

- 20 CALL "USE"(A)

- 30 CALL "RTS"(A,0,4,100\*2/4,0)

#### 2.4.3 Display on the Light Emitting Diodes (LED)

**LED**

A call to the LED routine displays the floating point value of the specified expression on the LEDs (Light Emitting Diodes) of the LPS11. Up to six positive or five negative digits can be displayed in the LEDs. An optional decimal point can also be included. Numbers which cannot be accurately displayed (i.e., E numbers or 6-digit negative numbers) are shown as all minus signs.

This routine acts as a NOP (no-operation) when \$ARll is defined in PERPAR.MAC for an ARll system.

The form of the call is:

CALL "LED"(a)

where

a the expression or the value to be displayed.

Example:

Display the value 5.632 on the LEDs.

10 A=5.632 20 CALL "LED"(A)

or

10 CALL "LED" (5.632)

## 2.4.4 Returning A/D Data from Buffer (CVSG)

## CVSG

The CVSG routine returns the unformatted data value sampled by the RTS routine in one variable and the gain in a separate variable. A -1 will be returned if the data is bad (defined as overrun). A -2 will be returned if there is no data. A -3 will be returned when a hardware data overrun occurs.

The form of the call is:

CALL "CVSG"(V,I)

where

- V is the target variable and contains the floating point conversion from the analog input in the range 0 to 4095 for LPS11 and 0 to 1023 for AR11.

- I returns the gain setting of the requested A/D conversion.

when

- =1 gain of l for LPS11 (+or-5V); bipolar range for AR11 (+or-2.5V).

- =2 gain of 4 for LPS11 (+or-1.25V); unipolar range for AR11 (0 to +5V).

- =3 gain of 16 for LPS11 (+or-.3V); illegal for AR11.

- =4 gain of 64 for LPS11 (+or-.078V); illegal for AR11.

#### 2.5 MODULE LPS2 (REAL-TIME CLOCK)

## 2.5.1 Setting the Clock Rate (SETR)

## **SETR**

A call to the SETR routine sets the clock running in the specified

mode and at the designated rate. The interrupt enable is always set (except mode 8 and above).

The form of the call is:

CALL "SETR" (r,m,p)

where

- r determines the rate of the clock.

- m determines the mode of the clock.

- p is the preset value of the clock counter. The preset value must be less than 65535 (decimal) for the LPSKW and 255 (decimal) for the AR11.

The following preset values are illegal for the indicated rates in interrupt mode.

| Rate | Illegal preset values                                    |

|------|----------------------------------------------------------|

| 1    | <150<br><180 (for systems with memory management option) |

| 2    | <15<br><18 (for system with memory management option)    |

| 3    | =1                                                       |

NOTE

All values of rate and preset are legal in interrupt mode.

The following tables describe the rates and modes  $\,$  determined  $\,$  by  $\,$  the values of r and m.

Table 2-3 Selecting the Clock Rate

| Values of r                          | Rate                                                                                                                    |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | No rate selected 1 MHz 100 kHz 10 kHz 1 kHz 1 kHz 1 character (external event for AR11) Line frequency (50 Hz or 60 Hz) |

Table 2-4

Selecting the Clock Mode

| Values of | m                                                                                                                                                                                               | Mode                                                                                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | Single into                                                                                                                                                                                     | terval mode. Counter counts from preset value to and stops.                                                                                                                  |

| 1         |                                                                                                                                                                                                 | interval mode. Counter counts from preset value to transfers buffer/preset register to the counter, again.                                                                   |

| 2         | and a pu                                                                                                                                                                                        | event timing mode. The counter is free running, alse from Schmitt trigger 2 transfers contents from er to the buffer/preset register and then continues Not valid for ARII.  |

| 3         | except whe                                                                                                                                                                                      | ing from zero base mode is the same as mode 2 en the transfer of the counter to the buffer/preset is done, the counter is cleared and the count om zero. Not valid for AR11. |

| 4,5,6,7   |                                                                                                                                                                                                 | ck only after Schmitt trigger 1 fires. Mode is mined by the value of m-4. Not valid for AR11.                                                                                |

| 8 to 15   | Indicates the operation of the clock in a non-interrupt mode has been added for faster A/D data acquisition. To get the value of m, just add 8 to the value of the interrupt mode. For example: |                                                                                                                                                                              |

|           | m = 0 + 8                                                                                                                                                                                       | indicates single interval non-interrupt mode clock operation.                                                                                                                |

|           | m=1+8                                                                                                                                                                                           | indicates repeated interval non-interrupt mode clock operation.                                                                                                              |

#### Example:

Set the clock running to interrupt once every second. A 100 Hz frequency is used and the clock mode is 1.

CALL "SETR"(5,1,100)

Each programmable clock interrupt causes a 16-bit software clock (counter) to be incremented by one. When the maximum count of 65535 is reached, the next interrupt causes a reset to zero. This clock may be retrieved by the RTIM and DRS routines.

## 2.5.2 Setting the Clock to Rate and Time (SETC)

## SETC

A call to the SETC routine sets clock to specified rate and time.

The form of the call is:

CALL "SETC"(r,t)

where

- r determines the clock rate as described i n Table 2-3, and may be 4.5, or 7.

- is the time in seconds that the clock runs before issuing an interrupt.

The clock status register is set to rate determined by r and runs for t seconds. A clock interrupt then occurs which can be used to initiate any of the clock controlled functions. The time argument is evaluated as ticks equal time in seconds multiplied by the clock rate specified, e.g., if the clock rate was 10kHz, then ticks equal time in seconds multiplied by 10kHz. The ticks are entered into the clock preset/buffer register. The clock always runs in mode 0.

#### Example:

Set the clock to interrupt in 10 seconds using a 100 Hz frequency.

CALL "SETC" (5,10)

## 2.5.3 Histograms - Timed Schmitt Trigger (HIST)

HIST

The HIST routine inputs values from the clock preset/buffer register and stores them into the specified buffer whenever Schmitt trigger 2 fires. The clock must be in mode 2 or 3 for the data to be meaningful.

The form of the call is:

CALL "HIST" (T[(i)], n)

where

T[(i)] is a buffer previously defined in a call to the USE routine.

determines the total number of data points stored.

The RDB function is used to retrieve the data. The data pointers in the ring buffer are reset before the sampling operation begins.

If n is given as zero, the HIST sampling will be disabled.

HIST operations do not interfere with other sampling operations (i.e., RTS and DRS) and all can be in progress simultaneously.

HIST routine acts as a NOP (no-operation) when \$ARll is defined in PERPAR.MAC for an ARll system.

#### Example:

Collect a timed histogram between external events (Schmitt trigger 2) and store the results in array T. The clock runs at 1 kHz and 100 intervals are required.

- 10 DIM T(50)

- 20 CALL "USE"(T) 30 CALL "HIST"(T,100)

- 40 CALL "SETR" (4,3,1)

## 2.5.4 Delaying Program Execution (WAIT)

## WAIT

A call to WAIT disables further program execution until the specified event occurs.

The form of the call is:

CALL "WAIT" (n)

where

n specifies the event that must occur for program execution to continue.

Values of n are:

- n=0 Wait for clock to overflow only.

- n=1 Wait for Schmitt trigger 1 (external event for AR11) to fire (for clock rate = 6 only).

- n=2 Wait for clock to overflow or Schmitt trigger 1 to fire.

- n>2 Returns immediately.

- n<0 Wait for Schmitt trigger 1 (external event for AR11) to fire (a call to the SETR or SETC routine must be made prior to this).

#### Example:

Wait for clock to overflow.

10 CALL "WAIT"(0)

#### 2.5.5 Returning Current Software Clock Tick Value (RTIM)

## RTIM

A call to the RTIM routine returns the 16-bit integer value of the internal software clock counter maintained by the programmable clock.

The form of the call is:

CALL "RTIM"(s,t)

where

- s specifies whether the internal clock counter is to be cleared or not. The counter is cleared when s is equal to 0; otherwise it is unaltered.

- t is the 16-bit integer value of the internal clock counter.

#### 2.6 MODULE LPS3 (DIGITAL I/O)

The user should read the LPS11 Laboratory Peripheral System User's Guide in order to fully understand the hardware latching mechanism before using these modules.

The interrupt control logic permits the LPSDR-A or the DR11-K to perform an interrupt operation. The switches and jumpers on this logic can be arranged so that vector address can be assigned other than those configured as standard on the module for alignment.

One method of causing interrupts to the Unibus uses the two control lines between the DR11-K and the external device. If the input interrupt enable (bit 6 of the status register) is set, a negative transition (+3 v to ground) of the EXTERNAL DATA READY pulse will generate an interrupt to the Unibus, with a vector address of 300. A bus request is made on the BR level that corresponds with the level of the priority plug in the logic (the standard level for the DR11-K interface is BR4; this may be changed on the priority plug if desired). The control line method of interrupting is logically ORed into the DR11-K interrupt control, and is disabled by internal clamping circuitry if not desired. The device will continue interrupting as long as the line is held low.

The second and most preferred method of interrupting is to use the individual input lines. Each input (IN15:IN00) is buffered by a flip-flop that will set on a negative transition (+3 v to ground). Switches for the buffered bits on the hardware option make it possible to wire-OR each bit onto a common interrupt line. When the input interrupt enable (bit 6 of the status register) is set and a switch is on, the transition of the associated bit causes an interrupt to the Unibus. The bits are read under program control by reading the input register, and are cleared by moving data ls to the bits to be cleared. The input interrupt enable is cleared when an input interrupt is accepted by the Unibus; when reset, it will retrigger the interrupt circuit if any other input bits were set during the program service subroutine, so that new interrupting bits will not be lost.

#### 2.6.1 Reading the Digital Input Register (DIR)

DIR

A call to DIR reads the Digital Input Register and converts it to a floating point number. The form of the call is:

CALL "DIR"(i, V, S[, m[, j]])

where

- i determines the type of floating point conversion.

- v is the target variable. It is the value in the input register ANDed with m.

- S contains the returned digital Control Status Register (CSR) setting.

- m indicates the 16-bit mask. The default value is -1.

- j indicates the number of the DR11-K unit on a multiple DR11-K system. The default value is 0. The maximum legal value is determined by the parameter \$NUMBER in PERPAR.MAC at the assembly time of PERVEC.MAC module.

If i=0, input is four Binary Coded Decimal (BCD) digits converted to a floating point number and the result is in the range 0 to 9999. If i<>0, then the binary result read from the register is directly converted to a floating point number and the result is in the range 0 to 65535. The Digital Input Register is read via an internal load request and does not respond to interrupts. The input word is immediately written back into the input register to clear those bits which were obtained from the register. The result is returned in V.

The new CSR register setting is returned in S.

#### Example:

320 RETURN 500 END

```

1 REM THIS PROGRAM TESTS THE "DIR", "DOR" AND "DRS" MODULES ALONG WITH

2 REM SETR, WAIT AND RDB. THE INPUT AND THE OUTPUT DIGITAL CABLES MUST BE

3 REM CONNECTED TO EACH OTHER.

4 DIM X(30)

5 0=1

6 CALL "DOR"(1,65535,N)

7 CALL "USE"(X)

10 FOR I=1 TO 16

20 CALL "DOR"(0,0,N)

30 CALL "DIR"(1,Y,N1)

40 PRINT NOY

50 0=0*2

60 NEXT I

160 CALL "DOR" (1,65535,N)

165 CALL "DRS" (X)1,30,0,N)

170 CALL "SETR" (5,1,100)

175 M=0

180 0≔0

185 FOR I=1 TO 30

190 CALL "DOR"(1,65535,N)

195 CALL "DOR"(M,O,N)

200 0=0+4096+256+16+1

205 CALL "WAIT"(O)

210 NEXT I

215 GOSUB 300

220 STOP

300 FOR J=1 TO 30

305 CALL "RDB"(X,Y)

310 PRINT JyY

315 NEXT J

```

## 2.6.2 Writing to the Digital Output Register (DOR)

DOR

A call to DOR can either set or clear selected bits in the Digital Output Register. The form of the call is

CALL "DOR" (m,n,R[,j])

where

- m determines whether bits are to be set (when m=0) or cleared (when m is not equal to 0).

- n determines which bits are to be set or cleared.

- R contains the floating point equivalent to the new value in the Digital Output Register.

- j indicates the number of the DR11-K unit on a multiple DR11-K system. The default value is 0. The maximum legal value is determined by the parameter \$NUMBER in PERPAR.MAC at the assembly time of PERVEC.MAC module.

If a bit in the binary representation of n is 1, the corresponding bit of the Digital Output Register will be cleared or set (depending on the value of m). If a bit in the binary representation of n is 0, the corresponding bit of the Digital Output Register will not be changed. The BASIC-11 BIN and OCT functions are very useful in setting or clearing the registers.

#### Example:

Turn on (set) bits 1 and 2 of the Digital Output Register.

- 40 CALL "DOR"(0,BIN'110',N) Clear Digital Output Register.

- 40 CALL "DOR" (1,OCT'177777', N)

or

40 CALL "DOR" (1,-1,N)

## 2.6.3 Digital Readout Sampling (DRS)

**DRS**

A call to the DRS routine samples the Digital Input Register in a similar fashion as the RTS function.

The form of the call is:

CALL "DRS"(A[(i)],ml,n,m2,R[,T[,m[,j]]])

where

| A[(i)] | is a buffer previously defined in a call to the USE routine.                                                                                                                                                          |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ml     | determines the mode by which the Digital Input<br>Register is to be read.                                                                                                                                             |

| n      | determines the total number of samplings.                                                                                                                                                                             |

| m 2    | determines whether the sampling is clock driven.                                                                                                                                                                      |

| R      | contains the returned setting of the digital Control Status Register (CSR).                                                                                                                                           |

| Т      | describes the address of the buffer to store the current clock TICK value on every data interrupt when m2 is not equal to zero.                                                                                       |

| m      | indicates the 16-bit mask. The default value is $-1$ .                                                                                                                                                                |

| j      | indicates the number of the DR11-K unit on a multiple DR11-K system. The default value is 0. The maximum legal value is determined by the parameter \$NUMBER in PERPAR.MAC at the assembly time of PERVEC.MAC module. |

When m2 is equal to 0, each time the clock fires (Schmitt trigger, or external event for AR11), the Digital Input Register is read.

If ml is equal to zero the Digital Input Register will be treated as Binary Coded Decimal and will be converted to binary. If ml is not equal to zero the Digital Input Register will be input directly as a binary number. This number is stored in the circular buffer specified by A[(i)]. When DRS is first called, it resets the pointers of the buffer to the beginning.

If n is given as zero, the DRS sampling will be disabled. The DRS call is driven by digital clock when m2 is not equal to zero. Whenever a new value is received in the input register, the value is immediately read in and stored in the buffer. The value of the 16-bit software clock is stored in the buffer specified by T. The input data word is immediately written back into the input register, and the active bit which have been sampled are cleared.

The new setting of the digital Control Status Register is returned in  $\mathbb{R}$ .

#### Example:

Read the Digital Input Register once every one tenth of a second for 100 readings and store the results in array A.

```

10 DIM A(50)

```

<sup>20</sup> CALL "USE"(A)

<sup>30</sup> CALL "DRS"(A,0,100,0,N)

<sup>40</sup> CALL "SETR" (5,1,10)

### 2.6.4 Relay Control (REL)

REL

A call to the REL routine opens or closes the specified relay.

The REL routine acts as a NOP (no-operation) when \$AR11 is defined in PERPAR.MAC for an AR11 system.

The form of the call is:

CALL "REL" (a,b)

where

- specifies the relay and may be equal to 1 or 2.

- b determines the operation. Relay is opened if equal to 0, otherwise it is closed.

#### Example:

Open relay 1 and close relay 2.

100 CALL "REL"(1,0) 110 CALL "REL"(2,1)

### 2.6.5 Reading/Writing Data From/Into Memory (IPK)

IPK

The IPK routine can be called to read a value from a specified address or place a value into a specified address. The form of the call is:

CALL "IPK"(s,a,V)

where

indicates whether the value is a word or a byte. If s is even, the word value supplied in V will be read from or written into the even address register. If s is odd, the byte value supplied in V will be read from or written into the odd address register.

A call such as CALL "IPK" (0,64,V) reads into variable V the value at location 64 in memory.

specifies the address where the value V is read from or written into. This address must be even when the value of s is even. This address can be specified as an octal string, integer constant or integer variable.

A call such as CALL "IPK" (2,73,100) is illegal because the address is odd; the error message ?ARG will result.

V is the value to be read from or written into the address register.

NOTE

This routine should not be used except to read from or write into the I/O page or to read from memory. Writing into memory can cause serious consequences (program being wiped out, etc.).

### 2.7 MODULE LPS4 (DISPLAY)

The routines in this module require the LPSVC or AR11 with the VR14 interfaced through it. The VT11 cannot be used with these routines.

#### 2.7.1 Defining the Display Buffer (CLRD)

## **CLRD**

A call to the CLRD routine defines the display buffer having fixed delta  ${\bf x}$  values.

The form of the call is:

CALL "CLRD" (A[(i)],a,b)

where

A[(i)] is a buffer previously defined by a call to the USE routine.

a specifies the size of the buffer to be displayed.

b specifies the scale.

The buffer to be displayed should contain single word values. Values in the range 4095 >= value >= 0 are displayed while values outside this are not. The size of the buffer, a, is the number of Y points to display and must be less than or equal to the number of points defined in the DIM statement and the call to the USE routine. The delta x is calculated as 4096/a and can be fractional.

If b, the scale, equals 0, CLRD will set all buffer values to -1 (non-displayable values). If scale does not equal 0, CLRD bypasses the clearing of the array and the original data is multiplied by b. In either case, the PUTD pointers are reset to point to the beginning of the array. Data is entered into the array through the PUTD function; however, a CLRD must be issued before data is initially transferred to the array.

A CLRD routine must be issued at least once before issuing the DIS, FSH, or DXY functions which can display the buffer defined by CLRD.

Example:

Set up the array C to be used as a display buffer having 256 points.

10 DIM C(128) 20 CALL "USE"(C) 30 CALL "CLRD"(C,256,0)

## 2.7.2 Putting Data into Display Buffer (PUTD)

PUTD

A call to the PUTD routine puts a data value into the specified buffer. Repeated calls to PUTD will cause the buffer to be filled sequentially.

The form of the call is:

CALL "PUTD" (A[(i)],b)

where

A[(i)] is a buffer previously defined by the USE routine.

b is the value to be inserted. Must be in range  $0 \le 65535$ .

This function does not initiate a display, but rather just enters data into the specified array.

#### Example:

Remove 100 data points from the specified digital sampling buffer  $\, \, {\rm D} \, ,$  and transfer them to the buffer  $\, {\rm Z} \, .$

80 DIM D(50),X(50) 90 CALL "USE"(D,X) 100 FOR I=1 TO 100 110 CALL "RDB"(D,X) 120 CALL "PUTD"(Z,X) 130 NEXT I

#### 2.7.3 Background Display Routine (DIS)

DIS

A call to the DIS routine displays data from the buffer whenever BASIC is idle. Data is not displayed by DIS or DXY routines under RT-11 FB system because BASIC is never idle. Data is displayed under RT-11 SJ system (version 2 or later) only when I/O is taking place.

The form of the call is:

CALL "DIS"(A[(i)],a,b[,n]) where

A[(i)] is a display buffer previously defined by the USE and CLRD routines.

- a determines the starting point of the display.

- b determines the frequency of points in the buffer that are to be displayed.

- n specifies the number of data point to display. The default value is all remaining elements of the array.

The points displayed start with the point a in the buffer and proceed in increments of b. If b is equal to 1, consecutive points starting with the a one are displayed. If b is equal to 2, every other point is displayed, etc.

#### Example:

Display data from buffer E beginning at the 12th data point and displaying every 3rd point of the remaining array elements.

```

20 DIM E(100)

40 CALL "USE"(E)

60 CALL "CLRD"(E,200,0)

80 REM BUFFER MAY BE FILLED HERE

100 CALL "DIS"(E,12,3)

120 REM OR MAY BE FILLED HERE

```

#### Example:

```

5 REM THIS PROGRAM TESTS THE ROUTINES-USE, CLRD, PUTD, DIS, FSH-ALONG WITH

10 REM SETRYAND WAIT

15 PRINT "PROGRAM TO TEST CLRD PUTD DIS AND FSH."

50 CALL "SETR" (5,1,10)

100 DIM A(100)

200 CALL "USE"(A)

300 CALL "CLRD"(A,100,0)

400 FOR I=1 TO 100

500 CALL "PUTD" (A)I)

600 NEXT I

700 CALL "DIS"(A+1+1)

710 INPUT D

750 CALL "DIS"(A,1,1,75)

760 INPUT D

780 CALL "DIS"(A)1,1,50)

G TUPHI 008

900 IF D=0GO TO 2000

950 FOR S=1 TO 99

975 FOR I=1 TO 50

980 FOR D=1 TO 100

1000 CALL "FSH"(A,S,I,D)

1010 CALL "WAIT"(O)

1025 NEXT D

1030 NEXT I

1050 NEXT S

1100 GO TO 800

2000 STOP

```

### 2.7.4 Display Buffer (FSH)

FSH

The FSH routine is identical to the DIS routine except that the data points in the buffer are completely displayed only once when this call is executed. The next BASIC statement is then executed.

The form of the call is:

CALL "FSH"(A[(i)],a,b[,n])

where

A[(i)] have the same b meaning n as in DIS.

#### Example:

Using the previous example, display 100 cycles of the array E.

100 FOR I=1 TO 100 110 CALL "FSH"(E,12,3) 120 NEXT I

## 2.7.5 Displaying X,Y Data (DXY)

DXY

A call to the DXY routine displays points from two buffers as x and y values. These buffers are displayed whenever BASIC is idle. Data is displayed under RT-11 SJ system (version 2 or later) only when I/O is taking place.

The form of the call is:

CALL "DXY" (X[(i)],Y[(j)],a,b[,n])

where

X[(i)] is a buffer previously defined by a call to the

USE routine and contains the x values.

Y[(j)] is a buffer previously defined by calls to the USE

and CLRD routines and contains the y values.

a determines the starting point in both buffers

b determines the frequency of the points in each

buffer to be displayed.

n specifies the number of data points to display.

The default value is all remaining elements of the

array.

The buffer containing the x values, X[(i)] does not have to be initialized by a call to CLRD, but it may be convenient to do so to initialize all values so that they are non-displayable. The buffer containing the y values must be initialized by a call to CLRD although the value of delta x is not used.

As in the other display routines the a determines the location of the first point to be displayed in each buffer and b determines the frequency of points to be displayed. If b equals one, consecutive values are taken from the two buffers. If b equals two, every other value in each buffer will be used to create the display.

### Example:

Generate fiducial marks on the display screen of a 256-point display every 16 points. Marks will be 10 points in height. Data will be generated into the arrays X and Y.

```

5 REM THIS PROGRAM TFSTS -DXY AND FXY- ROUTINES

10 PRINT "TFST PROGRAM FOR DXY AND FXY ROUTINES"

20 DIM X(128), Y(128)

30 CALL "USF"(X,Y)

40 CALL "CLRD"(X,256,0)

50 CALL "CLRD"(Y,256,0)

60 FOR I=16 TO 256 STFP 16

70 FOR J=1 TO 10

80 CALL "PUTD"(X,I)

90 CALL "PUTD"(Y,J)

100 NEXT J

110 NFXT I

120 CALL "DXY"(X,Y,1,1)

130 STOP

140 END

```

## 2.7.6 Flashing X-Y Data (FXY)

# FXY

The FXY routine is the same as DXY routine except that the X and Y values are displayed only once when this call is made.

The form of the call is:

## Example:

```

5 REM THIS PROGRAM TESTS -DXY AND FXY- ROUTINES

10 PRINT "TEST PROGRAM FOR DXY AND FXY ROUTINES"

20 DIM X(128), Y(128)

30 CALL "USE"(X, Y)

40 CALL "CLRD"(X, 256, 0)

50 CALL "CLRD"(Y, 256, 0)

```

```

60 FOR I⇒16 TO 256 STEP 16

70 FOR J=1 TO 10

80 CALL "PUTD"(X,I)

90 CALL "PUTD"(Y) J)

100 NEXT J

110 NEXT I

120 CALL "DXY"(X,Y,1,1)

130 INPUT D

140 CALL "DXY"(X, Y, 1, 1, 25)

150 INPUT D

160 CALL "DXY"(X,Y,1,1,50)

170 IMPUT D

180 IF D=0GO TO 260

190 FOR S=1 TO 99

200 FOR I=1 TO 50

210 FOR D=1 TO 100

220 CALL "FXY"(X,Y,S,I,D)

230 NFXT D

240 NEXT I

250 NEXT S

260 STOP

270 END

READY

```

#### 2.8 HARDWARE REQUIRED FOR LPS COMMANDS

The following summary describes the hardware necessary to fully utilize the LPS system.

| Command | Hardware Required                           |

|---------|---------------------------------------------|

| USE     | None                                        |

| ACC     | None                                        |

| RDB     | None                                        |

| ADC     | LPSAD-12, LPSAM (for additional 8 channels) |

| RTS     | LPSAD-12, LPSAD-NP (for DMA operations)     |

|         | LPSAM (for additional 8 channels)           |

|         | LPSSH (for dual sample and hold)            |

|         | LPSKW (for real-time clocking and Schmitt   |

|         | triggers)                                   |

|         | LPSAG-VG (for multi-gain)                   |

| LED     | LPSAD-12                                    |

| CVSG    | None                                        |

| SETR    | LPSKW                                       |

| SETC    | LPSKW                                       |

| HIST    | LPSKW                                       |

| WAIT    | L <sub>PSKW</sub>                           |

| RTIM    | L <sub>P</sub> SKW                          |

| DIR     | L <sub>PSDR</sub>                           |

| DOR     | L <sub>PSDR</sub>                           |

| DRS     | LPSDR                                       |

| REL     | LPSDR                                       |

| IPK     | None                                        |

| CLRD    | None                                        |

| PUTD    | None                                        |

| DIS     | LPSVC                                       |

| FSH     | LPSVC                                       |

| DXY     | LPSVC                                       |

| FXY     | LPSVC                                       |

The routines that require the AR11 are ADC, RTS, SETR, SETC, WAIT, and RTIM.

## LABORATORY PERIPHERAL SYSTEM SUPPORT

The routines that require the VR14 in addition to the AR11 are DIS, FSH, DXY, and FXY.

The routines that require the DR11-K are DIR, DOR, and DRS.

# 2.9 EXAMPLE PROGRAMS

50 DIM A(20)

```

THIS PROGRAM TESTS THE "ADC" MODULE

2 REM

IT REQUIRES 2 INPUTS: CHANNEL # AND IGAIN FROM CONSOLE

3 REM

A CHANNEL # EQUAL TO -1 TERMINATES PROGRAM

10 INPUT C

20 INPUT G

30 IF C=-1 THEN 100

40 CALL "ADC"(C,V)

50 PRINT V, ABS(V)

60 CALL "ADC" (CyV1y1)

70 PRINT V1,ABS(V1)

80 CALL "ADC"(C,V2,G)

90 PRINT U2,ABS(U2)

95 GO TO 10

100 END

**

1 REM THIS PROGRAM TESTS THE DRS MODULE TIME LOG FEATURE

3 DIM Z(30)

4 DIM X(30)

50=1

6 CALL "DOR"(1,65535,N)

8 CALL "USE"(X,Z)

10 FOR I=1 TO 16

20 CALL "DOR"(O,O,N)

30 CALL "DIR"(1,Y,N1)

40 PRINT NOY

50 0=0*2

60 NEXT I

160 CALL "DOR"(1,65535,N)

165 CALL "DRS"(X,1,30,1,N,Z,7)

166 PRINT "*******" , N , "**********

170 CALL "SETR"(4,1,1)

175 M≕0

180 0 = 0

185 FOR I=1 TO 30

190 CALL "DOR"(1,65535,N)

195 CALL "DOR" (MyOyN)

200 0=0+256+16+1

210 NEXT I

215 GOSUB 300

220 STOP

300 FOR J=1 TO 30

305 CALL "RDB"(X,Y)

306 CALL "RDB"(Z,Y1)

310 PRINT JyYyY1

315 NEXT J

320 RETURN

500 END

10 RFM

THIS PROGRAM TESTS THE "RTS" MODULE

20 REM

IT REQUIRES 3 INPUTS: STARTING CHANNEL #, NUMBER OF CHANNELS

AND IGAIN FROM CONSOLE

40 RFM A STARTING CHANNEL # EQUAL TO -1 TERMINATES PROGRAM

```

### LABORATORY PERIPHERAL SYSTEM SUPPORT

```

60 CALL "USE"(A)

70 INPUT S

80 IF S=-1 THEN 150

90 IMPUT N

100 INPUT G

110 CALL "SETR"(5,1,100)

120 CALL "RTS"(A, S, N, 20, 2, G)

130 GOSUB 200

1.40 GO TO 50

150 STOP

170 CALL "RDB"(A, Z)

180 IF ZC0 THEM 170

190 RETURN

200 FOR I=1 TO 4

210 GOSUB 170

220 R1=Z

230 GOSUB 170

240 A2=7

250 GOSUR 170

260 A3=Z

270 GOSUB 170

280 A4=Z

290 GOSUB 170

300 A5=Z

R10 PRINT A1, A2, A3, A4, A5

320 NFXT I

330 RETURN

340 END

READY

1 REM

THIS PROGRAM TESTS THE "RTS" & "CVSG" ROUTINES

IT REQUIRES 3 INPUTS: STARTING CHANNEL ## NUMBER OF CHANNELS

2 REM

3 REM AND IGAIN FROM CONSOLE

A STARTING CHANNEL # EQUAL TO -1 TERMINATES PROGRAM

4 REM

10 DIM A(20)

20 CALL "USE"(A)

30 INPUT S

40 IF S=-1 THEN 100

50 INPUT N

60 INPUT G

70 CALL "SETR"(5,1,100)

80 CALL "RTS" (AySyNy20y2yG)

90 GOSUB 220

95 GO TO 10

100 STOP

200 CALL "CVSG"(Z,V)

210 IF Z=-2 THEN 200

215 RETURN

220 FOR I=1 TO 4

225 GOSUB 200

230 A1=Z

235 V1=V

240 GOSUB 200

250 A2=Z

255 V2=V

260 GOSUB 200

270 A3=Z

275 V3=V

280 GOSUB 200

290 A4=Z

```

## LABORATORY PERIPHERAL SYSTEM SUPPORT

```

295 V4=V

300 GOSUB 200

310 A5=Z

315 V5=V

320 PRÍNT A1,42,43,44,45

325 PRINT V1, V2, V3, V4, V5

350 NEXT I

400 RETURN

1000 END

1 REM THIS PROGRAM TESTS THE "RTIM" MODULE ALONG WITH SETR AND WAIT

2 REM THE LAST 10 VALUES PRINTED WILL BE 0 THRO' 9.

10 INPUT S

20 IF S=-1 THEN 1000

30 CALL "RTIM"(O,V)

40 PRINT V

50 CALL "SETR"(5,1,100)

30 FOR I=1 TO 10

70 CALL "RTIM"(1,V)

80 PRINT V

90 CALL "WAIT"(0)

100 NEXT I