# **XMI Adapters Handbook**

Order Number EK-XMIAD-HB-PRE

This handbook is a quick reference guide to the various I/O adapters which interface XMI-based systems to devices that employ different bus structures and protocols. The handbook is for VAX system trained Digital customer service personnel who are familiar with the XMI bus architecture.

Revision/Update Information: This is a preliminary release

**Digital Equipment Corporation**

#### July, 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227–7013.

Copyright © Digital Equipment Corporation 1990

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

| DEC   | UNIBUS   | VAX 9000 |

|-------|----------|----------|

| DECUS | VAX      | VAXBI    |

| PDP   | VAX 6000 | XMI      |

This document was prepared and published by Educational Services Development and Publishing, Digital Equipment Corporation.

# Contents

# About This Manual

#### xi

## Part I XMI Bus Section

# 1 XMI BUS OVERVIEW

| 1.1 | INTRODUCTION                   | 1-1 |

|-----|--------------------------------|-----|

| 1.2 | IMPLEMENTATIONS                | 1–1 |

| 1.3 | SPECIFICATIONS AND TERMINOLOGY | 1-4 |

| 1.4 | BUS INTEGRITY FEATURES         | 1-6 |

# 2 XMI BUS PHYSICAL DESCRIPTION

| 2.1   | XMI CARD CAGE       | 2–1 |

|-------|---------------------|-----|

| 2.1.1 | Node ID Numbers     | 2-1 |

| 2.1.2 | Clock/Arbiter Card  | 2–1 |

| 2.1.3 | I/O Header Pins     | 2-4 |

| 2.2   | XMI NODE            | 2–5 |

| 2.2.1 | XMI Corner          | 2-5 |

| 2.2.2 | Self-Test LED       | 2–5 |

| 2.3   | CONFIGURATION RULES | 2–5 |

# 3 XMI BUS FUNCTIONAL DESCRIPTION

| 3.1 | ADDRESSING                     | 3–1  |

|-----|--------------------------------|------|

| 3.2 | BUS SIGNALS                    | 3–5  |

| 3.3 | BUS FUNCTION CODES             | 3–7  |

| 3.4 | XMI DATA TRANSFER TRANSACTIONS | 3-8  |

| 3.5 | INTERRUPT TRANSACTIONS         | 3-15 |

| iv Co | ntents |

|-------|--------|

|-------|--------|

| 3.6 | ARBITRATION                 | 3-20 |

|-----|-----------------------------|------|

| 3.7 | BUS INITIALIZATION          | 3-21 |

| 3.8 | XMI NODE REQUIRED REGISTERS | 3-22 |

## 4 DIAGNOSING XMI BUS RELATED ERRORS

| 4.1 | NODE RBDs AND SELF-TESTS | 4-1 |

|-----|--------------------------|-----|

| 4.2 | ERROR CONDITIONS         | 4-1 |

| 4.3 | ERROR HANDLING           | 4-3 |

| 4.4 | ERROR RECOVERY           | 4-3 |

| 4.5 | ERROR REPORTING          | 4-4 |

|     |                          |     |

# Part II CIXCD Section

## 5 CIXCD INTERFACE OVERVIEW

| 5.1 | INTRODUCTION          | 5-1  |

|-----|-----------------------|------|

| 5.2 | FUNCTIONAL OVERVIEW   | 5-1  |

| 5.3 | FEATURES              | 5-6  |

| 5.4 | SPECIFICATIONS        | 5-7  |

| 5.5 | RELATED DOCUMENTATION | 5-10 |

## 6 CIXCD CONFIGURATIONS

| 6.1 | INSTALLATION REQUIREMENTS | 6-1 |

|-----|---------------------------|-----|

| 6.2 | CONFIGURATION JUMPERS     | 6-1 |

# 7 CIXCD SELF-TEST (XCDST) AND ROM-BASED DIAGNOSTICS (RBDs)

| 7.1   | CIXCD SELF-TEST (XCDST)       | 7–1 |

|-------|-------------------------------|-----|

| 7.2   | ROM-BASED DIAGNOSTICS (RBDs)  | 7–3 |

| 7.2.1 | RBD User Interface            | 7–3 |

| 7.2.2 | RBD Commands and Control Keys | 7-4 |

| 7.2.3 | RBD Error Report Formats      | 7-6 |

| 7.2.4 | Sample RBD Run                | 7–7 |

Contents v

| 8 CIXCD MACRODIAGNOSTICS AND SUPPORT       |    |

|--------------------------------------------|----|

| PROGRAMS                                   |    |

| 8.1 INTRODUCTION                           | ·1 |

| 8.2 DIAGNOSTIC PROGRAMS 8-                 | -2 |

| 8.3 RUNNING EVGAA AND EVGAB 8-             | -4 |

| 8.3.1 Sample EVGAA Run 8-                  | .7 |

| 8.3.2 Sample EVGAB Run 8-                  | .9 |

| 8.4 RUNNING EVGAC 8–1                      | 0  |

| 8.4.1 Sample EVGAC Run 8–1                 | 0  |

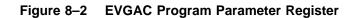

| 8.4.2 EVGAC Program Parameter Register 8–1 | 1  |

| 8.4.3 EVGAC Program Parameters 8-1         | 4  |

| 8.4.4 EVGAC Support Files 8–1              | 6  |

| 8.5 RUNNING EVGEA 8–1                      | 9  |

| 8.5.1 Sample EVGEA Run 8–1                 | 9  |

| 8.5.2 Sample EVGEA Error Message 8–1       | 9  |

| 8.6 EEPROM UPDATE/VERIFICATION UTILITY 8-2 | 21 |

| 8.7 MAINTENANCE SUPPORT TOOLS 8–2          | :3 |

|                                            |    |

| 9 CIXCD REGISTERS                          |    |

| 9.1   | INTRODUCTION                                     | 9-1  |

|-------|--------------------------------------------------|------|

| 9.2   | CIXCD REGISTER TYPES                             | 9-2  |

| 9.3   | ADDRESSING XMI VISIBLE REGISTERS                 | 9–3  |

| 9.4   | INTERNAL BUS (IB) REGISTER ADDRESSING            | 9-6  |

| 9.5   | REGISTER DESCRIPTION CONVENTIONS                 | 9-10 |

| 9.6   | HARDWARE REGISTERS — XMI ARCHITECTURE            | 9–11 |

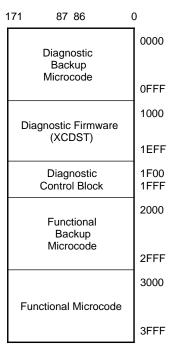

| 9.6.1 | XMI Device Register (XDEV, bb+00000)             | 9-12 |

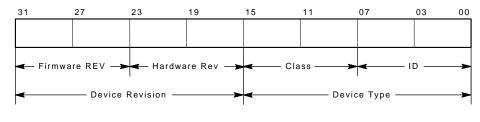

| 9.6.2 | XMI Bus Error Register (XBER, bb+00004)          | 9-15 |

| 9.6.3 | XMI Failing Address Register (XFADR, bb+00008)   | 9–20 |

| 9.6.4 | XMI Failing Address Extension Register (XFAER,   |      |

|       | bb+0002C)                                        | 9-21 |

| 9.6.5 | XMI Communications Register (XCOMM, bb+00010)    | 9-21 |

| 9.7   | HARDWARE REGISTERS — CI ARCHITECTURE             | 9–23 |

| 9.7.1 | Port Scan Control Register (PSCR, bb+00014)      | 9–24 |

| 9.7.2 | Port Scan Data Register (PSDR, bb+00018)         | 9-26 |

| 9.7.3 | Port Maintenance Control/Status Register (PMCSR, |      |

|       | bb+0001C)                                        | 9–27 |

vi Contents

| 9.7.4 | Port Diagnostic Control/Status Register (PDCSR, bb+00020) | 9–33 |

|-------|-----------------------------------------------------------|------|

| 9.7.5 | Port Status Register (PSR, bb+00024)                      | 9-34 |

| 9.8   | SOFTWARE REGISTERS                                        | 9-37 |

| 9.8.1 | Port Queue Block Base Register (PQBBR, bb+01000)          | 9-37 |

| 9.8.2 | Port Error Status Register (PESR, bb+01008)               | 9-38 |

| 9.8.3 | Port Failing Address Register (PFAR, bb+0100C)            | 9-38 |

| 9.8.4 | Port Parameter Register (PPR, bb+01010)                   | 9-39 |

| 9.8.5 | Port Serial Number Register (PSNR, bb+01014)              | 9-41 |

| 9.8.6 | Port Interrupt Destination Register (PIDR, bb+01018)      | 9-41 |

| 9.8.7 | Port Interrupt Vector Register (PIVR, bb+01020)           | 9-42 |

| 9.8.8 | PCQ0CR to PMTECR (bb+01028 to bb+01054)                   | 9-42 |

| 9.8.9 | Port Parameter Extension Register (PPER, bb+01058)        | 9-44 |

# Part III DEC LANcontroller 400 (DEMNA) Section

# 10 DEMNA OVERVIEW

| 10.1 INTRODUCTION                   | 10-1 |

|-------------------------------------|------|

| 10.2 PORT OVERVIEW                  | 10-1 |

| 10.3 FUNCTIONAL OVERVIEW            | 10-3 |

| 10.3.1 Microprocessor Subsystem     | 10-3 |

| 10.3.2 Memory Subsystem             | 10-5 |

| 10.3.3 XMI Interface Subsystem      | 10-6 |

| 10.3.4 Ethernet Interface Subsystem | 10-6 |

| 10.4 PHYSICAL DESCRIPTION           | 10-7 |

| 10.5 ENVIRONMENTAL SPECIFICATIONS   | 10-7 |

| 10.6 REFERENCE DOCUMENTS            | 10-8 |

## 11 DEMNA CONFIGURATIONS

| INTRODUCTION                          | 11-1                                                                                       |

|---------------------------------------|--------------------------------------------------------------------------------------------|

| DEMNA OPTION PACKAGE AND CABINET KITS | 11-1                                                                                       |

| T2020 MODULE PLACEMENT                | 11–3                                                                                       |

| INTERNAL ETHERNET CABLE               | 11–3                                                                                       |

| INTERNAL CABLE FOR PHYSICAL CONSOLE   | 11–3                                                                                       |

|                                       | DEMNA OPTION PACKAGE AND CABINET KITS<br>T2020 MODULE PLACEMENT<br>INTERNAL ETHERNET CABLE |

Contents vii

| 12     | DEMNA POWER-UP SELF-TESTS AND ROM-BASED<br>DIAGNOSTICS (RBDs) |

|--------|---------------------------------------------------------------|

| 12.1   | POWER-UP SELF-TESTS 12–1                                      |

| 12.2   | ROM-BASED DIAGNOSTICS (RBDs) 12–3                             |

| 12.2.1 | RBD COMMANDS         12–5                                     |

| 12.2.2 | RBD CONTROL KEYS         12-12                                |

| 12.2.3 | Running the DEMNA RBDs 12–13                                  |

| 12.2.4 | RBD Error Report Formats    12–13                             |

| 12.2.5 | Diagnostic Error Log Reader 12-14                             |

| 12.2.6 | Isolating Faults With the RBDs 12–17                          |

## 13 DEMNA MACRODIAGNOSTICS AND SUPPORT PROGRAMS

| 13.1 l | INTRODUCTION                                            | 13–1  |

|--------|---------------------------------------------------------|-------|

| 13.2 l | DIAGNOSTICS AND SUPPORT PROGRAMS                        | 13-1  |

| 13.3 I | RUNNING EVDWC AND EVDYE                                 | 13-2  |

| 13.4 I | EVGDB                                                   | 13-3  |

| 13.4.1 | Modifying EVGDB Flags                                   | 13-6  |

| 13.4.2 | Updating the EEPROM Firmware (VAX 9000 System) $\ldots$ | 13-8  |

| 13.5 l | DIAGNOSTIC PATCH MECHANISM 1                            | 13–10 |

|        |                                                         |       |

# 14 DEMNA Console Monitor Program

| 14.1 OVERVIEW                                   | 14-1    |

|-------------------------------------------------|---------|

| 14.2 CONNECTING TO THE CONSOLE MONITOR PROGRAM. | 14-2    |

| 14.2.1 Using the Physical Console               | 14-2    |

| 14.2.2 Using the Network Control Program (NCP)  | 14-2    |

| 14.2.3 Using the Console Connection Program     | 14-4    |

| 14.3 INVOKING AND EXITING THE CONSOLE           | 14–5    |

| 14.4 CONSOLE COMMANDS                           | 14-6    |

| 14.5 CONSOLE CONTROL KEYS                       | 14-9    |

| 14.6 DEMNA STATUS SCREENS                       | 14-11   |

| 14.7 DEMNA NETWORK SCREEN                       | 14 - 25 |

# 15 DEMNA Adapter Registers

| 15.1   | INTRODUCTION 15–1                                             |

|--------|---------------------------------------------------------------|

| 15.2   | REGISTER TYPES 15-2                                           |

| 15.3   | REGISTER BIT DESCRIPTION CONVENTIONS 15-4                     |

| 15.4   | XMI ARCHITECTURE REGISTERS 15-4                               |

| 15.4.1 | XMI Device Register (XDEV, bb+0000) 15–5                      |

| 15.4.2 | 8                                                             |

| 15.4.3 | XMI Failing Address Register (XFADR, bb+0008) 15–10           |

| 15.4.4 | XMI Communication Register (XCOMM, bb+00010) 15-11            |

| 15.4.5 | XMI Failing Address Extension Register (XFAER, bb+002C)       |

| 15.5   | PORT SPECIFIC, XMI VISIBLE REGISTERS 15–15                    |

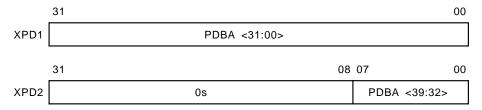

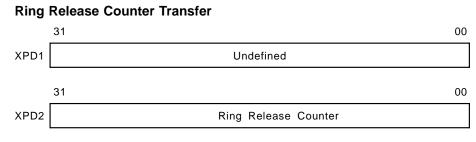

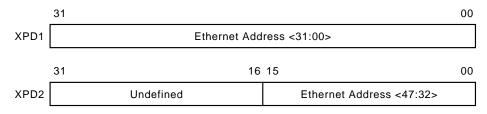

| 15.5.1 | Port Data Registers (XPD1, bb+00100; XPD2, bb+00104) . 15–16  |

| 15.5.2 | Port Status Register (XPST, bb+00108) 15–19                   |

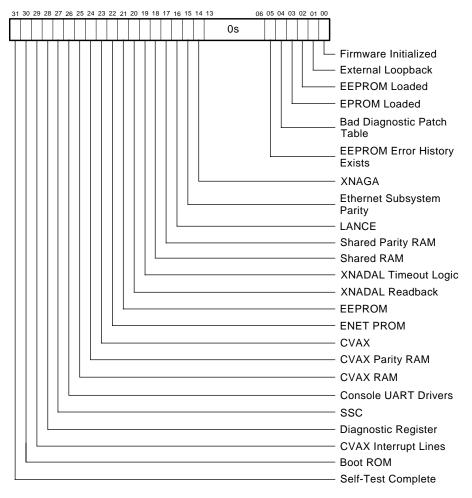

| 15.5.3 | Power-Up Diagnostic Register (XPUD, bb+010C) 15–22            |

| 15.5.4 | Port Control Initialization Register (XPCI, bb+00110) 15-25   |

| 15.5.5 | Port Control Poll Register (XPCP, bb+00114) 15–26             |

| 15.5.6 | Port Control Shutdown Register (XPCS, bb+00118) 15-26         |

| 15.6   | NODE-PRIVATE REGISTERS 15–26                                  |

| 15.6.1 | Gate Array Control and Status Register (GACSR) 15-27          |

| 15.6.2 | Gate Array Host Interrupt Register (GAHIR) 15–32              |

| 15.6.3 | Gate Array IDENT Vector Register (GAIVR) 15-32                |

| 15.6.4 | Gate Array Timer Register (GATMR)                             |

| 15.6.5 | Datamove Port Address Registers (DMPORn) 15–33                |

| 15.6.6 | Datamove Control and Status Registers (DMCSRn) 15-33          |

| 15.6.7 | Datamove XMI Address Register (DMXMIn) 15-33                  |

| 15.6.8 | Datamove Next Page Address Register                           |

| 15.6.9 | Peek XMI Low Address Register (PKXMILn)15-34                  |

| 15.6.1 | $\mathbf{U}$                                                  |

| 15.6.1 | 1 Peek Data A and Peek Data B Registers (PKDATAn,<br>PKDATBn) |

Contents ix

# 16 DEMNA Sequencing Flows

| 16.1 | POWER-UP/RESET SEQUENCE    | 16-1 |

|------|----------------------------|------|

| 16.2 | NODE HALT/RESTART SEQUENCE | 16-1 |

| 16.3 | PORT SHUTDOWN              | 16-2 |

# 17 DEMNA Error Handling

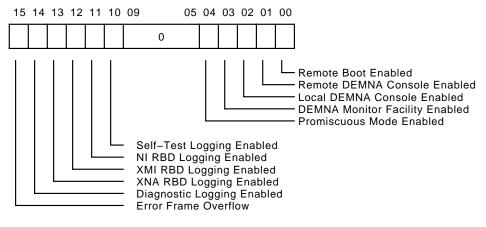

| 17.1   | Introduction                           | 17–1  |

|--------|----------------------------------------|-------|

| 17.2   | Error Types                            | 17–1  |

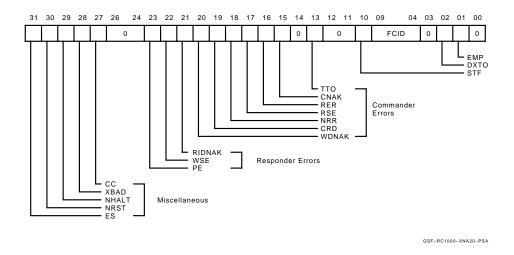

| 17.3   | Error Blocks                           | 17–3  |

| 17.4   | ERROR LOGGING                          | 17–7  |

| 17.4.1 | History Entry Header                   | 17-8  |

| 17.4.2 | History Data Entries                   | 17–11 |

| 17.5   | ERROR RESPONSE                         | 17–16 |

| 17.6   | Restarting the Port from a Fatal Error | 17–22 |

# Part IV DWMBA Adapter Section

## 18 DWMBA ADAPTER OVERVIEW

| 18.1 | INTRODUCTION         | 18-1 |

|------|----------------------|------|

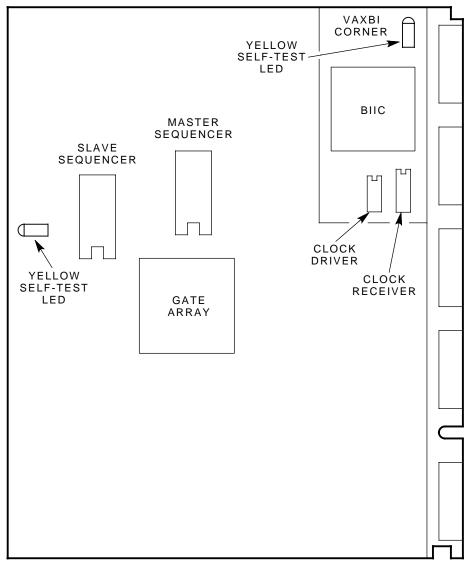

| 18.2 | PHYSICAL DESCRIPTION | 18-1 |

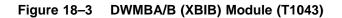

| 18.3 | FUNCTIONAL OVERVIEW  | 18-6 |

| 18.4 | REFERENCE DOCUMENTS  | 18–7 |

## **19 DWMBA CONFIGURATIONS**

| 19.1 | INTRODUCTION     | 19–1 |

|------|------------------|------|

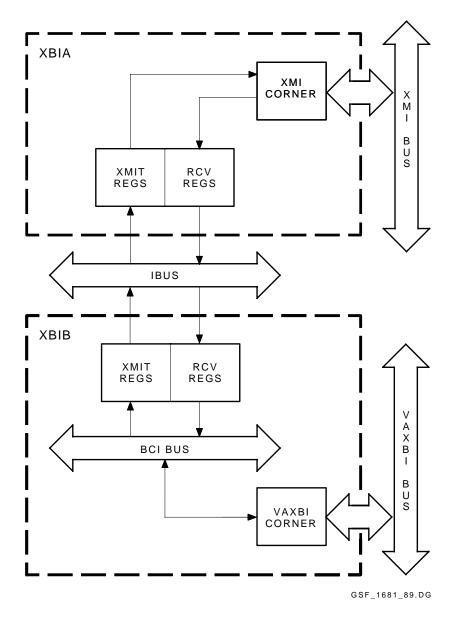

| 19.2 | MODULE PLACEMENT | 19–1 |

| 19.3 | CABLING          | 19-3 |

#### x Contents

# 20 DWMBA DIAGNOSTICS

| 20.1 INTRODUCTION                | 20-1 |

|----------------------------------|------|

| 20.2 POWER-UP SELF-TESTS         | 20-1 |

| 20.3 ROM-BASED DIAGNOSTICS (RBD) | 20-4 |

| 20.3.1 RBD Monitor               | 20-4 |

| 20.3.2 Sample RBD Runs           | 20-6 |

| 20.4 LOOPBACK TESTS              | 20-7 |

# 21 DWMBA REGISTERS AND IBUS SIGNALS

| 21.1 II | NTRODUCTION                                                                    | 21-1    |

|---------|--------------------------------------------------------------------------------|---------|

| 21.2 D  | WMBA REGISTER TYPES                                                            | 21-2    |

| 21.3 R  | EGISTER DESCRIPTION CONVENTIONS                                                | 21-5    |

| 21.4 X  | MI ARCHITECTURE REGISTERS                                                      | 21–6    |

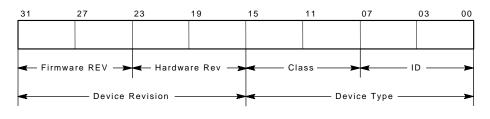

| 21.4.1  | XMI Device Type Register (XDEV, bb+00000)                                      | 21-6    |

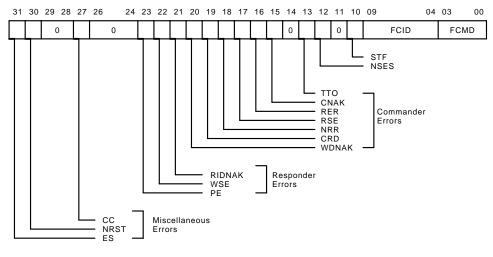

| 21.4.2  | XMI Bus Error Register (XBE, bb+00004)                                         | 21-8    |

| 21.4.3  | XMI Failing Address Register (XFADR, bb+00008)                                 | 21-12   |

| 21.5 D  | WMBA/A RESIDENT NODE SPECIFIC REGISTERS                                        | 21-13   |

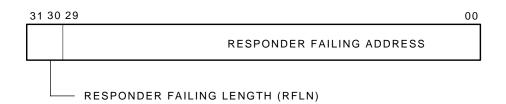

| 21.5.1  | Responder Error Address Register (AREAR, bb+000C)                              | 21-13   |

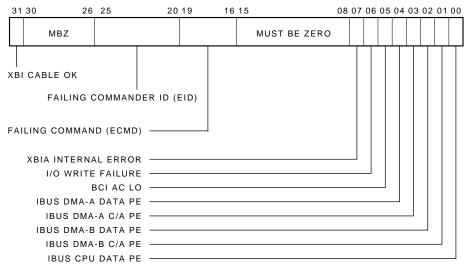

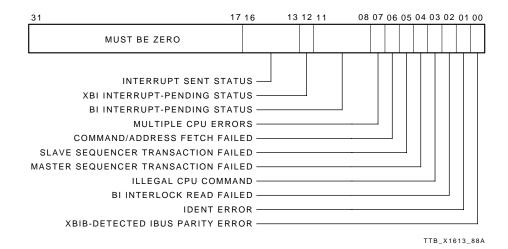

| 21.5.2  | Error Summary Register (AESR, bb+0010)                                         | 21-14   |

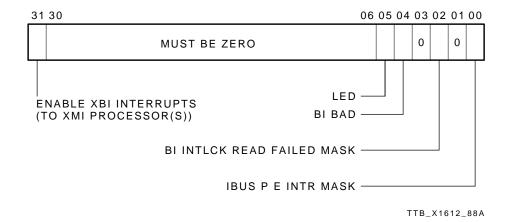

| 21.5.3  | Interrupt Mask Register (AIMR, bb+0014)                                        | 21-17   |

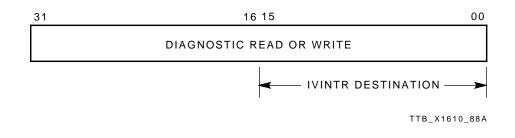

| 21.5.4  | Implied Vector Interrupt Destination/Diagnostic Register<br>(AIVINTR, bb+0018) | 21–20   |

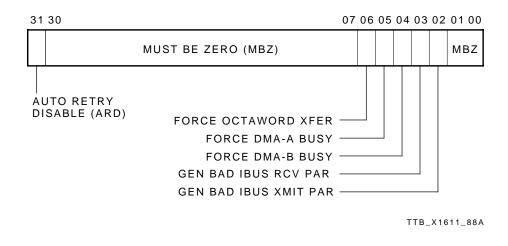

| 21.5.5  | Diagnostic Control Register 1 (ADG1, bb+001C)                                  | 21-21   |

| 21.6 D  | WMBA/B RESIDENT NODE SPECIFIC REGISTERS                                        | 21-23   |

| 21.6.1  | Control and Status Register (BCSR, bb+0040)                                    | 21-23   |

| 21.6.2  | Error Summary Register (BESR bb+0044)                                          | 21 - 25 |

| 21.6.3  | Interrupt Destination Register (BIDR, bb+0048)                                 | 21–29   |

| 21.6.4  | Timeout Address Register (BTIM, bb+004C)                                       | 21-30   |

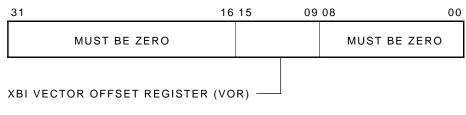

| 21.6.5  | Vector Offset Register (BVOR, bb+0050)                                         | 21-31   |

| 21.6.6  | Vector Register (BVR, bb+0054)                                                 | 21-32   |

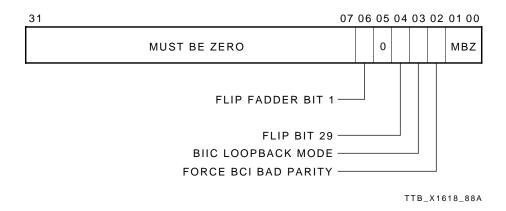

| 21.6.7  | Diagnostic Control Register 1 (BDCR1, bb+0058)                                 |         |

| 21.7 V  | AXBI REGISTERS                                                                 | 21-35   |

| 21.8 II | BUS SIGNALS                                                                    | 21-37   |

|         |                                                                                |         |

Contents xi

I

# Examples

| 7–1  | Invoking the RBD User Interface                  | 7-4   |

|------|--------------------------------------------------|-------|

| 7–2  | Sample RBD Error Report                          | 7-6   |

| 7–3  | Sample RBD Run With Failure (VAX 6000 System)    | 7–7   |

| 7–4  | Sample RBD Run With Failure (VAX 9000 System)    | 7–8   |

| 8-1  | VAX/DS Attach and Select for CIXCD               | 8-6   |

| 8-2  | Sample PARAMETER.PAR File                        | 8-17  |

| 8-3  | Sample PATTERN.PTN File                          | 8-18  |

| 12-1 | Running DEMNA Self-Tests from the System Console | 12-3  |

| 12-2 | Sample DEMNA RBD Error Report                    | 12-14 |

| 12–3 | DEMNA Error Log Reader                           | 12-15 |

| 20-1 | Power-up Self-Test Display (No Errors)           | 20-2  |

| 20-2 | Power-up Self-Test Display (With Errors)         | 20-3  |

| 20-3 | DWMBA RBD Run With No Errors                     | 20-6  |

| 20-4 | DWMBA RBD Run With Errors                        | 20-6  |

# Figures

| 1–1  | Typical System — XMI Bus as the Primary System Bus                | 1–2  |

|------|-------------------------------------------------------------------|------|

| 1–2  | Typical System — XMI Bus as an I/O Bus                            | 1–3  |

| 2–1  | XMI Card Cage Rear View, Showing Node ID Numbers andDaughter Card | 2–2  |

| 2-2  | XMI Card Cage, VAX 9000 System                                    | 2-3  |

| 2–3  | I/O Header Pins                                                   | 2-4  |

| 2-4  | XMI Corner Functional Layout                                      | 2-6  |

| 3–1  | XMI Address Space                                                 | 3–1  |

| 3-2  | I/O Space                                                         | 3-2  |

| 3–3  | Data Transfer Command/Address Cycle — XMI Signals                 | 3–9  |

| 3-4  | Octaword Write Bus Cycles                                         | 3-10 |

| 3–5  | Octaword Read Command/Address Cycle                               | 3–11 |

| 3-6  | Octaword Read, Read Response Data Cycles                          | 3-12 |

| 3–7  | Interlock Read Transaction                                        | 3-13 |

| 3-8  | Unlock Write Transaction                                          | 3-14 |

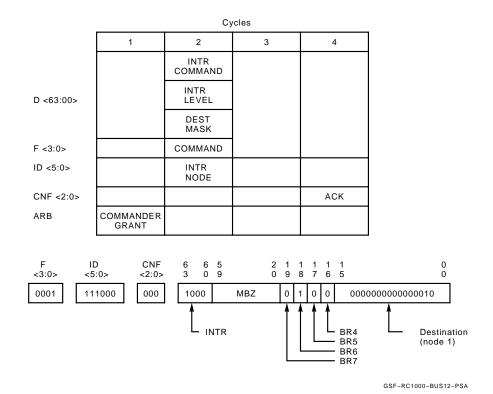

| 3–9  | INTR Transaction                                                  | 3-16 |

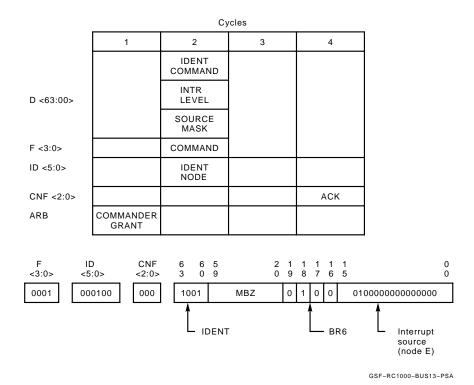

| 3–10 | IDENT Transaction                                                 | 3–17 |

| 3–11 | IDENT Response                                                    | 3-18 |

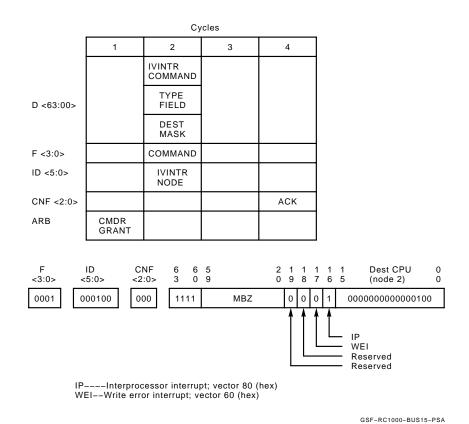

| 3-12 | IVINTR Transaction                                                | 3-19 |

#### xii Contents

1

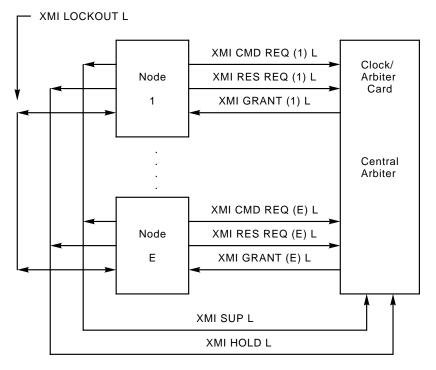

| 3–13  | Arbitration Block Diagram                                 | 3-20  |

|-------|-----------------------------------------------------------|-------|

| 3-14  | Initialization Flowchart                                  | 3–21  |

| 5-1   | CIXCD Interface in a VAXcluster                           | 5 - 2 |

| 5 - 2 | CIXCD Functional Block Diagram                            | 5 - 3 |

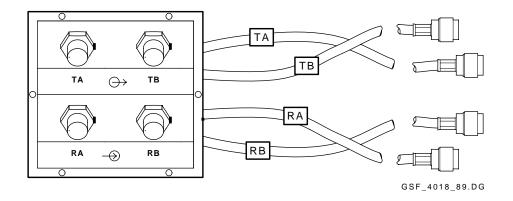

| 6-1   | XMI Cardcage — VAX 9000 System Implementation             | 6-3   |

| 6-2   | CIXCD-AA Bulkhead Cable                                   | 6-4   |

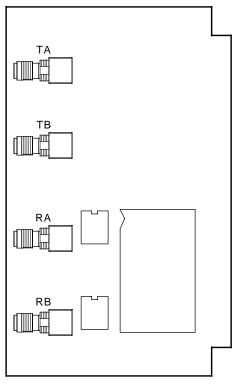

| 6-3   | CIXCD Header Assembly                                     | 6-5   |

| 6-4   | CIXCD Configuration Jumpers                               | 6-6   |

| 8-1   | Diagnostic Loopback Cable Connections                     | 8-5   |

| 8-2   | EVGAC Program Parameter Register                          | 8-12  |

| 8-3   | EEPROM Memory Map                                         | 8-22  |

| 9-1   | XMI Node Space Addressing                                 | 9–3   |

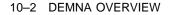

| 10-1  | DEMNA Option in an XMI System                             | 10-2  |

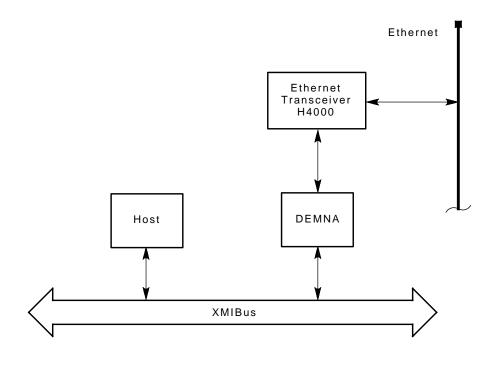

| 10-2  | DEMNA Logic Subsystems                                    | 10-4  |

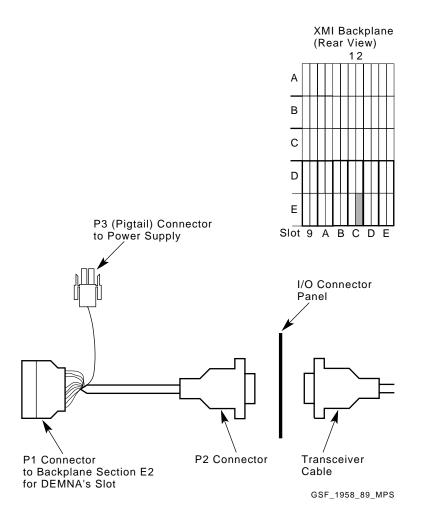

| 11–1  | Internal Ethernet Cable Connections                       | 11-4  |

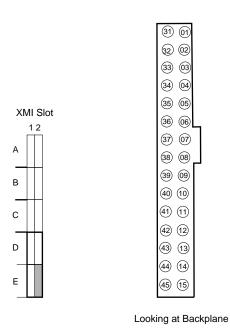

| 11-2  | Internal Ethernet Cable, P1 Connector Pinouts             | 11-6  |

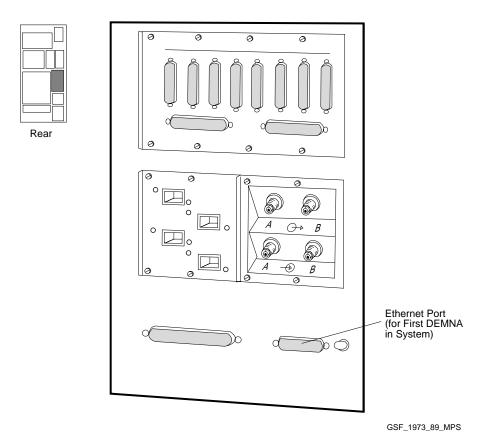

| 11-3  | VAX 6000 Model 400 System Interconnect Panel              | 11–7  |

| 11-4  | Internal Ethernet Cable, P2 Connector Pinouts             | 11-8  |

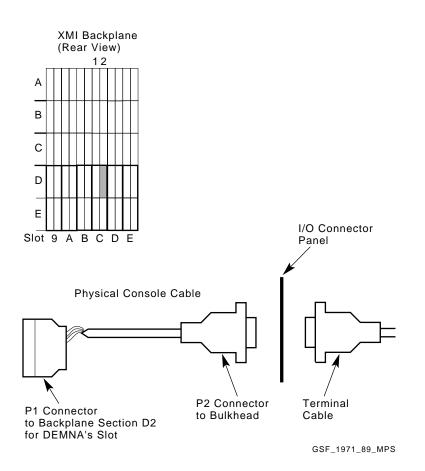

| 11–5  | Internal Cable for Physical Console, Connections          | 11–9  |

| 11-6  | Internal Cable for Physical Console, P1 Connector Pinouts | 11–10 |

| 11–7  | Internal Cable for Physical Console, P2 Connector Pinouts | 11–11 |

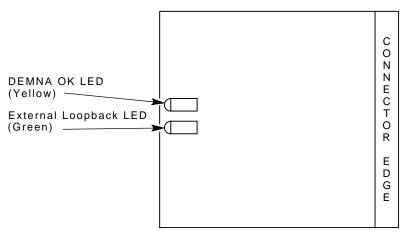

| 12-1  | DEMNA LED Locations                                       | 12-2  |

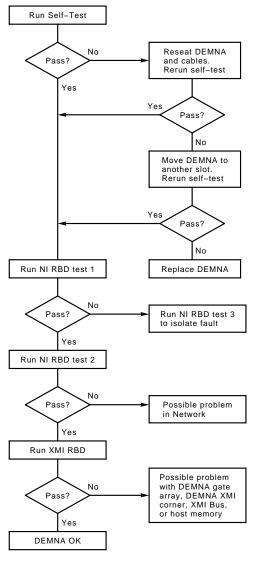

| 12-2  | DEMNA RBD Troubleshooting Flowchart                       | 12–19 |

| 14-1  | DEMNA Status Screens                                      | 14–11 |

| 14-2  | DEMNA Network Screen                                      | 14–25 |

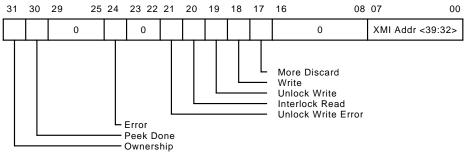

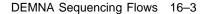

| 16-1  | DEMNA Power-Up and Node Reset                             | 16-3  |

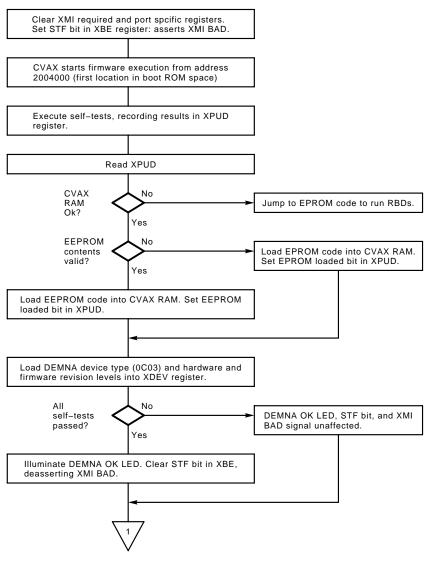

| 16-2  | DEMNA Node Halt/Restart                                   | 16-5  |

| 16-3  | DEMNA Shutdown                                            | 16-6  |

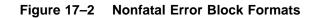

| 17–1  | Fatal Error Block Formats                                 | 17–4  |

| 17–2  | Nonfatal Error Block Formats                              | 17–5  |

| 17–3  | EEPROM History Data Area                                  | 17–7  |

| 17–4  | History Entry Header                                      | 17–9  |

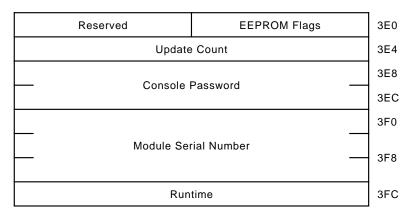

| 17–5  | EEPROM Flags                                              | 17–10 |

| 17-6  | History Entry Format For Diagnostic Errors                | 17–12 |

| 17–7  | History Entry Format for All Other Errors                 | 17–14 |

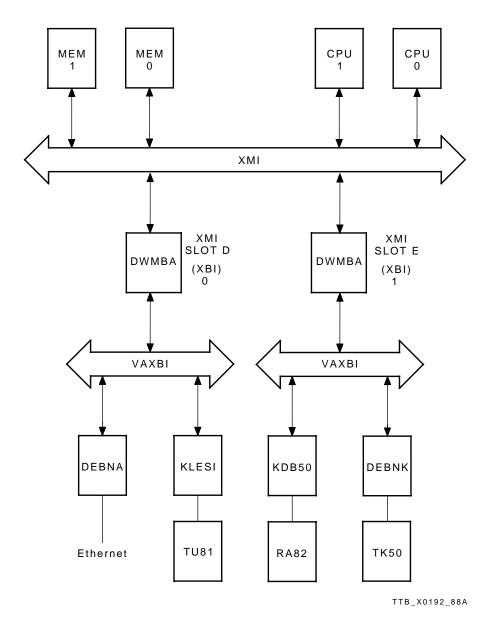

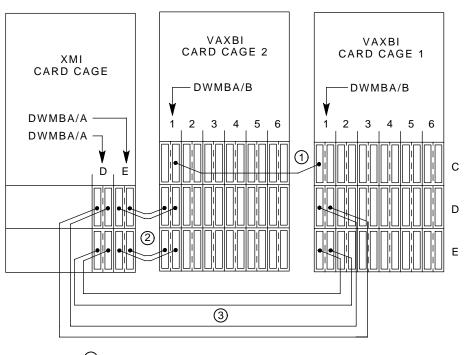

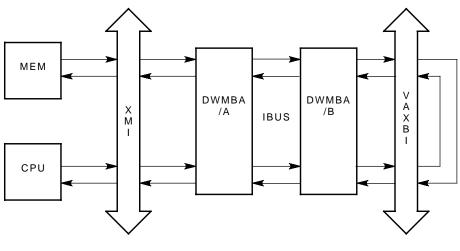

| 18-1  | DWMBA Adapters in a Typical System                        | 18-2  |

L

#### Contents xiii

Γ

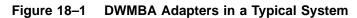

| 18-2 | DWMBA/A (XBIA) Module (T2012)   | 18-3 |

|------|---------------------------------|------|

| 18–3 | DWMBA/B (XBIB) Module (T1043)   | 18-4 |

| 18-4 | DWMBA Functional Logic Elements | 18-5 |

| 19–1 | XMI and VAXBI Cardcages         | 19–2 |

| 19–2 | DWMBA Cabling                   | 19-4 |

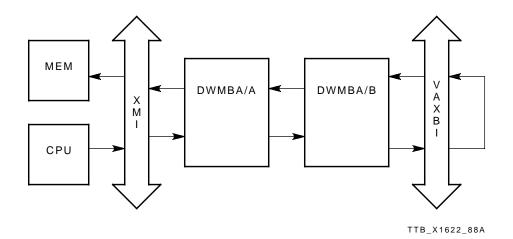

| 20-1 | VAXBI Loopback Data Path        | 20-7 |

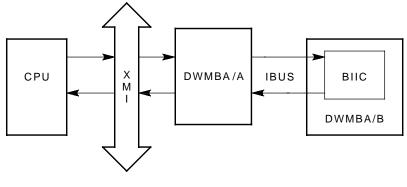

| 20-2 | CPU Write Loopback Data Path    | 20-8 |

| 20-3 | CPU Read Loopback Data Path     | 20-8 |

|      |                                 |      |

# Tables

| 1–1 | XMI Bus Specifications                                                | 1-4  |

|-----|-----------------------------------------------------------------------|------|

| 1–2 | XMI Bandwidth                                                         | 1–5  |

| 1–3 | XMI Architecture Terms                                                | 1–5  |

| 3–1 | XMI I/O Space Regions                                                 | 3–3  |

| 3-2 | XMI Nodespace and I/O Space Allocations                               | 3-4  |

| 3–3 | XMI Bus Signals                                                       | 3–5  |

| 3-4 | XMI Function Codes                                                    | 3–7  |

| 3–5 | Data Transfer Transactions                                            | 3-8  |

| 3-6 | Interrupt Transactions                                                | 3-15 |

| 3–7 | Required and Recommended Registers                                    | 3-22 |

| 4-1 | XMI Bus Transaction Timeouts                                          | 4-2  |

| 5-1 | CIXCD Logic Element Descriptions                                      | 5-5  |

| 5-2 | CIXCD Specifications                                                  | 5-7  |

| 5-3 | CI Bus Specifications                                                 | 5-9  |

| 6-1 | CI Node Address Jumpers                                               | 6-7  |

| 6-2 | Boot Time Jumpers                                                     | 6-8  |

| 6–3 | Disable Arbitration, Extend Header, and Extend ACK<br>Timeout Jumpers | 6–9  |

| 6-4 | Alter Delta (Quiet Slot) Time Jumpers                                 | 6-9  |

| 6–5 | Cluster Size Jumpers                                                  | 6-10 |

| 7–1 | XCDST Indications After Power Up or XMI Reset                         | 7–1  |

| 7–2 | XCDST Diagnostics                                                     | 7–2  |

| 7–3 | CIXCD RBD Sample Tests List                                           | 7–3  |

| 7–4 | RBD Commands                                                          | 7–4  |

| 7–5 | RBD START Command Qualifiers                                          | 7–5  |

| 7–6 | RBD Control Keys                                                      | 7–5  |

|     |                                                                       |      |

| 7–7   | RBD Error Report Levels                                                                | 7-6     |

|-------|----------------------------------------------------------------------------------------|---------|

| 8-1   | CIXCD Macrodiagnostics                                                                 | 8-2     |

| 8-2   | EVGAA Event Flags                                                                      | 8-8     |

| 8-3   | EVGAB Event Flags                                                                      | 8-9     |

| 8-4   | EVGAC Event Flags                                                                      | 8-11    |

| 8-5   | EVGAC Program Parameter Register Bit Descriptions                                      | 8-13    |

| 8-6   | EVGAC Program Parameters                                                               | 8-14    |

| 8–7   | EVGAC Support Files                                                                    | 8-16    |

| 8-8   | PARAMETER.PAR File Structure                                                           | 8-17    |

| 8-9   | EVGEA Program Sections                                                                 | 8-20    |

| 8-10  | VAXcluster System Maintenance Tools                                                    | 8-23    |

| 9-1   | CIXCD Register Types                                                                   | 9-2     |

| 9–2   | CIXCD XMI Visible Registers                                                            | 9-4     |

| 9–3   | IB Accessible Register Locations                                                       | 9-6     |

| 9-4   | Internal Registers                                                                     | 9–7     |

| 9–5   | PCQ0CR (bb+01028) to PMTECR (bb+01054)                                                 | 9-43    |

| 11-1  | DEMNA-M Option Package Contents                                                        | 11–1    |

| 11-2  | Cabinet Kits                                                                           | 11-2    |

| 11-3  | T2020 Module Placement in XMI Cardcage                                                 | 11–3    |

| 11-4  | Internal Ethernet Cable Connectors                                                     | 11–5    |

| 11-5  | Internal Ethernet Cable, P1 Connector Signals                                          | 11-6    |

| 11-6  | Internal Ethernet Cable, P2 Connector Signals                                          | 11-8    |

| 11–7  | Internal Cable for Physical Console, Connectors                                        | 11–9    |

| 11-8  | Internal Cable for Physical Console, P1 Connector Signals                              | 11-10   |

| 11-9  | Internal Cable for Physical Console, P2 Connector Signals                              | 11–11   |

| 12-1  | DEMNA Self-test Indications After Power-up or XMI Reset $% \mathcal{A}_{\mathrm{A}}$ . | 12-1    |

| 12-2  | DEMNA RBDs                                                                             | 12-4    |

| 12–3  | DEMNA Self-Test (RBD 0)                                                                | 12–5    |

| 12-4  | DEMNA RBD Commands                                                                     | 12-6    |

| 12–5  | DEMNA RBD START Command Qualifiers                                                     | 12-8    |

| 12-6  | DEMNA RBD START Command Parameters                                                     | 12-10   |

| 12–7  | DEMNA RBD Deposit/Examine Command Qualifiers                                           | 12–11   |

| 12-8  | DEMNA RBD Deposit/Examine Commnad Special                                              |         |

|       | Addressing Characters                                                                  |         |

|       | DEMNA RBD Control Keys                                                                 |         |

| 12-10 | DEMNA RBD Error Report Levels                                                          | 12 - 14 |

1

Contents xv

| 13–1  | DEMNA Macrodiagnostics and Support Programs 13-1                      |

|-------|-----------------------------------------------------------------------|

| 13-2  | EVGDB Distribution Media 13-3                                         |

| 13-3  | EVGDB Sections 13-4                                                   |

| 13-4  | EVGDB Event Flags 13-4                                                |

| 13–5  | DEMNA EEPROM User-Modifiable Flags and Parameters 13-5                |

| 14-1  | DEMNA Console Commands 14-6                                           |

| 14-2  | DEMNA Console SHOW Command Parameters 14-8                            |

| 14-3  | DEMNA Console Control Keys 14–10                                      |

| 14-4  | DEMNA Status and Status/Interval Screens—Parameter                    |

|       | Definitions                                                           |

| 14–5  | DEMNA Status/Error Screen—Parameter Definitions 14–19                 |

|       | DEMNA Network Screen—Parameter Definitions 14–25                      |

| 15-1  | DEMNA XMI Visible Registers 15–2                                      |

| 15-2  | DEMNA Node-Private Registers 15–3                                     |

| 17–1  | EEPROM History Data Entries 17-8                                      |

| 17–2  | History Entry Header Fields 17-9                                      |

| 17–3  | EEPROM Flags 17–10                                                    |

| 17–4  | History Entry Fields for Diagnostic Errors                            |

| 17–5  | History Entry Fields for All Other Errors 17–15                       |

| 17-6  | Error Response Keys                                                   |

| 17–7  | Response To Ethernet Errors                                           |

| 17-8  | Response To Internal Errors that Affect the LANCE 17–19               |

| 17–9  | Response to Hardware Errors that Affect the CVAX $\ldots \ldots 1720$ |

| 17-10 | Response to XMI Related Errors                                        |

| 18-1  | DWMBA Transactions 18-6                                               |

| 19–1  | XMI Node/VAXBI Card Cage Configurations 19-3                          |

| 19–2  | DWMBA Cables 19–5                                                     |

| 20-1  | DWMBA RBD Tests                                                       |

| 21-1  |                                                                       |

| 21-2  | VAXBI Architecture Registers 21-4                                     |

# **About This Manual**

#### **Intended Audience**

This handbook is for VAX system trained Digital customer service personnel who service XMI-based systems and subsystems. Users of this handbook should be familiar with the XMI bus architecture (either through the *XMI Bus Concepts* course or through practical experience) and have a minimum of level 1 hardware maintenance training on one or more VAX systems (for example, VAX 6000 or VAX 9000 systems).

#### **Document Scope and Structure**

This handbook provides a single, quick reference source to the type of information most frequently required to service XMI adapters. The handbook is divided into three parts.

Part 1 overviews the XMI bus architecture and describes the XMI physical and functional characteristics.

Part 2 covers the CIXCD interface and Part 3 covers the DWMBA adapter. The information in Parts 2 and 3 includes XMI adapter:

- Block diagrams

- Configurations

- Maintenance features

- Diagnostics

- Register bit maps and descriptions

xii DIGITAL INTERNAL USE ONLY

#### Conventions

| addresses | All addresses are given in hexadecimal (hex).                                                                                                                                                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bits      | All bit numbers are given in decimal with the bit(s) enclosed in angle brackets; for example $<31>$ .                                                                                                                                                                |

|           | Multiple individual bits or bit fields are separated by commas<br>with bit fields indicated by two numbers separated by a colon.<br>For example <31:24,20,18,14:10> indicates bits 31 through 24<br>(inclusive), bit 20, bit 18, and bits 14 through 10 (inclusive). |

| CTRL/x    | Specifies to press and hold the $Ctrl$ key while pressing the key; for example, $CTRL/C$ .                                                                                                                                                                           |

| [item]    | Indicates the item is optional. The horizontal ellipsis indicates that additional optional items can be entered.                                                                                                                                                     |

|           | In examples, tables, or figures, indicates that not all information is shown.                                                                                                                                                                                        |

| •         |                                                                                                                                                                                                                                                                      |

#### **Related Documents**

This handbook was written in conjunction with XMI adapter specific user's guides and technical descriptions. Each adapter specific section (Parts 2 and 3) contains a list of documents which the user can reference for more detailed information.

# Part I XMI Bus Section

This part of the handbook introduces the XMI bus and briefly describes the main features of the XMI architecture. Topics in this section include XMI bus:

- Specifications

- Terms

- Transactions

- Maintenance features

# 1 XMI BUS OVERVIEW

# 1.1 INTRODUCTION

The XMI bus is a limited length, synchronous, high-speed bus with centralized arbitration. The XMI bus is pended (XMI nodes do not hold the bus waiting for a response) with multiplexed address and data lines.

Multiple transactions can be in progress at any time on the XMI, with arbitration and data transfer transactions occurring simultaneously.

# **1.2 IMPLEMENTATIONS**

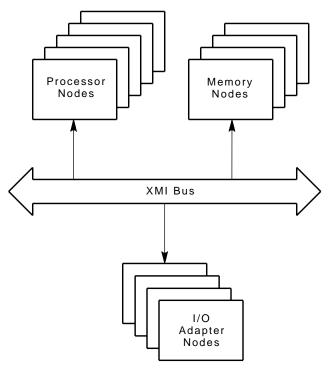

The XMI bus can be implemented as the primary system bus (for example, in most VAX 6000 systems) or as an I/O bus (for example, in VAX 9000 systems).

When used as the primary system bus, the XMI can support multiple processors, memory subsystems, and I/O adapters, in a variety of configurations, to a maximum of 14 nodes.

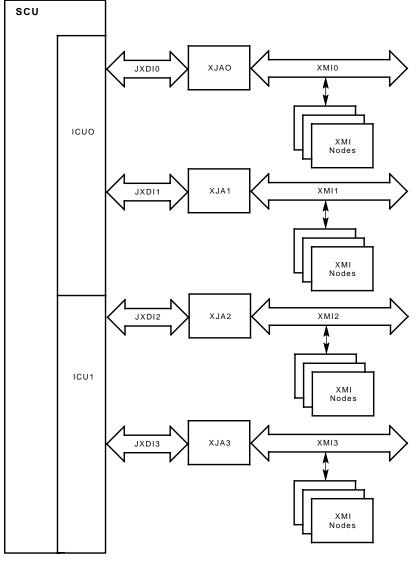

When used as an I/O bus, the XMI is interfaced to the system by way of an adapter. For example, in VAX 9000 systems, the XMI bus interfaces to the system by way of the XJA adapter, JXDI bus, and an I/O control unit.

Figures 1–1 and 1–2 show typical XMI bus implementations.

1-2 XMI BUS OVERVIEW

GSF\_1733\_89.DG

Figure 1–1 Typical System — XMI Bus as the Primary System Bus

XMI BUS OVERVIEW 1-3

Γ

GSF\_4016\_89.DG

# Figure 1–2 Typical System — XMI Bus as an I/O Bus

# 1.3 SPECIFICATIONS AND TERMINOLOGY

#### Table 1–1 XMI Bus Specifications

| Physical                        |                                    |

|---------------------------------|------------------------------------|

| Backplane                       | 14-slot card cage                  |

| Nodes <sup>1</sup>              | Maximum of 14                      |

| Node ID                         | Hardwired to physical slot         |

| Bus length                      | Fixed, nonexpandable               |

| Technology                      | CMOS                               |

| Performance                     |                                    |

| Bus type                        | Synchronous                        |

| Bus cycle                       | 64 ns                              |

| Address/data lines <sup>2</sup> | 64                                 |

| Address bits                    | 40                                 |

| Address space                   | 1 terabyte (2 <sup>40</sup> bytes) |

| Data transfer size              | 64 bits/cycle                      |

| Data transfer type <sup>3</sup> | Pended                             |

| Bandwidth                       | See Table 1–2                      |

| Arbitration                     |                                    |

| Type                            | Centralized                        |

| Algorithm                       | Modified round-robin               |

| Cycles <sup>4</sup>             | Concurrent with data transfers     |

| Queues                          | Two — commander, responder         |

$^1\mathrm{The}$  XMI architecture allows for up to 16 nodes, but current physical constraints limit the bus to 14 nodes.

$^2 {\rm Multiplexed}$  address/data lines.

$^3{\rm Read}\text{-}$  and interrupt-type transactions are pended (node does not hold bus while waiting for a response).

$^{4}\mathrm{No}$  dedicated arbitration cycles.

| Data Size             | <b>Read</b> <sup>1</sup> | Write <sup>1</sup> |

|-----------------------|--------------------------|--------------------|

| Longword <sup>2</sup> | 31.25                    | 31.25              |

| Quadword              | 62.5                     | 62.5               |

| Octaword              | 83.3                     | 83.3               |

| Hexword               | 100.0                    | 100.0              |

Table 1–2 XMI Bandwidth

$^1Bandwidth$  values given in MBytes/s.

$^2{\rm The}$  XMI architecture allows data transfers of all data sizes to both memory and I/O space. However, some implementations may not support transfers greater than a longword to I/O space.

Table 1–3 XMI Architecture Terms

| Term                                                                                                                                    | Definition                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Node Hardware device that connects to the XMI backplane.<br>can consist of one or more modules, but only one mod<br>have an XMI corner. |                                                                                                                                                                                                                                                                                                                                 |

| Transfer                                                                                                                                | Smallest unit of information exchange that occurs on the XMI bus. For example, the command and data cycles of a read transaction and the command and data cycles of a write transaction are transfers.                                                                                                                          |

| Transaction                                                                                                                             | One or more transfer cycles which comprise the XMI task<br>being performed. For example, a read transaction consists of<br>a command transfer followed some time later by a return data<br>transfer.                                                                                                                            |

| Commander                                                                                                                               | Node that initiated the current transaction.                                                                                                                                                                                                                                                                                    |

|                                                                                                                                         | In a write transaction, the commander node is the source of the<br>data to be transferred. In a read transaction, the commander is<br>the node that requested the data.                                                                                                                                                         |

|                                                                                                                                         | A node which initiates a transaction is considered to be the<br>commander for the duration of the transaction. For example,<br>on a read transaction, the commander initiates the transaction<br>and the responder returns the data. During the return data<br>transfer, the requesting node is still considered the commander. |

| Responder                                                                                                                               | Node which is the target of a transaction request.                                                                                                                                                                                                                                                                              |

#### 1-6 XMI BUS OVERVIEW

Table 1–3 (Cont.) XMI Architecture Terms

| Term                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter          | Node that is the source of the data on the bus.                                                                                                                                                                                                                                                                                                                                                                                    |

|                      | For example, on a read transaction, the commander is the transmitter during the command transfer and the responder is the transmitter on the return data transfer.                                                                                                                                                                                                                                                                 |

| Receiver             | Node that is the target of the data on the bus.                                                                                                                                                                                                                                                                                                                                                                                    |

| Naturally<br>aligned | Data quantity whose address is an offset, from the beginning of memory, of an integral number of data elements of the same size.                                                                                                                                                                                                                                                                                                   |

|                      | The low order address bits of naturally aligned data items are<br>always zero. All XMI bus read and write transfers occur on<br>naturally aligned blocks of data.                                                                                                                                                                                                                                                                  |

| Wraparound<br>read   | Octaword or hexaword read operation in which read data is<br>returned so that the originally requested quadword is returned<br>first, independent of alignment. The remaining data in the<br>naturally aligned block of data which contains the addressed<br>quadword is returned in subsequent transfers. XMI bus<br>protocol requires that all octaword and hexaword reads, both<br>normal and interlocked, be wraparound reads. |

# **1.4 BUS INTEGRITY FEATURES**

The XMI bus contains several features that enhance the integrity and reliability of the bus.

- Parity protection for all bus information transfer lines

- ECC protection on all bus confirmation signals

- Bus protocol permits detection and correction of single-bit errors

- Defined timeout conditions to detect and diagnose faults

# **2** XMI BUS PHYSICAL DESCRIPTION

# 2.1 XMI CARD CAGE

The XMI card cage consists of a 14-slot backplane, connectors, card guides, and structural members. Each slot has a ZIF connector which is opened and closed by a cam actuator mechanism. This mechanism is sometimes called the card cage handle.

#### 2.1.1 Node ID Numbers

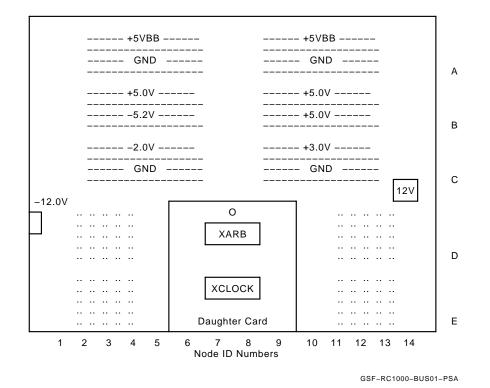

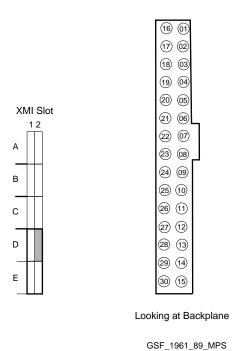

XMI node ID numbers are hardwired on the XMI backplane. The node numbers correspond to the backplane slot numbers as shown in Figure 2-1.

#### 2.1.2 Clock/Arbiter Card

In VAX 6000 systems, the XMI system clock and bus arbiter are located on a daughter card (DCARD) which is attached to the XMI backplane. The location of the daughter card is indicated in Figure 2–1.

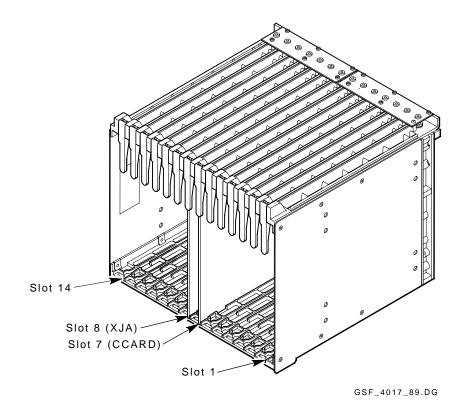

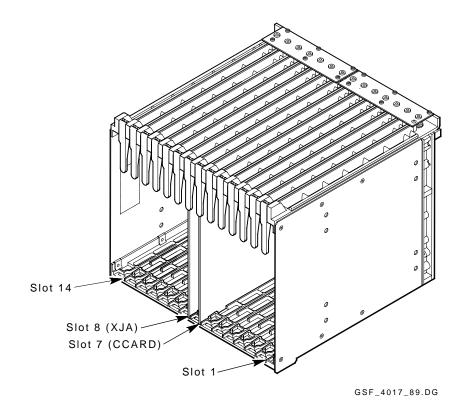

In VAX 9000 systems, the clock/arbiter module (CCARD) is mounted in slot 7 of the card cage (Figure 2–2).

#### 2-2 XMI BUS PHYSICAL DESCRIPTION

Figure 2–1 XMI Card Cage Rear View, Showing Node ID Numbers and Daughter Card

### XMI BUS PHYSICAL DESCRIPTION 2-3

Figure 2–2 XMI Card Cage, VAX 9000 System

2-4 XMI BUS PHYSICAL DESCRIPTION

#### 2.1.3 I/O Header Pins

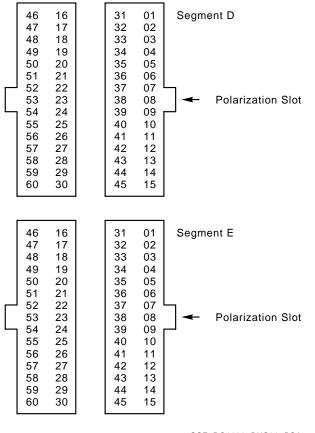

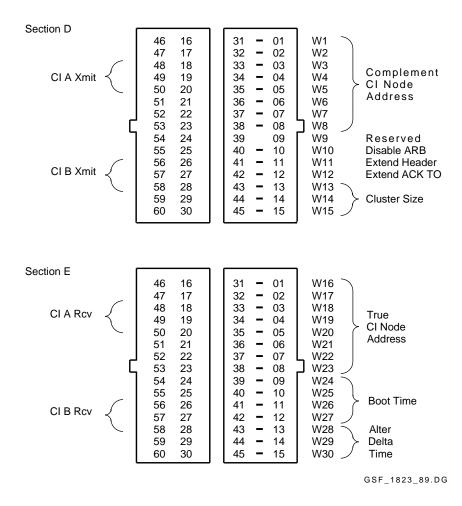

Figure 2–3 shows the I/O header pins which are provided in segments D and E of each XMI backplane slot for attaching I/O cables.

GSF-RC1000-BUS02-PSA

Figure 2–3 I/O Header Pins

# 2.2 XMI NODE

An XMI node consists of one or more modules that are mounted in the XMI card cage and interface to the XMI bus via the XMI corner. If the node consists of more than one module, only one may have an XMI corner.

#### 2.2.1 XMI Corner

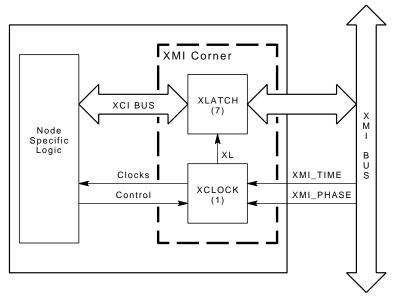

The XMI corner contains custom logic that:

- Assures a standard electrical interface to the XMI bus

- Buffers drive signals to the XMI bus

- · Buffers receive signals from the XMI bus

The XMI corner occupies an area of approximately 4.45 cm (1.75 in)  $\times$  12.70 cm (5.00 in) on the module and consists of eight Digital custom CMOS I chips:

- Seven XLATCH chips

- One XCLOCK chip

Figure 2–4 is a functional block diagram of the XMI corner. Note that the XMI corner does not perform any node control functions. All node control functions are performed by the node-specific logic.

#### 2.2.2 Self-Test LED

XMI nodes are required to have one yellow LED to indicate the result of the node's self-test. This LED lights when self-test passes. The LED is located on the front edge of the module (the edge opposite the connectors) and is the only yellow LED on the module.

# 2.3 CONFIGURATION RULES

The XMI backplane design places certain restrictions on the placement of modules in the XMI cardcage as described below.

#### 2-6 XMI BUS PHYSICAL DESCRIPTION

GSF\_1734\_89.DG

#### Figure 2–4 XMI Corner Functional Layout

#### VAX 6000 Systems

- Slot 1 or E must contain a (non-memory) module

- No I/O adapter modules in slots 5 to A

- CPU modules are typically installed beginning with slot 1

- Memory modules are placed in slots A to 5, then in slots B and C

- DWMBA adapters are installed in the left side of the card cage, beginning with slot E

XMI BUS PHYSICAL DESCRIPTION 2-7

### VAX 9000 Systems

- Slot 1 or E must contain a (non-memory) module

- CCARD module is installed in slot 7

- XJA module is installed in slot 8

- First I/O adapter is installed in slot 1 or E

- Additional I/O adapters may be located in any other slot

# **3** XMI BUS FUNCTIONAL DESCRIPTION

## 3.1 ADDRESSING

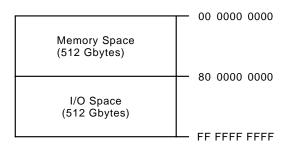

The XMI bus supports one terabyte ( $2^{40}$  bytes) of address space, which is divided into physical memory space and I/O space (Figure 3–1).

Address line <39> selects between memory and I/O space:

<39> = 0 selects memory space <39> = 1 selects I/O space

#### NOTE

# Some implementations of the XMI only support 30-bit addressing. These systems use address bit <29> to distinguish memory space from I/O space.

XMI I/O space is further divided into private space, nodespace, and 15 I/O adapter address space regions. Figure 3–2 shows the I/O space divisions, and Tables 3–1 and 3–2 describe the regions.

GSF-RC1000-BUS03-PSA

#### Figure 3–1 XMI Address Space

#### 3-2 XMI BUS FUNCTIONAL DESCRIPTION

| [                                                                                                                                         | 80 0000 0000                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| XMI Private Space<br>(24 Mbytes)                                                                                                          | 00.0400.0000                                                 |

| XMI Nodespace<br>(16 x 512 Kbytes)                                                                                                        | 80 0180 0000                                                 |

| I/O Adapter 1 Address Space<br>(32 Mbytes)                                                                                                | 80 0200 0000                                                 |

| I/O Adapter 2 Address Space<br>(32 Mbytes)                                                                                                | 80 0400 0000                                                 |

| I/O Adapter 3 Address Space<br>(32 Mbytes)                                                                                                | 80 0600 0000                                                 |

| I/O Adapter 4 Address Space<br>(32 Mbytes)                                                                                                | 80 0800 0000                                                 |

|                                                                                                                                           | 0000 00A0 08                                                 |

|                                                                                                                                           |                                                              |

|                                                                                                                                           |                                                              |

|                                                                                                                                           |                                                              |

| I/O Adapter 11 Address Space<br>(32 Mbytes)                                                                                               | 80 1600 0000                                                 |

|                                                                                                                                           | 80 1600 0000<br>80 1800 0000                                 |

| (32 Mbytes)<br>I/O Adapter 12 Address Space                                                                                               | 80 1600 0000                                                 |

| (32 Mbytes)<br>I/O Adapter 12 Address Space<br>(32 Mbytes)<br>I/O Adapter 13 Address Space<br>(32 Mbytes)                                 | 80 1600 0000<br>80 1800 0000                                 |

| (32 Mbytes)<br>I/O Adapter 12 Address Space<br>(32 Mbytes)<br>I/O Adapter 13 Address Space                                                | 80 1600 0000<br>80 1800 0000<br>80 1A00 0000<br>80 1C00 0000 |

| (32 Mbytes)<br>I/O Adapter 12 Address Space<br>(32 Mbytes)<br>I/O Adapter 13 Address Space<br>(32 Mbytes)<br>I/O Adapter 14 Address Space | 80 1600 0000<br>80 1800 0000<br>80 1A00 0000                 |

GSF-RC1000-BUS04-PSA

Table 3–1

XMI I/O Space Regions

Region

Description

| Region                       | Description                                                                                                                                                                                                                                                              |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Private space                | 24-Mbyte region reserved for operations local to the nodes.<br>References to private space are serviced by resources local<br>to a node, such as local device control and status registers<br>(CSRs) and boot ROM. These references are not broadcast<br>on the XMI bus. |

| Nodespace                    | 16, 512-Kbyte regions for node control and status registers. Table 3–2 shows the address ranges.                                                                                                                                                                         |

| I/O adapter address<br>space | 15, 32-Mbyte regions used for accessing XMI I/O adapters.<br>Address ranges are shown in Table 3–2. Note that node 0<br>does not have an I/O adapter address region.                                                                                                     |

|                       | Nodespace    |              | I/O Adapter Space |              |  |

|-----------------------|--------------|--------------|-------------------|--------------|--|

| Node                  | Begin        | End          | Begin             | End          |  |

| <b>0</b> <sup>1</sup> | 80 0180 0000 | 80 0187 FFFF | _                 |              |  |

| 1                     | 80 0188 0000 | 80 018F FFFF | 80 0200 0000      | 80 03FF FFFF |  |

| 2                     | 80 0190 0000 | 80 0197 FFFF | 80 0400 0000      | 80 05FF FFFF |  |

| 3                     | 80 0198 0000 | 80 019F FFFF | 80 0600 0000      | 80 07FF FFFF |  |

| 4                     | 80 01A0 0000 | 80 01A7 FFFF | 80 0800 0000      | 80 09FF FFFF |  |

| 5                     | 80 01A8 0000 | 80 01AF FFFF | 80 0A00 0000      | 80 0BFF FFFF |  |

| 6                     | 80 01B0 0000 | 80 01B7 FFFF | 80 0C00 0000      | 80 0DFF FFFF |  |

| 7                     | 80 01B8 0000 | 80 01BF FFFF | 80 0E00 0000      | 80 0FFF FFFF |  |

| 8                     | 80 01C0 0000 | 80 01C7 FFFF | 80 1000 0000      | 80 11FF FFFF |  |

| 9                     | 80 01C8 0000 | 80 01CF FFFF | 80 1200 0000      | 80 13FF FFFF |  |

| А                     | 80 01D0 0000 | 80 01D7 FFFF | 80 1400 0000      | 80 15FF FFFF |  |

| В                     | 80 01D8 0000 | 80 01DF FFFF | 80 1600 0000      | 80 17FF FFFF |  |

| С                     | 80 01E0 0000 | 80 01E7 FFFF | 80 1800 0000      | 80 19FF FFFF |  |

| D                     | 80 01E8 0000 | 80 01EF FFFF | 80 1A00 0000      | 80 1BFF FFFF |  |

| Е                     | 80 01F0 0000 | 80 01F7 FFFF | 80 1C00 0000      | 80 1DFF FFFF |  |

| $\mathbf{F}^2$        | 80 01F8 0000 | 80 01FF FFFF | 80 1E00 0000      | 80 1FFF FFFF |  |

Table 3–2 XMI Nodespace and I/O Space Allocations

$^1\mathrm{The}$  nodespace for node 0 is reserved for future expansion. Also, node 0 does not have I/O adapter space; addresses in this range comprise XMI private space and XMI nodespace.

$^{2}\mbox{Reserved}$  for future expansion.

# 3.2 BUS SIGNALS

| Table 3 | –3 XM | Bus   | Signals  |

|---------|-------|-------|----------|

|         | • /   | - Duo | orginalo |

| Signal                   | Description                                                                |

|--------------------------|----------------------------------------------------------------------------|

| Arbitration              |                                                                            |

| XMI CMD REQn             | Commander bus request lines (n = node number)                              |

| XMI RES REQn             | Responder bus request lines (n = node number)                              |

| XMI GRANTn               | Bus grant lines (n = node number)                                          |

| XMI HOLD                 | Bus hold (multicycle transfers)                                            |

| XMI SUP                  | Suppress initiation of new XMI transactions                                |

| XMI LOCKOUT <sup>1</sup> | Prevent resource starvation (forces sequential access to shared resources) |

| Information Transfer     |                                                                            |

| XMI D <63:00>            | Data cycles: read or write date<br>Command cycles: command, address, mask  |

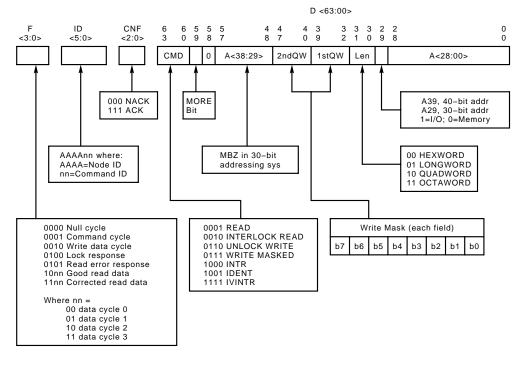

| XMI F <03:00>            | Bus function (see Table 3–4)                                               |

| XMI ID <05:00>           | Commander ID                                                               |

| XMI P <02:00>            | Parity of XMI D, XMI F, and XMI ID lines                                   |

| Response                 |                                                                            |

| XMI CNF <02:00>          | Data transfer status confirmation (from receiver)                          |

| Control                  |                                                                            |

| XMI AC LO                | Low ac line voltage                                                        |

| XMI AC LO | Low ac line voltage                                    |

|-----------|--------------------------------------------------------|

| XMI DC LO | Impending loss of dc power                             |

| XMI BAD   | Node failure (asserted until all nodes pass self-test) |

<sup>1</sup>Commander nodes assert XMI LOCKOUT when repeated attempts to perform hardware locks are denied, or repeated attempts to perform IDENTs or I/O space references are NOACKed. The assertion of LOCKOUT ensures fair access to resources by preventing nodes which have completed a lock, IDENT, or I/O reference from initiating another request while LOCKOUT is asserted. XMI LOCKOUT need only be generated and monitored by commander nodes that perform interlock reads, IDENTs, or I/O space references.

| Signal                   | Description                                                                                       |

|--------------------------|---------------------------------------------------------------------------------------------------|

| Control                  |                                                                                                   |

| XMI DEF [A,B]            | Defaults bus tristate lines during XMI idle cycles                                                |

| XMI ERR DEF              | Bus configuration defaulting check                                                                |

| XMI RESET                | Initialize system to power-up state                                                               |

| XMI TRIGGER <sup>2</sup> | Node detected significant event (specific to node)                                                |

| XMI TIME n               | XMI clock reference $(n = 1 \text{ to } 15)$                                                      |

| XMI PHASE n              | XMI clock phase reference $(n = 1 \text{ to } 15)$                                                |

| XMI UPDATE EN            | Modification control for EEPROM or other writeable,<br>non-volatile storage devices.              |

|                          | UPDATE EN must be observed by all nodes that implement on-board, writeable, non-volatile storage. |

Table 3–3 (Cont.) XMI Bus Signals

| XMI CON XMIT    | Transmit data to console                                         |

|-----------------|------------------------------------------------------------------|

| XMI CON RECV    | Receive data from console                                        |

| XMI CON SECURE  | Console secure (if XMI is system bus, disables CTRL/P detection) |

| XMI BOOT EN     | Auto-boot control (if XMI is system bus)                         |

| XMI RUN         | Front panel RUN LED control                                      |

| XMI TOY BBU PWR | Time of year clock BBU power                                     |

| XMI TOY BBU OK  | TOY clock BBU status                                             |

|                 |                                                                  |

#### Miscellaneous

| XMI NODE ID<br><03:00> | Backplane wired node ID (for example, slot 1 = node 1) |

|------------------------|--------------------------------------------------------|

| XMI SPARE0             | Reserved                                               |

$^2 {\rm This}$  signal may be labeled as XMI FAULT on some implementations of the XMI bus.

$^{3}\text{Used}$  only by CPU nodes

# 3.3 BUS FUNCTION CODES

| XMI F <3:0> |   |   |   |          |                              |

|-------------|---|---|---|----------|------------------------------|

| 3           | 2 | 1 | 0 | Mnemonic | Function                     |

| 0           | 0 | 0 | 0 | NULL     | Null cycle                   |

| 0           | 0 | 0 | 1 | CMD      | Command cycle                |

| 0           | 0 | 1 | 0 | WDAT     | Write data cycle             |

| 0           | 0 | 1 | 1 |          | Reserved (decoded as NULL)   |

| 0           | 1 | 0 | 0 | LOC      | Lock response                |

| 0           | 1 | 0 | 1 | RER      | Read error response          |

| 0           | 1 | 1 | 0 |          | Reserved (decoded as NULL)   |

| 0           | 1 | 1 | 1 |          | Reserved (decoded as NULL)   |

| 1           | 0 | 0 | 0 | GRD0     | Good read data, cycle 0      |

| 1           | 0 | 0 | 1 | GRD1     | Good read data, cycle 1      |

| 1           | 0 | 1 | 0 | GRD2     | Good read data, cycle 2      |

| 1           | 0 | 1 | 1 | GRD3     | Good read data, cycle 3      |

| 1           | 1 | 0 | 0 | CRD0     | Corrected read data, cycle 0 |

| 1           | 1 | 0 | 1 | CRD1     | Corrected read data, cycle 1 |

| 1           | 1 | 1 | 0 | CRD2     | Corrected read data, cycle 2 |

| 1           | 1 | 1 | 1 | CRD3     | Corrected read data, cycle 3 |

Table 3–4 XMI Function Codes

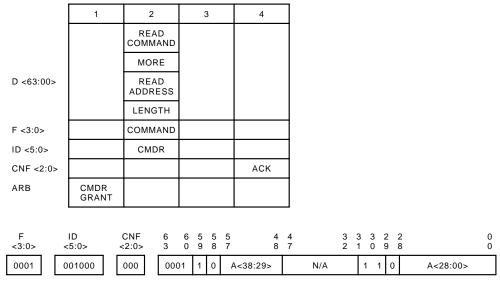

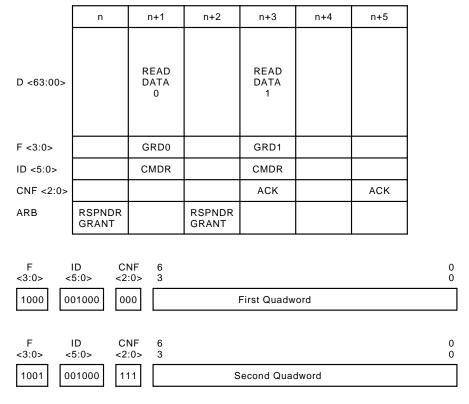

# 3.4 XMI DATA TRANSFER TRANSACTIONS

Table 3–5 Data Transfer Transactions

| Type <sup>1</sup>      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read                   | Moves a longword, quadword, octaword, or hexword of data<br>from the responder to the commander. Data are naturally<br>aligned and delivered in wraparound order. Multiple transfers<br>may be necessary to transfer all of the quadwords in an<br>octaword or hexword transaction.                                                                                                                                                                                                              |

| Interlocked<br>read    | Similar to a read transaction except that a locked bit in<br>memory determines if the data transfer should continue.<br>If the bit is set, signifying that the memory structure is<br>not available, the transaction is terminated and no data is<br>transferred. If the bit is clear, the memory structure is locked<br>from future interlocked transactions and the requested data<br>is returned to the commander. The unlock write masked<br>transaction must be issued to release the lock. |

|                        | Interlock granularity is implementation dependent. The minimum supported granularity in memory space is hexword.                                                                                                                                                                                                                                                                                                                                                                                 |

| Masked write           | Moves specific bytes in a longword, quadword, octaword, or<br>hexword data block from the commander to the responder.<br>The data block is naturally aligned and the bytes to be<br>transferred are identified by a byte mask field.                                                                                                                                                                                                                                                             |

|                        | Write transactions are performed with one, two, or four consecutive data transfer cycles with no NULL cycles in between.                                                                                                                                                                                                                                                                                                                                                                         |

| Unlock write<br>masked | Complement of interlocked read. Writes data to, and releases the lock on, a locked memory location.                                                                                                                                                                                                                                                                                                                                                                                              |

|                        | When a node issues an interlocked read, it must unlock the<br>memory structure when it is finished by issuing an unlock<br>write masked with the data to be written. When memory<br>receives the unlock write masked, it unlocks the memory<br>location and writes the data as requested. If an unlock write<br>masked is directed to a currently unlocked location, memory<br>performs a masked write operation.                                                                                |

$^1{\rm The}$  XMI architecture allows data transfers of all data sizes to both memory and I/O space. However, some implementations may not support transfers greater than a longword to I/O space.

GSF-RC1000-BUS05-PSA

Figure 3–3 Data Transfer Command/Address Cycle — XMI Signals

|           | Bus Cycles    |                            |                    |                    |     |     |

|-----------|---------------|----------------------------|--------------------|--------------------|-----|-----|

|           | 1             | 2                          | 3                  | 4                  | 5   | 6   |

|           |               | WRITE<br>MASKED<br>COMMAND |                    |                    |     |     |

|           |               | MORE                       | WRITE<br>DATA<br>0 | WDITE              |     |     |

| D <63:00> |               | WRITE<br>ADDRESS           |                    | WRITE<br>DATA<br>1 |     |     |

|           |               | WRITE<br>MASK              |                    |                    |     |     |

|           |               | LENGTH                     |                    |                    |     |     |

| F <3:0>   |               | COMMAND                    | WRITE<br>DATA      | WRITE<br>DATA      |     |     |

| ID <5:0>  |               | CMDR                       |                    |                    |     |     |

| CNF <2:0> |               |                            |                    | ACK                | ACK | ACK |

| ARB       | CMDR<br>GRANT | HOLD                       | HOLD               |                    |     |     |

#### 3-10 XMI BUS FUNCTIONAL DESCRIPTION

GSF-RC1000-BUS06-PSA

|            |             |              | Command/Address Cycle                                                                                                                                                       |        |

|------------|-------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| F<br><3:0> | ID<br><5:0> | CNF<br><2:0> | 6       6       5       5       4       4       3       3       2       2         3       0       9       8       7       8       7       2       1       0       9       8 | 0<br>0 |

| 0001       | 001000      | 000          | 0111 1 0 A<38:29> All 1s 1 1 0 A<28:0>                                                                                                                                      |        |

|            |             |              | Write Data Cycles                                                                                                                                                           |        |

| F<br><3:0> | ID<br><5:0> | CNF<br><2:0> | 6<br>3                                                                                                                                                                      | 0<br>0 |

| 0010       | 001000      | 000          | First Quadword                                                                                                                                                              |        |

| F<br><3:0> | ID<br><5:0> | CNF<br><2:0> | 6<br>3                                                                                                                                                                      | 0<br>0 |

| 0010       | 001000      | 111          | Second Quadword                                                                                                                                                             |        |

GSF-RC1000-BUS07-PSA

### Figure 3–4 Octaword Write Bus Cycles

GSF-RC1000-BUS08-PSA

Figure 3–5 Octaword Read Command/Address Cycle

#### 3-12 XMI BUS FUNCTIONAL DESCRIPTION

GSF-RC1000-BUS09-PSA

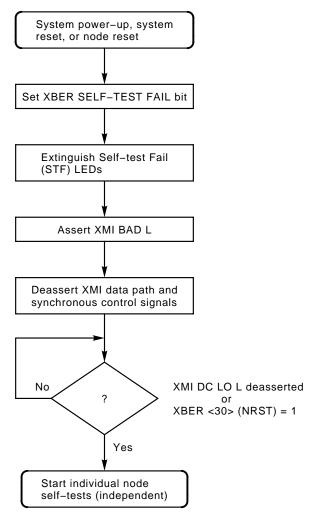

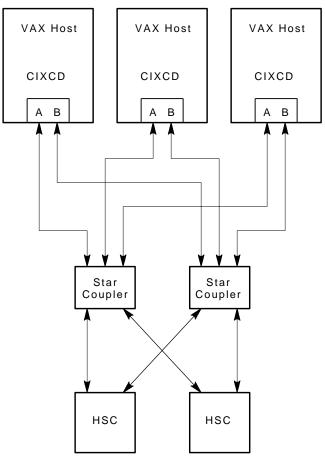

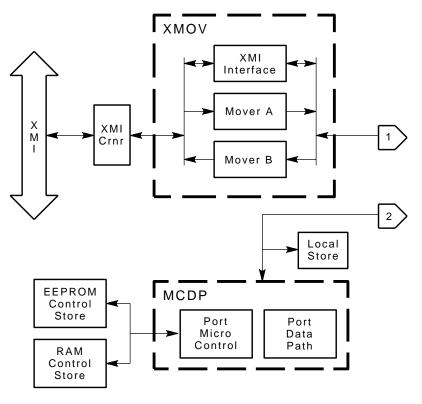

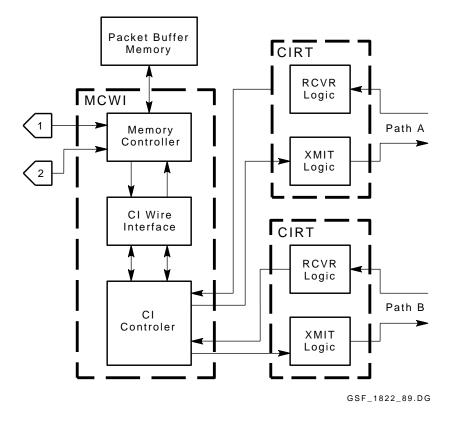

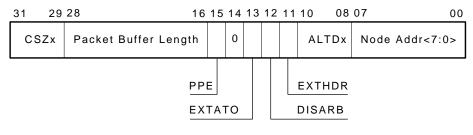

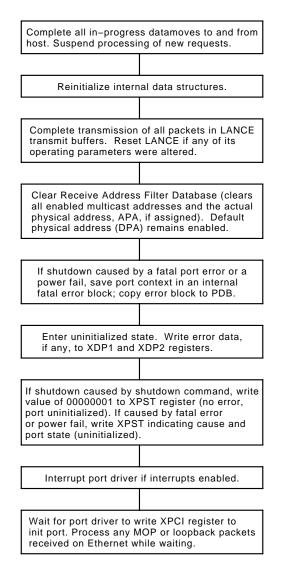

#### Figure 3–6 Octaword Read, Read Response Data Cycles