DEC MicroServer Manufacturing and Repair Manual

DIGITAL INTERNAL USE ONLY

First printing, January 1989

# Copyright (c) 1989 by Digital Equipment Corporation All Rights Reserved

The reproduction of this material, in whole or in part, is strictly prohibited. For copy information, contact your local Digital Sales Office.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

### The following are trademarks of Digital Equipment Corporation:

| digital DATATRIEVE DEC DECmate DECnet DECset DECsystem-10 | DECtape DECUS DECWriter DIBOL MASSBUS PDP P/OS | Rainbow<br>RSTS<br>RSX<br>UNIBUS<br>VAX<br>VMS<br>VT |

|-----------------------------------------------------------|------------------------------------------------|------------------------------------------------------|

| DECSYSTEM-20                                              | Professional                                   | Work Processor                                       |

#### CONTENTS

Preface

| PART I  |             | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER | <b>1</b>    | The DEC MicroServer and its Uses                                                                                                                                                                                                                                                                                                                                                                      |

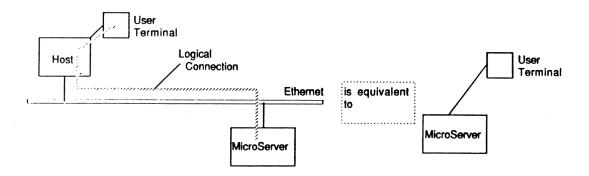

|         | 13          | What is the DEC MicroServer?                                                                                                                                                                                                                                                                                                                                                                          |

| CHAPTER | 2           | Major Components and Specifications                                                                                                                                                                                                                                                                                                                                                                   |

|         | 2.5.1 2.5.2 | Overview                                                                                                                                                                                                                                                                                                                                                                                              |

| PART II |             | FUNCTIONAL AND CIRCUIT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

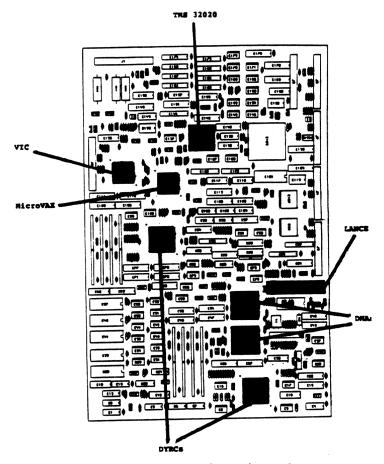

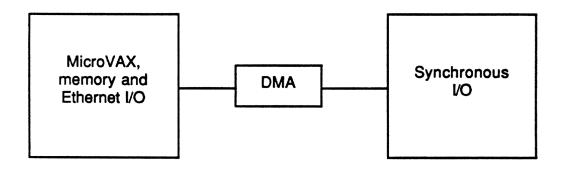

| CHAPTER | 3           | System Architecture                                                                                                                                                                                                                                                                                                                                                                                   |

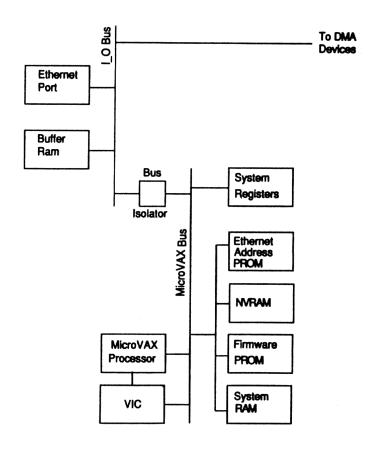

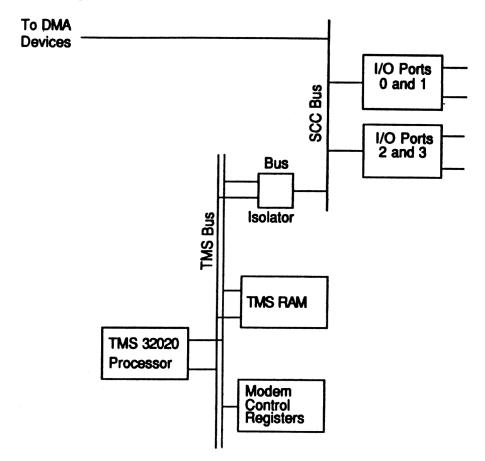

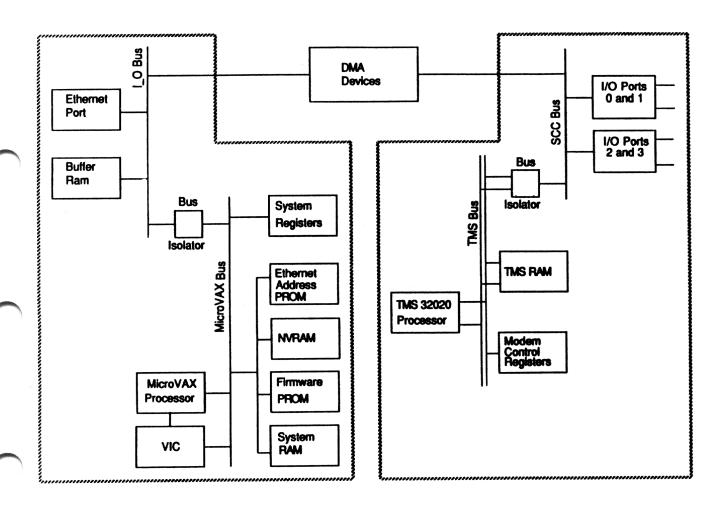

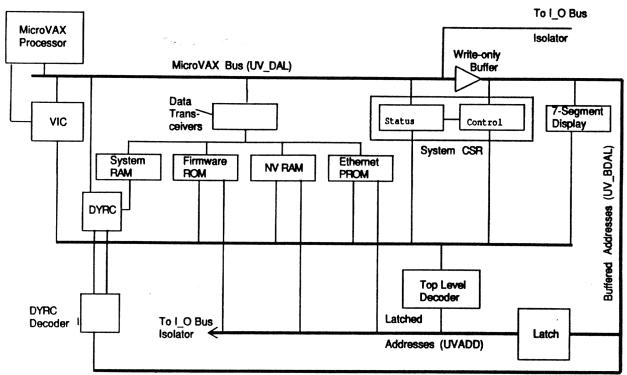

|         | 3.2.1       | Overview       3-1         General Architecture       3-1         MicroVAX Side       3-2         MicroVAX Bus       3-3         I_O Bus       3-3         Why Two Buses?       3-3         Synchronous I/O Side       3-4         SCC Bus       3-5         TMS Bus       3-5         Why Two Buses?       3-5         Position of the DMA Devices       3-5         Complete Architecture       3-6 |

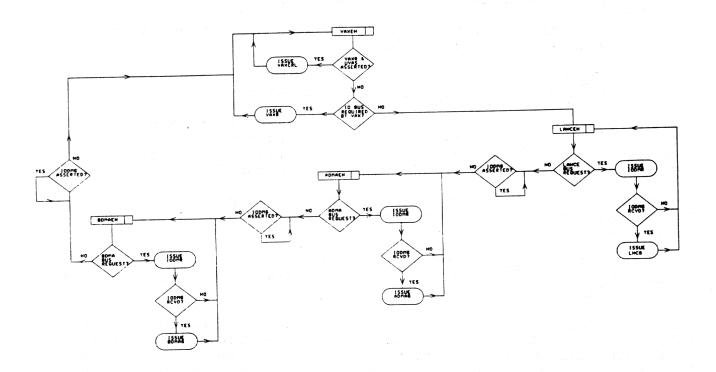

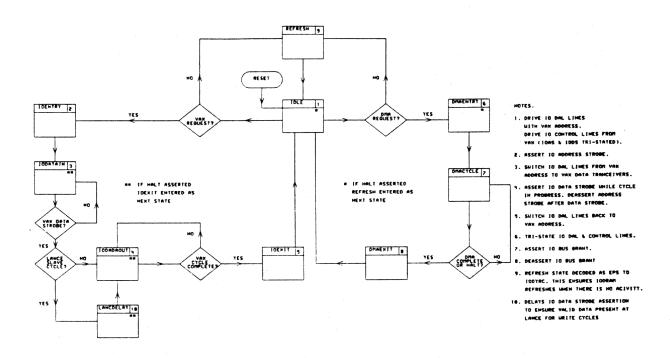

|         | 3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.4.1<br>3.4.1.1<br>3.4.1.2<br>3.4.1.3<br>3.4.1.4<br>3.4.2<br>3.4.3<br>3.4.4.3<br>3.4.4.3<br>3.4.4.3 | System Initialization            | 3-8<br>3-9<br>3-9<br>3-10<br>3-10<br>3-11<br>3-11<br>3-12<br>3-13<br>3-13<br>3-14<br>3-14 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------|

| CHAPTER | 4                                                                                                                                      | The MicroVAX and I_O Buses       |                                                                                           |

|         | 4.1                                                                                                                                    | Overview                         | 4-1                                                                                       |

|         | 4.2                                                                                                                                    | Bus Structures                   | 4-1                                                                                       |

|         | 4.3                                                                                                                                    | Bus Structures                   | 4-3                                                                                       |

|         | 4.3.1                                                                                                                                  | Address Space                    | 4 3                                                                                       |

|         | 4.3.2                                                                                                                                  | Address Space                    | 4-5                                                                                       |

|         | 4.3.3                                                                                                                                  | Interrupts and Exceptions        | 4-5                                                                                       |

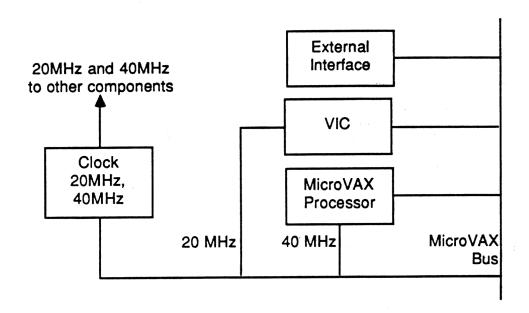

|         | 4.4                                                                                                                                    | System Clocks                    | 4-6                                                                                       |

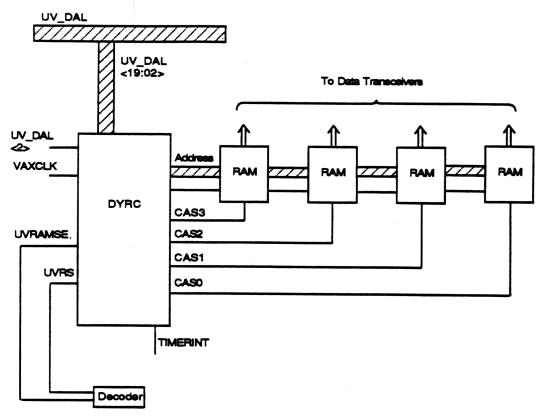

|         | 4.5                                                                                                                                    | System RAM                       | 4-6                                                                                       |

|         | 4.5.1                                                                                                                                  | Memory Element Addressing        | 4-7                                                                                       |

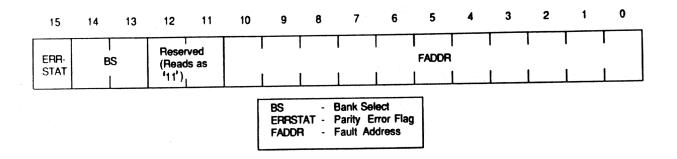

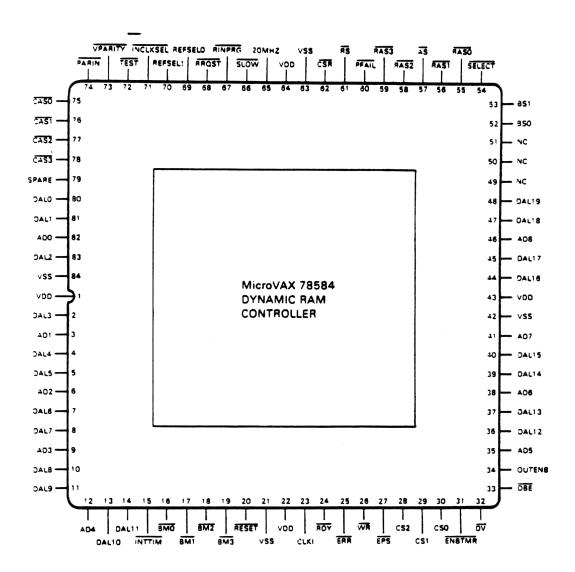

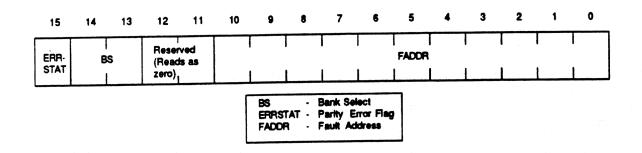

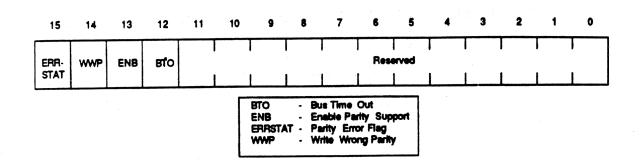

|         | 4.5.2                                                                                                                                  | DYRC Registers                   | 4-8                                                                                       |

|         | 4.5.3                                                                                                                                  | Memory Partitioning              | 4-10                                                                                      |

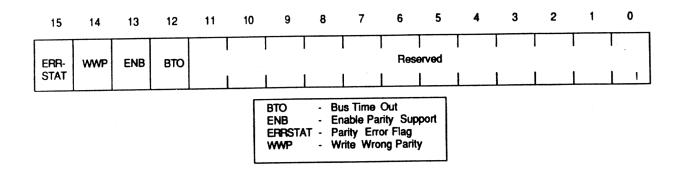

|         | 4.5.4                                                                                                                                  | Parity Checking                  | 4-11                                                                                      |

|         | 4.5.5                                                                                                                                  | Clocks                           | 4-11                                                                                      |

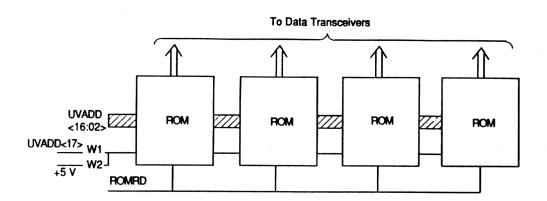

|         | 4.6                                                                                                                                    | Firmware ROM                     | 4-11                                                                                      |

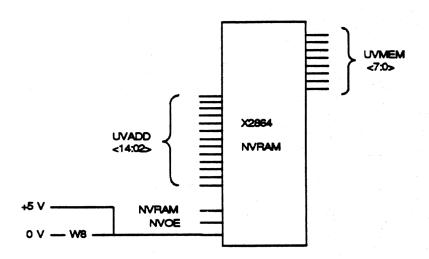

|         |                                                                                                                                        | NVRAM                            | 4-13                                                                                      |

|         | 4.8                                                                                                                                    | NVRAM                            | 4-14                                                                                      |

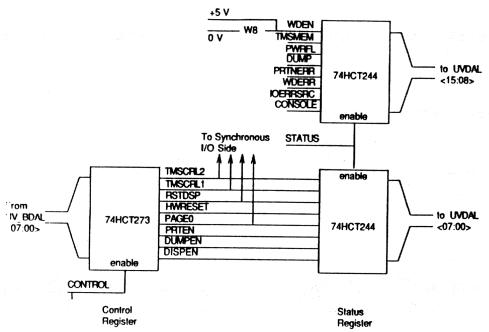

|         | 4.9                                                                                                                                    | System Registers                 | 4-14                                                                                      |

|         | 4.9.1                                                                                                                                  | System Registers                 | 4-15                                                                                      |

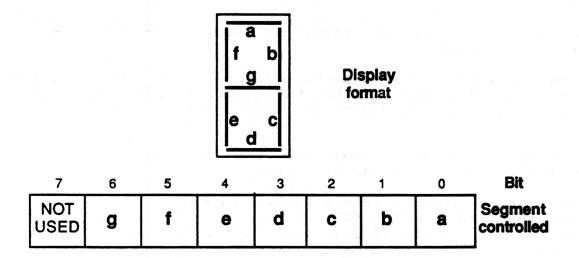

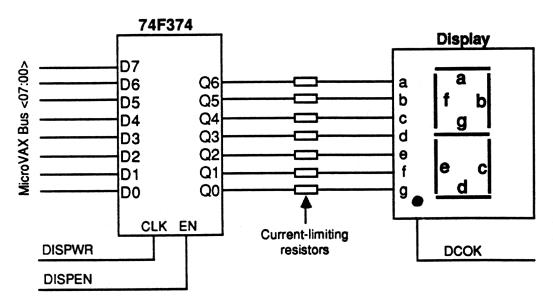

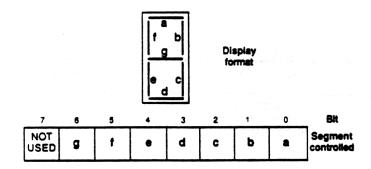

|         | 4.9.2                                                                                                                                  | Display Register                 | 4-20                                                                                      |

|         | 4.10                                                                                                                                   | Address Decoding                 | 4-21                                                                                      |

|         | 4.10.1                                                                                                                                 | MicroVAX Bus                     | 4-21                                                                                      |

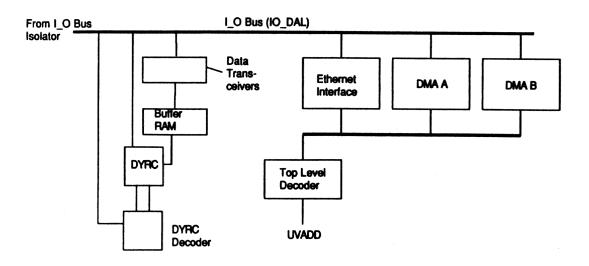

|         | 4.10.2                                                                                                                                 | I_O Bus                          | 4-22                                                                                      |

|         | 4.10.3                                                                                                                                 | I/O Device Access to the I O Bus | 4-22                                                                                      |

|         | 4.11                                                                                                                                   | The I O Bus Isolator             | 4-23                                                                                      |

|         | 4.12                                                                                                                                   | The I_O Bus Isolator             | 4-29                                                                                      |

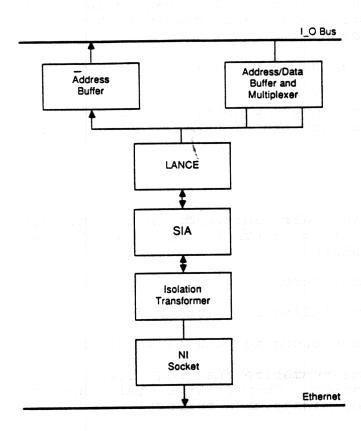

| CHAPTER | 5                                                                                                                                      | Ethernet Interface               |                                                                                           |

|         | 5.1                                                                                                                                    | Overview                         | 5-1                                                                                       |

|         | 5.2     | LANCE                                                 | 5-2  |

|---------|---------|-------------------------------------------------------|------|

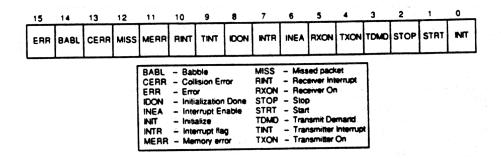

|         | 5.2.1   | Registers                                             | 5-2  |

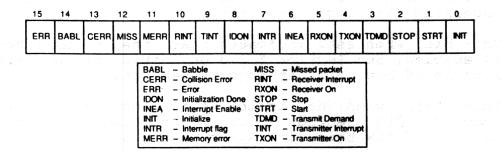

|         | 5.2.1.1 | Device Control and Status Word (CSR0) .               | 5-3  |

|         | 5.2.1.2 | Initialization Block Address (CSB1 and                |      |

|         |         | CSR2)                                                 | 5-5  |

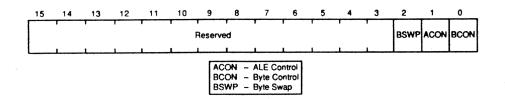

|         | 5.2.1.3 | Bus Master Interface Definition (CSR3)                | 5-6  |

|         | 5.2.2   | Access to the CSRs                                    | 5-7  |

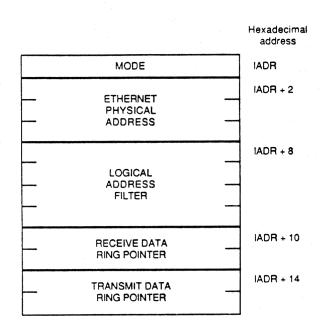

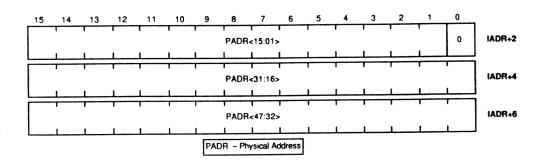

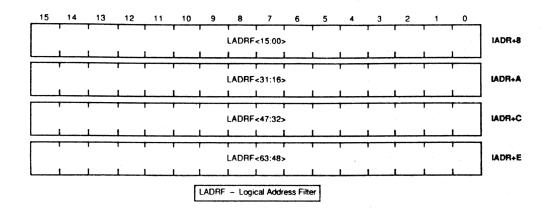

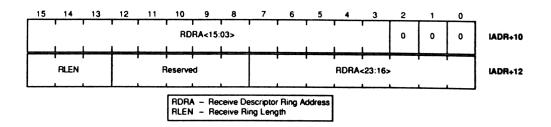

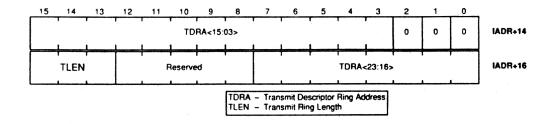

|         | 5.2.3   | Initialization Block                                  | 5-8  |

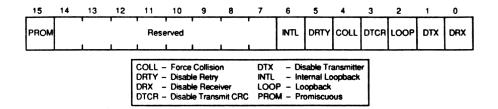

|         | 5.2.3.1 | Mode Field                                            | 5-8  |

|         | 5.2.3.2 | Mode Field                                            | 5-10 |

|         | 5.2.3.3 | Logical Address Filter Field                          | 5-11 |

|         |         | Receive Data Ring Pointer                             |      |

|         | 5.2.3.5 |                                                       | 5-14 |

|         |         | Operation Sequence                                    |      |

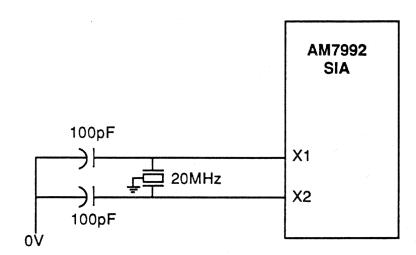

|         | 5.2.3   | SIA                                                   | 5-15 |

|         |         | Bus Multiplexer                                       |      |

|         | 5.4     | Interrupts Generated                                  | 5-17 |

|         | 5.5     | Ethernet Address PROM                                 | 5-17 |

|         | 5.6     | Ethernet Address From                                 | 2-10 |

|         |         |                                                       |      |

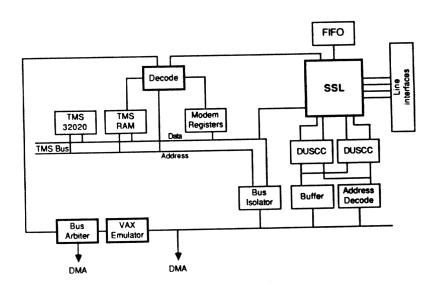

| CHAPTER | 6       | TMS Processor and Synchronous Control                 |      |

|         |         |                                                       |      |

|         | 6.1     | Overview of the Synchronous I/O Logic                 |      |

|         | 6.2     | The TMS 32020 Processor                               |      |

|         | 6.2.1   | Address Spaces                                        |      |

|         | 6.2.2   | Interrupts                                            |      |

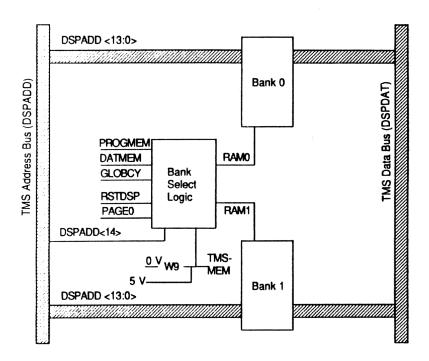

|         | 6.3     | TMS RAM                                               |      |

|         | 6.3.1   | TMS Access With One Memory Bank Fitted                |      |

|         | 6.3.2   | TMS Access With Two Memory Banks Fitted .             | 6-5  |

|         | 6.3.3   | MicroVAX Access                                       |      |

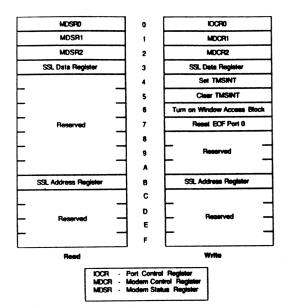

|         | 6.4     | Synchronous Control and Status Registers              | 6-7  |

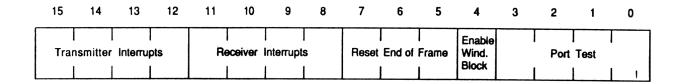

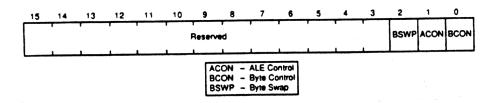

|         | 6.4.1   | Port Control (IOCRO)                                  |      |

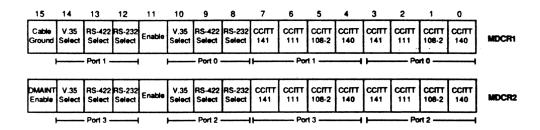

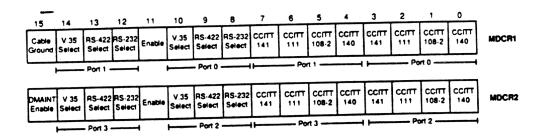

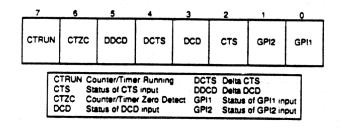

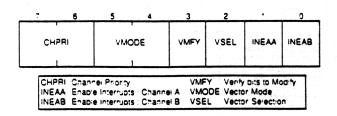

|         | 6.4.2   | Modem Control Registers (MDCR1 and MDCR2)             | 6-11 |

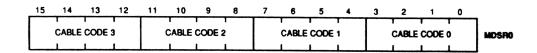

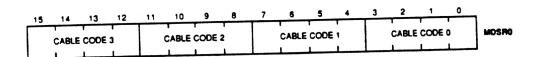

|         | 6.4.3   | Cable Code (MDSR0)                                    | 6-14 |

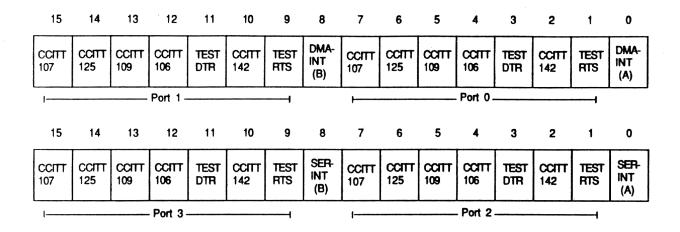

|         | 6.4.4   | Modem Status Registers (MDSR1 and MDSR2) .            | 6-16 |

|         | 6.4.5   | TMS Interrupt Control (TMSINT)                        | 6-18 |

|         | 6.4.6   | TMS Interrupt Control (TMSINT) Window Access Hold-Off | 6-19 |

|         | 6.4.7   | Reset End of Frame 0                                  | 6-19 |

|         | 6.5     |                                                       | 6-20 |

|         | 6.6     | Synchronous I/O Control Block                         | 6-21 |

|         | 6.6.1   | Global Control                                        | 6-23 |

|         |         | Ring Block Address                                    | 6-23 |

|         | 6.6.2   | Ring Block Address                                    | 6-23 |

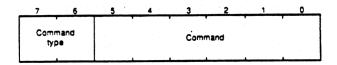

|         | 6.6.3   | Port Command Registers                                | 6-25 |

|         | 6.6.4   | mvc Processor Alive Counter                           | 6-27 |

|         | 6.6.5   | TMS Processor Alive Counter                           | 6-27 |

|         | 6.6.6   | Port Status Registers                                 | 6-20 |

|         | 6.6.7   | Modem Masks                                           | 6-31 |

|         | 6.6.8   | Modem Control and Status Registers                    | 6-33 |

|         | 6.6.9   | Port Initialization Blocks                            | 6-34 |

|         | 6.6.9.1 |                                                       | 6-34 |

|         | 6692    | Station Address                                       | ロースじ |

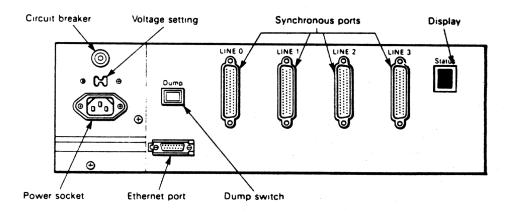

| CHAPTER | 7        | Synchronous I/O ports                                           |      |

|---------|----------|-----------------------------------------------------------------|------|

|         | 7.1      | Overview                                                        | 7-1  |

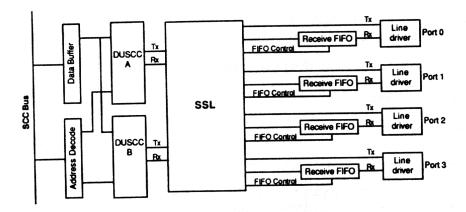

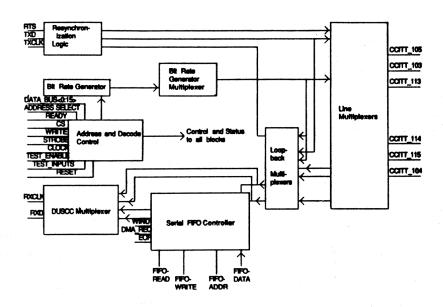

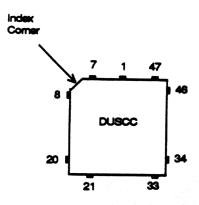

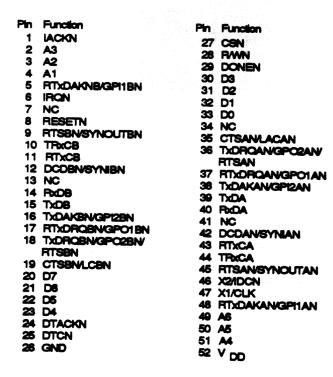

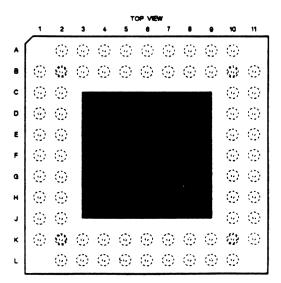

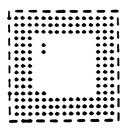

|         | 7.2      | DUSCC                                                           | 7-2  |

|         | 7.2.1    | Registers                                                       |      |

|         | 7.2.2    | Types of Register                                               | 7-3  |

|         | 7.2.3    | Register Addressing                                             | 7-6  |

|         | 7.2.4    | Register Usage                                                  | 7-7  |

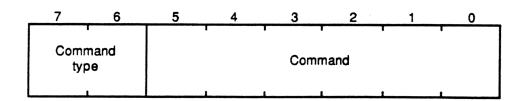

|         | 7.2.5    | Channel Command Register (CCR)                                  | 7-7  |

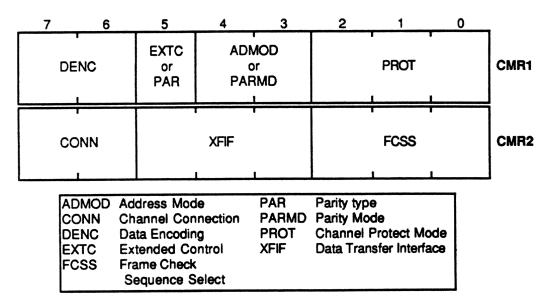

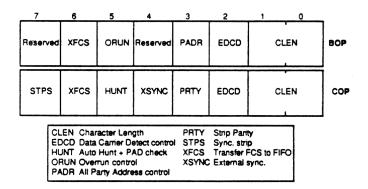

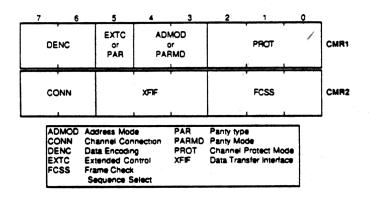

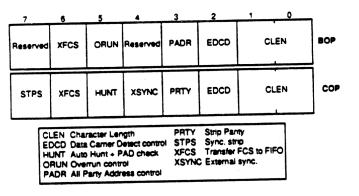

|         | 7.2.6    | Channel Mode Registers (CMR1 and CMR2)                          |      |

|         | 7.2.7    | Secondary Address Pegisters (CIR and CRA)                       | 7-10 |

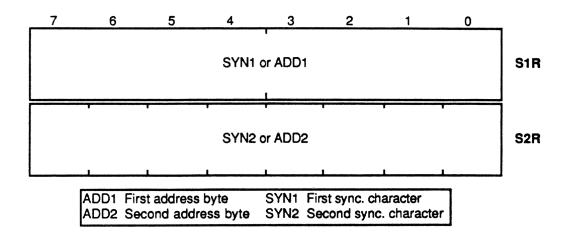

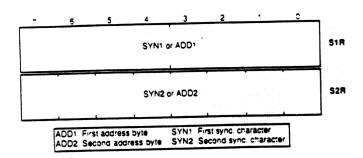

|         | 7.2.8    | Secondary Address Registers (S1R and S2R) Transmitter Registers | 7-19 |

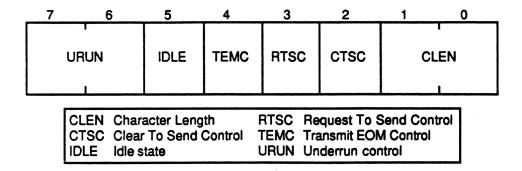

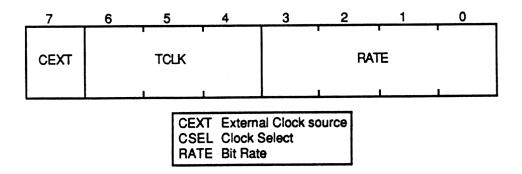

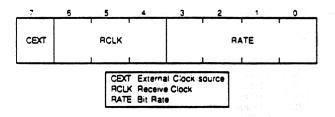

|         | 7.2.8.1  | Transmitter Parameter Register (TPR)                            | 7-20 |

|         | 7.2.8.2  |                                                                 | 7-20 |

|         |          |                                                                 | 7-24 |

|         | 7.2.8.3  |                                                                 |      |

|         | 7.2.9    | Receiver Registers                                              | 7-27 |

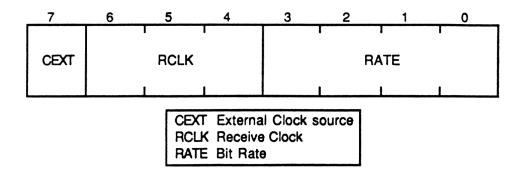

|         | 7.2.9.1  |                                                                 | 7-28 |

|         | 7.2.9.2  |                                                                 |      |

|         | 7.2.9.3  |                                                                 |      |

|         | 7.2.10   |                                                                 |      |

|         | 7.2.10.1 |                                                                 |      |

|         |          |                                                                 | 7-34 |

|         | 7.2.10.2 |                                                                 | 7-35 |

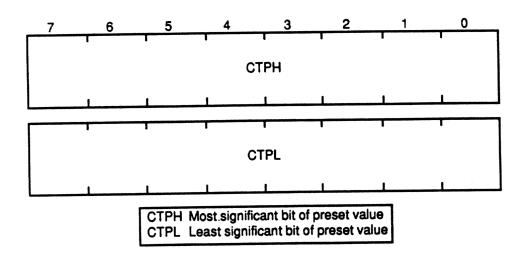

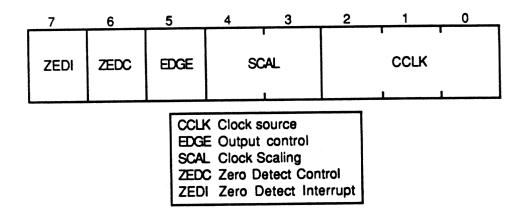

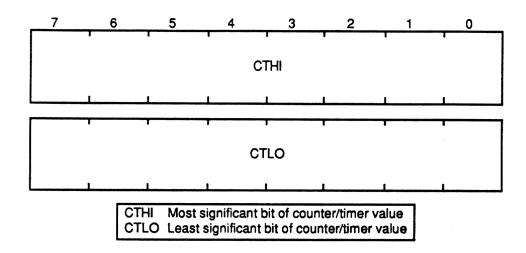

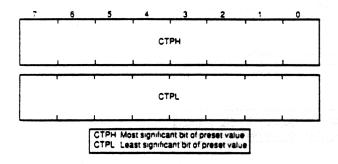

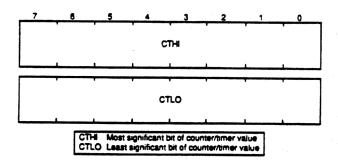

|         | 7.2.10.3 | Counter Timer (CTH and CTL)                                     | 7-37 |

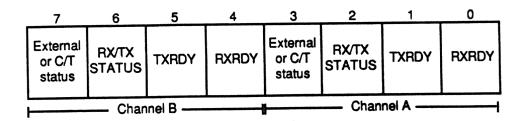

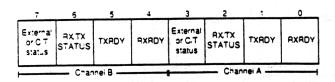

|         | 7.2.11   | Device and Channel Status Registers                             | 7-38 |

|         | 7.2.11.1 | General Status Register (GSR)                                   | 7-39 |

|         | 7.2.11.2 |                                                                 | 7-40 |

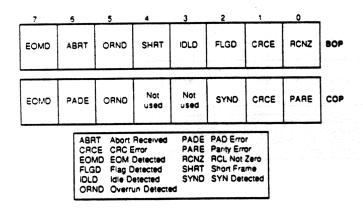

|         | 7.2.11.3 |                                                                 |      |

|         |          | (TRSR)                                                          | 7-45 |

|         | 7.2.11.4 |                                                                 |      |

|         |          | (ICTSR)                                                         | 7-49 |

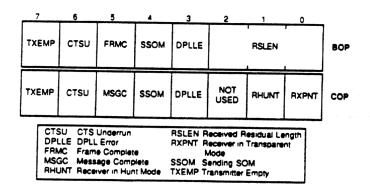

|         | 7.2.12   |                                                                 |      |

|         | 7.2.12.1 |                                                                 |      |

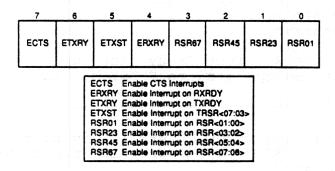

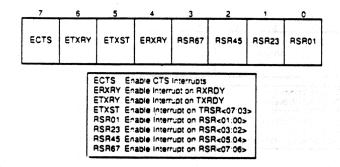

|         | 7.2.12.2 | Interrupt Enable Register (IER)                                 | 7-54 |

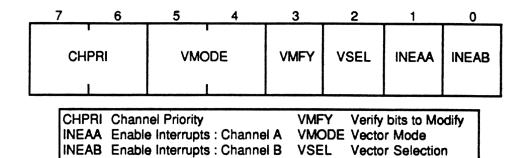

|         | 7.2.12.3 | Interrupt Vector Register (IVR)                                 | 7-56 |

|         | 7.2.12.4 | Interrupt Vector Register, Modified                             |      |

|         |          | (IVRM)                                                          | 7-56 |

|         | 7.2.13   | Miscellaneous Registers                                         | 7-58 |

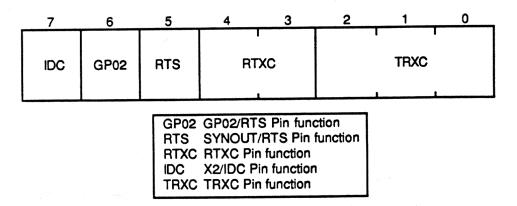

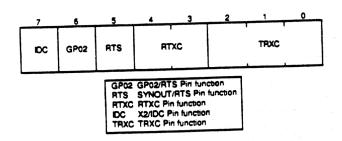

|         | 7.2.13.1 | l Pin Configuration Register (PCR)                              | 7-58 |

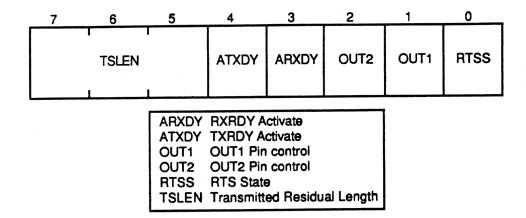

|         | 7.2.13.2 |                                                                 | 7-59 |

|         | 7.2.14   |                                                                 | 7-61 |

|         | 7.2.15   | Effects of Resetting the Device                                 | 7-61 |

|         | 7.3      |                                                                 | 7-62 |

|         | 7.4      |                                                                 | 7-63 |

|         | 7.4.1    |                                                                 | 7-63 |

|         | 7.4.1.1  | Transmission Synchronizers                                      | 7-64 |

|         | 7.4.1.2  |                                                                 | 7-64 |

|         | 7.4.1.3  |                                                                 | 7-64 |

|         | 7.4.1.4  | Loopback Controllers                                            | 7-65 |

|         | 7.4.2    | Architecture                                                    |      |

|         | 7.4.3    | Registers                                                       | 7-66 |

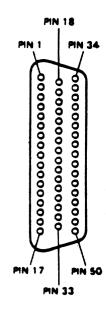

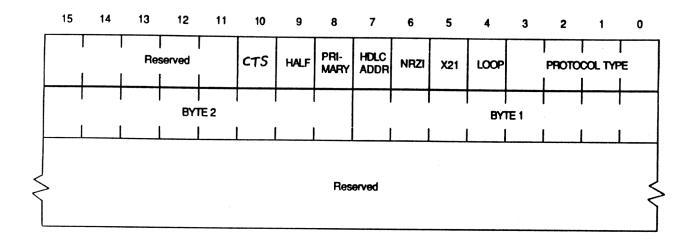

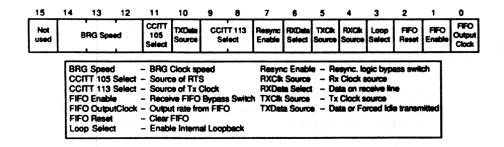

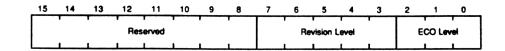

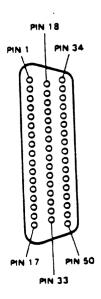

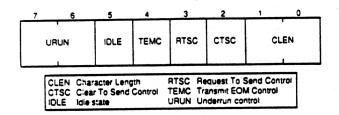

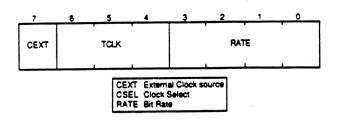

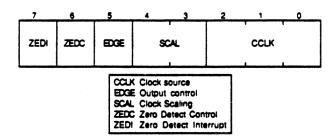

|         | 7.4.3.1<br>7.4.3.2<br>7.4.4<br>7.5<br>7.5.1<br>7.5.2<br>7.5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Channel Control Registers (DBCR) SSL Identification Register (DBIDR) . Accessing the Registers Line Drivers and Connectors | . 7-70<br>. 7-71<br>. 7-72<br>. 7-72 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| CHAPTER | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DMA devices                                                                                                                |                                      |

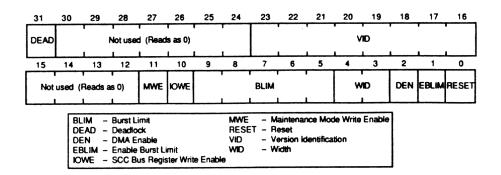

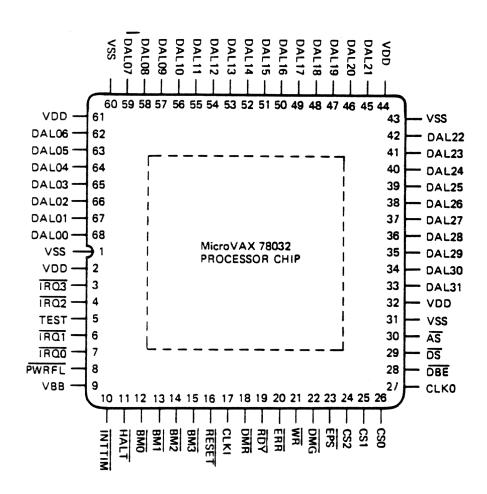

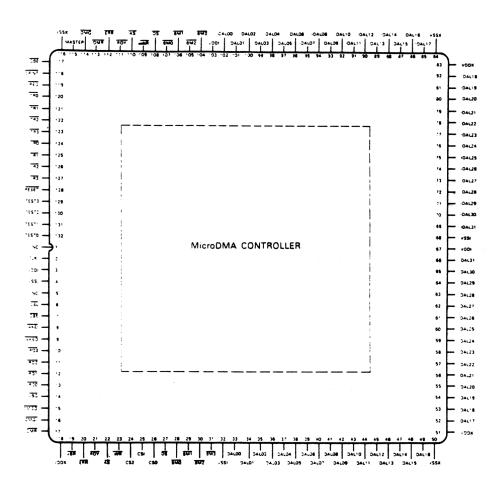

|         | 8.1<br>8.2<br>8.3<br>8.3.2<br>8.3.2.3<br>8.3.2.3<br>8.3.2.5<br>8.3.2.6<br>8.3.2.6<br>8.3.2.6<br>8.3.3.3.1<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3.3<br>8.3<br>8 | Introduction                                                                                                               |                                      |

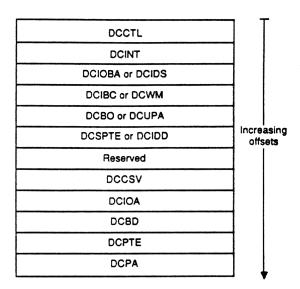

|         | 8.3.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5 Current Physical Address (DCPA)                                                                                          | . 8-17                               |

|         | 8.3.4<br>8.3.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            | . 8-17                               |

|         | 8.3.4.2<br>8.3.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 그는 사람들은 사람들이 하는 사람들이 하는 이 사람들이 되었다면 사람들이 살아 하는 바람들이 되었다. 그렇게 하는 그를 모르는 사람들이 되었다.                                           | . 8-19<br>. 8-21                     |

|         | 8.4<br>8.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DMA Channel Priorities and Device Chaining<br>How the MicroVAX Uses the MicroDMA                                           | . 8-23<br>. 8-24<br>. 8-25           |

|         | 8.6<br>8.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | How the TMS Processor Uses the DMA                                                                                         | 8-26                                 |

| CHAPTER | 9                  | Miscellaneous Functions                                                                      |                                 |

|---------|--------------------|----------------------------------------------------------------------------------------------|---------------------------------|

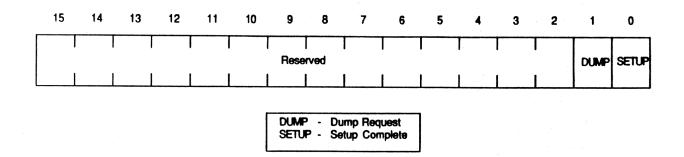

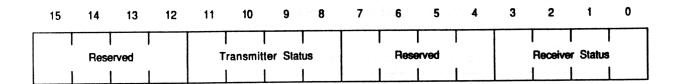

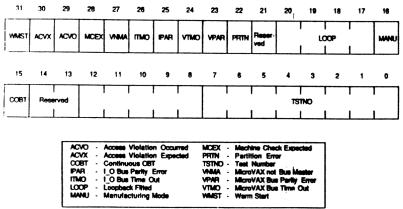

|         | 9.3.2.1<br>9.3.2.2 | Dump and Restart Sequence                                                                    | 9-3<br>9-3<br>9-4<br>9-7<br>9-8 |

|         | 9.4                | External Logic Interface                                                                     | 9-8                             |

| CHAPTER | 10                 | System control                                                                               |                                 |

|         | 10.1               | Introduction                                                                                 | 10-1                            |

|         | 10.2               | Introduction                                                                                 | 10-1                            |

|         | 10.3               | Event Reporting                                                                              | 10-2                            |

|         | 10.3.1             | Event Reporting                                                                              | 10-2                            |

|         | 10.3.2             | Event Processing                                                                             | 10-7                            |

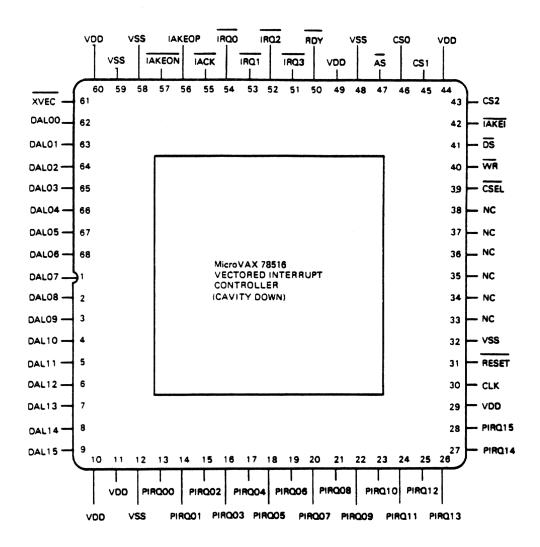

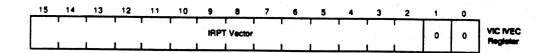

|         | 10.4               | The MicroVAX Vectored Interrupt Controller                                                   |                                 |

|         | 10 4 1             | (VIC)                                                                                        | 10-7                            |

|         | 10.4.1             | Interrupt Properties                                                                         | 10-8                            |

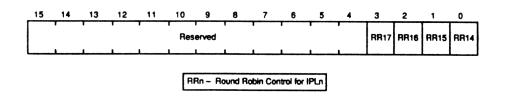

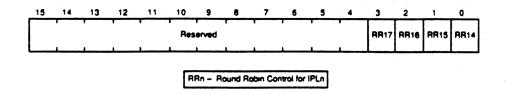

|         | 10.4.2             | Interrupt Priorities                                                                         | 10-9                            |

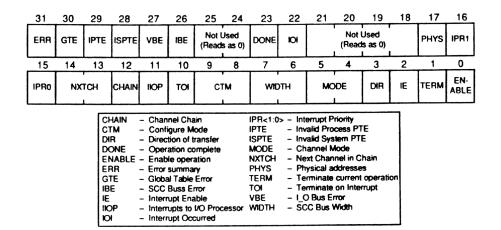

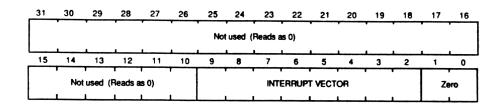

|         | 10.4.3             | Registers and Register Types                                                                 | 10-10                           |

|         | 10.4.4             | Signal Condition                                                                             | 10-10                           |

|         | 10.4.5             |                                                                                              | 10-11                           |

|         | 10.4.6             | Priority Scheme                                                                              | 10-12                           |

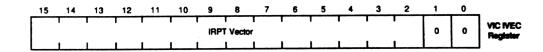

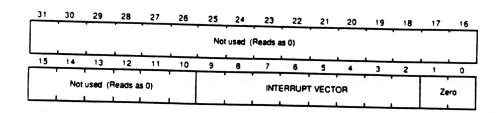

|         | 10.4.7             | Interrupt Vectors                                                                            | 10-13                           |

|         | 10.4.8             | Masking                                                                                      | 10-13                           |

|         | 10.4.9             | Pending Interrupts                                                                           | 10-14                           |

|         | 10.4.10            | Present of Docom                                                                             | 7 7 4                           |

|         | 10.4.11            | Register Addressing                                                                          | 10-14                           |

|         | 10.5               | Register Addressing Error Handling Nonexistent Memory MicroVAX Bus Accesses I O Bus Accesses | 10-15                           |

|         | 10.5.1             | Nonexistent Memory                                                                           | 10-16                           |

|         | 10.5.1.1           | MicroVAX Bus Accesses                                                                        | 10-16                           |

|         | 10.5.1.2           | I O Bus Accesses                                                                             | 10-16                           |

|         | 10.5.1.5           | D SCC BUS ACCESSES                                                                           | TO-T9                           |

|         |                    |                                                                                              | 10-17                           |

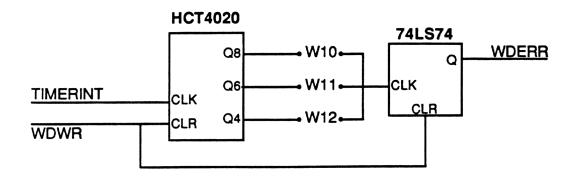

|         | 10.5.3             | Watchdog Expiry                                                                              | 10-17                           |

|         | 10.5.4             | Dump Switch                                                                                  | 10-17                           |

|         | 10.5.5             |                                                                                              | 10-17                           |

|         | 10.6               | Cross-Bus Accessing                                                                          | 10-18                           |

|         | 10.6.1             | MicroVAX Access to the SCC Bus                                                               | 10-18                           |

|         | 10.6.2             | TMS Processor Access to the I_O Bus                                                          | 10-19                           |

|         | 10.6.3             | LANCE Access to the I_O Bus                                                                  | 10-19                           |

| PART III | • A          | FIRMWARE                             |       |        |

|----------|--------------|--------------------------------------|-------|--------|

|          |              |                                      |       |        |

| CHAPTER  | 11           | Overview of the Firmware             |       |        |

|          | 11.1<br>11.2 | Types of Firmware                    | •     | . 11-1 |

|          | 11.3         | VAX Firmware                         | •     | 11-2   |

|          | 11.4         | VAX Firmware                         |       | . 11-2 |

|          |              |                                      |       |        |

|          | - 0          |                                      |       |        |

| CHAPTER  | 12           | On-Board Test                        |       |        |

|          | 12.1         | Overview                             |       | . 12-1 |

|          | 12.2         | Overview                             |       | . 12-1 |

|          | 12.2.1       | Low Level Phase                      | •     | 12-2   |

|          | 12.2.1.1     | Firmware ROM CRC                     |       | 12-3   |

|          | 12.2.1.2     | System PAM                           | •     | 12-3   |

|          | 12.2.1.3     |                                      | •     | 12-2   |

|          | 12.2.1.4     | MICIOVAX PIOCESSOI                   | •     | . 12-3 |

|          |              |                                      | •     | . 12-4 |

|          | 12.2.1.5     |                                      | •,    | . 12-4 |

|          | 12.2.1.6     |                                      |       |        |

|          | 12.2.1.      |                                      |       |        |

|          | 12.2.1.8     |                                      | •     | . 12-5 |

|          | 12.2.1.9     |                                      |       |        |

|          | 12.2.1.      |                                      | • 1   | . 12-6 |

|          | 12.2.1.3     |                                      |       |        |

|          | 12.2.1.      |                                      |       |        |

|          | 12.2.2       | Ethernet Interface Phase             | •     | . 12-6 |

|          | 12.2.2.      | LANCE Control and Status Registers   | • '•  | . 12-7 |

|          | 12.2.2.2     |                                      | • •   | . 12-7 |

|          | 12.2.2.3     | B Ethernet Loopback                  |       | . 12-8 |

|          | 12.2.3       | Synchronous I/O Phase                |       | . 12-8 |

|          | 12.2.3.3     | MicroDMA Controller                  |       | . 12-9 |

|          | 12.2.3.2     |                                      |       | . 12-9 |

|          | 12.2.3.3     | 3 DUSCC                              | • • • | . 12-9 |

|          | 12.2.3.4     | Synchronous Internal Data Loopback   |       | 12-10  |

|          | 12.2.3.      | Receive FIFO                         |       | 12-10  |

|          | 12.2.3.      | Modem Status Loopback                |       | 12-10  |

|          | 12.2.3.      | 7 Synchronous External Data Loopback |       | 12-11  |

|          | 12.2.3.8     | TMS Processor                        |       | 12-11  |

|          | 12.2.4       | Exerciser Phase                      |       | 12-11  |

|          | 12.2.5       |                                      |       | 12-12  |

|          | 12.2.5.      |                                      |       | 12-13  |

|          | 12.2.5.      | Incremental                          |       | 12-13  |

|          | 12.2.6       | Start Up Processing                  |       | 12-13  |

|          | 12.2.7       | Error Reporting                      |       | 12-14  |

|          | 12.2.7.      | 1 Previous Error Summary             |       | 12-14  |

|          | 12.2.7.      |                                      |       | 12-15  |

|          | 12.2.7.      |                                      |       | 12-15  |

|          | 12 2 8       |                                      |       | 12-17  |

|         | 12.3<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.4.1<br>12.4.1<br>12.4.2<br>12.4.3<br>12.4.4 | Manufacturing Tests  Using the Tests  Available Tests  Use of the Seven-Segment Display  Getting Error Information on Test Failur  Limitations to Test Coverage  Basic Hardware  Ethernet Interface  Synchronous I/O  Memory Management  Miscellaneous Functions | 12-20<br>12-22<br>12-23<br>12-24<br>12-24<br>12-24<br>12-25<br>12-26 |

|---------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| CHAPTER | 13                                                                                             | VAX Firmware                                                                                                                                                                                                                                                     |                                                                      |

|         | 13.1                                                                                           | Overview                                                                                                                                                                                                                                                         | . 13-1                                                               |

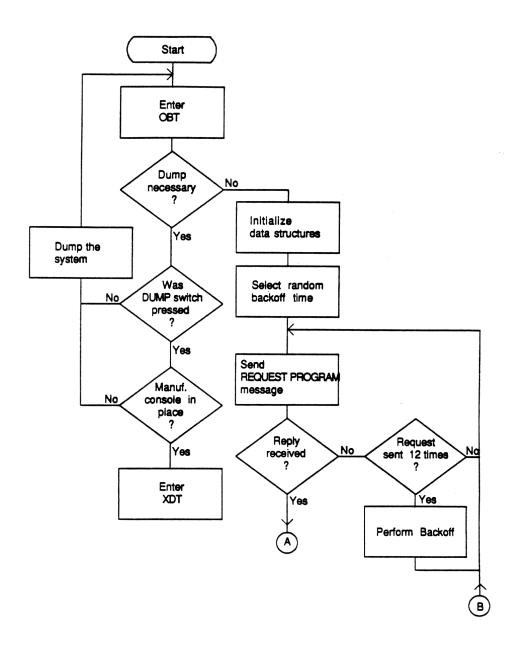

|         | 13.2                                                                                           | System Startup                                                                                                                                                                                                                                                   | . 13-1                                                               |

|         | 13.2.1                                                                                         | Setup and Test                                                                                                                                                                                                                                                   | . 13-2                                                               |

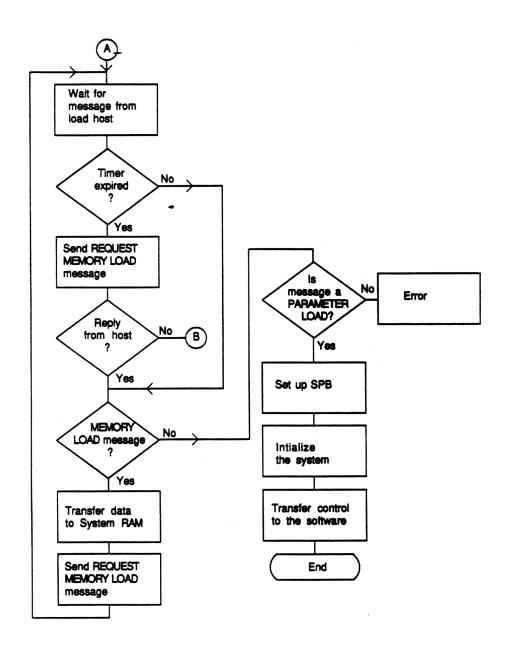

|         | 13.2.2                                                                                         | Request a Load Host                                                                                                                                                                                                                                              | . 13-2                                                               |

|         | 13.2.3                                                                                         | Load the Software                                                                                                                                                                                                                                                | . 13-3                                                               |

|         | 13.2.4                                                                                         | Transfer Control to the Software                                                                                                                                                                                                                                 | . 13-4                                                               |

|         | 13.2.4.1                                                                                       | The System Parameter Block                                                                                                                                                                                                                                       | . 13-4                                                               |

|         | 13.2.4.2                                                                                       | Initializing the System                                                                                                                                                                                                                                          | . 13-7                                                               |

|         | 13.2.4.3                                                                                       | Passing Control to the Software                                                                                                                                                                                                                                  | . 13-8                                                               |

|         | 13.2.5                                                                                         | Use of the Seven-Segment Display                                                                                                                                                                                                                                 |                                                                      |

|         | 13.2.6                                                                                         | Format of the Image File                                                                                                                                                                                                                                         | . 13-9                                                               |

|         | 13.2.7                                                                                         | Use of Software Identification                                                                                                                                                                                                                                   | . 13-9                                                               |

|         | 13.2.7.1                                                                                       |                                                                                                                                                                                                                                                                  |                                                                      |

|         | 13.2.7.2                                                                                       | Limitations of Software ID                                                                                                                                                                                                                                       | 13-10                                                                |

|         | 13.2.8                                                                                         | Effect of the Manufacturing Console                                                                                                                                                                                                                              | 13-11                                                                |

|         | 13.2.9                                                                                         | Summary                                                                                                                                                                                                                                                          |                                                                      |

|         | 13.3                                                                                           | System Dump                                                                                                                                                                                                                                                      |                                                                      |

|         | 13.3.1                                                                                         | System Dump                                                                                                                                                                                                                                                      | 13-14                                                                |

|         | 13.3.2                                                                                         | Dumping the System                                                                                                                                                                                                                                               | 13-15                                                                |

|         | 13.3.3                                                                                         | Rebooting the System                                                                                                                                                                                                                                             | 13-16                                                                |

|         | 13.3.4                                                                                         | Use of the Seven-Segment Display                                                                                                                                                                                                                                 | 13-16                                                                |

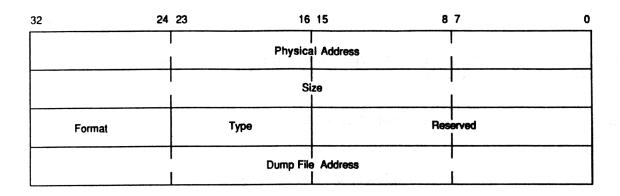

|         | 13.3.5                                                                                         | Format of the Dump File                                                                                                                                                                                                                                          | 13-17                                                                |

|         | 13.3.6                                                                                         | Effect of the Manufacturing Console or                                                                                                                                                                                                                           |                                                                      |

|         |                                                                                                | the Remote Console                                                                                                                                                                                                                                               | 13-17                                                                |

|         | 13.3.7                                                                                         |                                                                                                                                                                                                                                                                  |                                                                      |

|         | 13.4                                                                                           | Summary                                                                                                                                                                                                                                                          | 13-19                                                                |

|         | 13.4.1                                                                                         | Boot the System (ROM\$CALL BOOT)                                                                                                                                                                                                                                 | 13-19                                                                |

|         | 13.4.2                                                                                         | Dump the System (ROM\$CALL DUMP)                                                                                                                                                                                                                                 |                                                                      |

|         | 13.4.3                                                                                         | Maintain Console Carrier Session                                                                                                                                                                                                                                 |                                                                      |

|         |                                                                                                |                                                                                                                                                                                                                                                                  | 13-20                                                                |

|         | 13.4.4                                                                                         | (ROM\$MOP_FN)                                                                                                                                                                                                                                                    | 13-20                                                                |

|         | 13.4.5                                                                                         | Get Parameters from NVRAM                                                                                                                                                                                                                                        |                                                                      |

|         |                                                                                                | (ROM\$GET_PARAMS)                                                                                                                                                                                                                                                | 13-22                                                                |

|         | 13.4.6                                                                                         | Execute a Console Command                                                                                                                                                                                                                                        |                                                                      |

|         |                                                                                                | (ROM\$DO COMMAND)                                                                                                                                                                                                                                                | 13-22                                                                |

|         | 13.4.7                                                                                         | Load a Specified Image (ROM\$LOAD SYS) .                                                                                                                                                                                                                         | 13-22                                                                |

|         | 13.4.8 Set the Software State Text                                   |            |

|---------|----------------------------------------------------------------------|------------|

|         | (ROM\$SET_TEXT)                                                      | 23         |

|         | (ROM\$SET_TEXT)                                                      |            |

|         | (ROMSGET_VERSION)                                                    | 23         |

|         | 13.4.10 Calling the Routines                                         | 23         |

|         | 13.5 Ethernet Driver                                                 | 24         |

|         | 13.5.1 MOP Support                                                   | 25         |

|         | 13.5.2 System Identification Information 13-                         | 25         |

|         | 13.5.3 Effect of the NCP TRIGGER Command 13-                         | 26         |

|         | 12 6 Concolo 12-                                                     | 26         |

|         | 13.7 Console XDT 13-                                                 | 27         |

|         | 13.7 Console XDT                                                     | 27         |

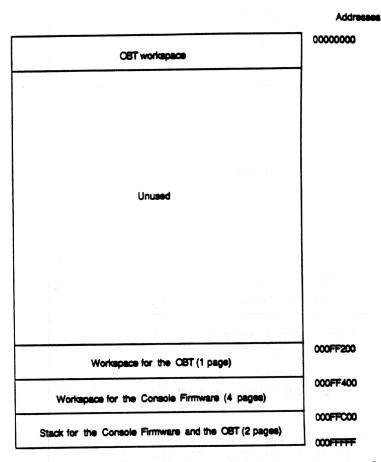

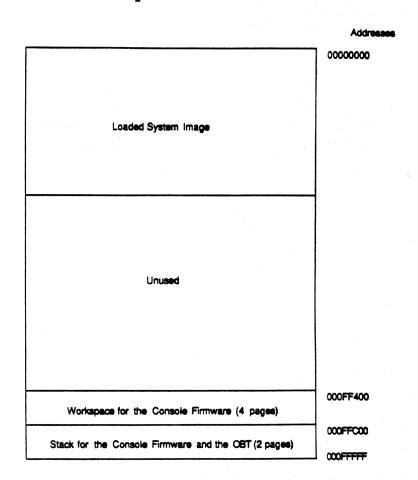

|         | 13.0 Memory Haage                                                    | 20         |

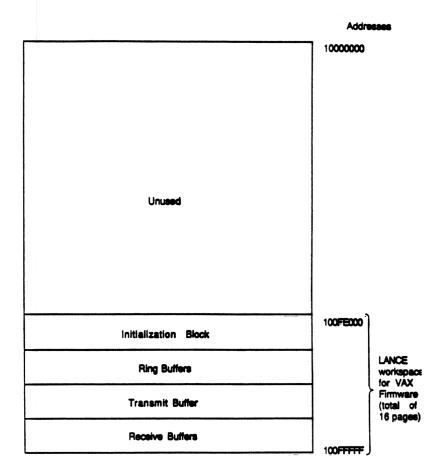

|         | 13.9 Memory Usage                                                    | 20         |

|         | 13.9.1 System RAM                                                    | 2 J<br>2 N |

|         | 13.9.2 Builer RAM                                                    | 30         |

|         |                                                                      |            |

|         |                                                                      |            |

| CHAPTER | 14 TMS Processor Firmware                                            |            |

|         |                                                                      |            |

|         | 14.1 Introduction                                                    | -1         |

|         | 14.2 Control Interface with the MicroVAX 14                          | -2         |

|         | 14.2.1 Commands to the TMS Processor 14                              | -2         |

|         | 14.2.1.1 Initialize Receiver                                         | -2         |

|         | 14.2.1.2 Start Receiver                                              | -2         |

|         | 14.2.1.3 Stop Receiver and Abort Current Packet . 14                 | -3         |

|         | 14.2.1.4 Turn Off the Receiver                                       | -3         |

|         | 14.2.1.5 Initialize Transmitter                                      | -3         |

|         | 14.2.1.6 Start Transmitter                                           | _3         |

|         | 14.2.1.7 Stop Transmitter and Abort Current                          | J          |

|         | Packet                                                               | _3         |

|         | 14.2.1.8 Stop Transmitter After Current Packet . 14                  | _ 3        |

|         |                                                                      | -3         |

|         | 14.2.1.9 Abort the Current Packet and Flush any                      |            |

|         | Pending Packets                                                      | -4         |

|         | 14.2.1.10 Switch Off the Transmitter 14                              | -4         |

|         | 14.2.1.11 Complete the Current Packet and Flush                      | _          |

|         | Any Pending Packets 14                                               | -4         |

|         | 14.2.1.12 Command Queuing 14                                         | -4         |

|         | 14.2.1.13 Port States                                                | -4         |

|         | 14.2.2 Boot and Dump Control 14                                      |            |

|         | 14.2.3 Loading 14                                                    | -7         |

|         | 14.2.4 Dumping 14                                                    | -7         |

|         | 14.2.5 Modem and Interrupt Control 14                                | -8         |

|         | 14.2.6 Status Values                                                 | -8         |

|         | 14.2.6.1 Global Status Register 14                                   | -9         |

|         | 14.2.6.2 Port Status Registers 14                                    | _ q        |

|         | 14.2.6.3 Alive Counters                                              | _ a        |

|         | 14.2.7 MicroVAX/TMS Processor Protocol 14-                           | ر<br>1 0   |

|         | 14.2.7.1 Location Polling 14-                                        | 10         |

|         | 14.2.7.1 Location Polling 14-<br>14.2.7.2 Interrupt Notification 14- | 10         |

|         | 14.2.7.2 Interrupt Notification                                      | 1 7        |

|         | 14.3 Buffer Passing                                                  | 17         |

|         | 14.4 Channel Control 14-                                             | 1/         |

|         | 14.4.1<br>14.4.2<br>14.4.3<br>14.4.4<br>14.5<br>14.6<br>14.6.1<br>14.6.2<br>14.7 | Occurrence of the TMSINT Interrupt 14-13 Loading the Firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER | 15                                                                               | Buffer Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

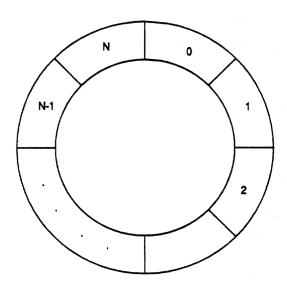

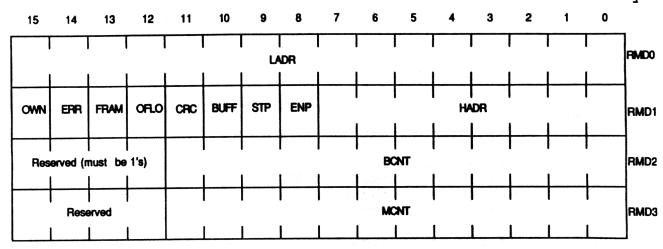

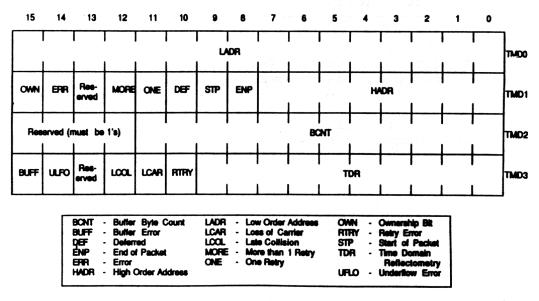

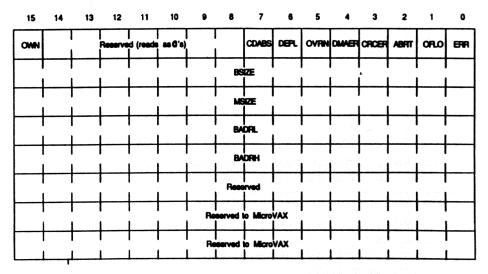

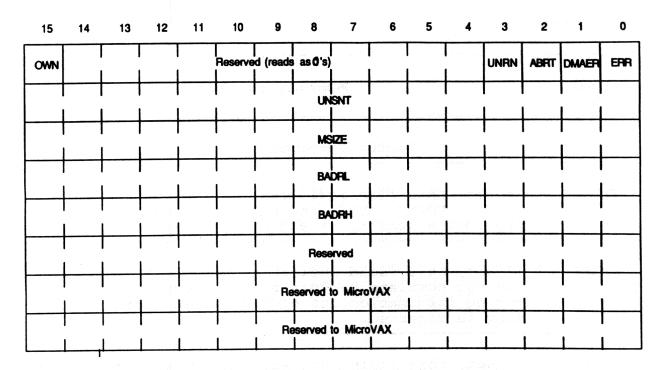

|         | 15.3<br>15.3.1<br>15.3.2<br>15.3.3<br>15.4<br>15.4.1<br>15.4.2                   | Descriptor Ownership       15-2         Descriptor Contents       15-3         Ring Sizes       15-4         Using the Rings       15-5         1 Transmit       15-5         2 Receive       15-5         Ethernet Ring Descriptors       15-6         Receive Descriptor       15-6         Transmit Descriptor Ring       15-9         Buffer Chaining       15-13         Synchronous Ring Descriptors       15-13         Receive       15-14         Transmit       15-18         Buffer and Descriptor Use       15-21 |

| CHAPTER | 16                                                                               | Non-Volatile Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | 16.1<br>16.2<br>16.3<br>16.4<br>16.4.1                                           | Overview of Structure and Content 16-1 Details of Field Contents 16-4 Clearing Fields in the NVRAM                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | 16.4.2<br>16.4.3<br>16.4.4<br>16.5                                               | Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

PART IV TROUBLESHOOTING

| CHAPTER | 17                | Circuit Board Troubleshooting                                  |        |

|---------|-------------------|----------------------------------------------------------------|--------|

|         | 17.1              | Introduction                                                   | . 17-1 |

|         | 17.1.1            | Equipment Level Required                                       | . 17-4 |

|         | 17.2              | Equipment Level Required                                       | . 17-5 |

|         | 17.2.1            | At Power Up the LED is Blank                                   | 17-5   |

|         | 17.2.2            | Processor Subsection                                           | 17-5   |

|         | 17.2.2.           |                                                                | 17-6   |

|         | 17.2.2.           | 2 Periodic EPS Activity on Power Up                            | 17-6   |

|         |                   | Z Periodic Ers Activity on rower op                            | 17-0   |

|         | 17.2.3            |                                                                |        |

|         | 17.2.4            |                                                                | . 17-0 |

|         | 17.2.4.           |                                                                | . 1/-9 |

|         | 17.2.4.           |                                                                | 17-10  |

|         | 17.2.4.           | 3 UVDRAM Parity Errors                                         | 17-12  |

|         | 17.2.4.           | 3.1 Machine Checks Due to UVDRAM Parity                        |        |

|         |                   | 3.1 Machine Checks Due to UVDRAM Parity Errors                 | 17-13  |

|         | 17.2.4.           | 3.2 UVDRAM Parity Error Reporting                              |        |

|         |                   | Mechanism Fault                                                | 17-15  |

|         | 17.2.4.           | 4 Incorrect UVDRAM Refresh Operation                           | 17-16  |

|         |                   | I_O Bus Faults                                                 | 17-16  |

|         | 17.3.1            | I O Bus Timeouts                                               |        |

|         | 17 3 2            | IODRAM Related Faults                                          | 17-19  |

|         | 17.3.2<br>17.3.2. | 1 Stuck-At 0/1 and Cross-Coupling                              | 17-19  |

|         | 17.3.2.           | 2 IODRAM Parity Reporting                                      | 17-20  |

|         | 17.3.2.           | 2.1 IODRAM Parity Errors                                       | 17-21  |

|         | 17.3.2.           | 2.2 IODRAM Parity Error Reporting                              | 1/-21  |

|         | 17.3.2.           |                                                                | 17-23  |

|         | 17 2 2            | Mechanism Fault                                                |        |

|         | 17.3.2.           |                                                                |        |

|         | 17.3.3            |                                                                |        |

|         | 17.3.3.           |                                                                |        |

|         | 17.3.3.           |                                                                |        |

|         |                   | SCC Bus Faults                                                 |        |

|         | 17.4.1            |                                                                |        |

|         | 17.4.1.           | SCC Bus Accesses Through the ADMA                              | 17-28  |

|         | 17.4.1.           |                                                                |        |