# Alpha 21064A Microprocessors

# **Data Sheet**

Order Number: EC-QFGKC-TE

This document contains information about the following Alpha microprocessors: 21064A–200, 21064A–233, 21064A–275, 21064A–275–PC, and 21064A–300.

**Revision/Update Information:**

This document supersedes the *Alpha 21064A-233, -275 Microprocessor Data Sheet,* EC-QFGKB-TE.

Digital Equipment Corporation Maynard, Massachusetts

#### January 1996

While Digital believes the information included in this publication is correct as of the date of publication, it is subject to change without notice.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

© Digital Equipment Corporation 1995, 1996. All rights reserved. Printed in U.S.A.

AlphaGeneration, Digital, Digital Semiconductor, OpenVMS, VAX, VAX DOCUMENT, the AlphaGeneration design mark, and the DIGITAL logo are trademarks of Digital Equipment Corporation.

Digital Semiconductor is a Digital Equipment Corporation business.

GRAFOIL is a registered trademark of Union Carbide Corporation. Windows NT is a trademark of Microsoft Corporation.

All other trademarks and registered trademarks are the property of their respective owners.

This document was prepared using VAX DOCUMENT Version 2.1.

# Contents

| 1       | Overview                                                 | 1  |

|---------|----------------------------------------------------------|----|

| 2       | Signal Names and Functions                               | 6  |

| 3       | Instruction Set                                          | 17 |

| 3.1     | Instruction Summary                                      | 17 |

| 3.2     | IEEE Floating-Point Instructions                         | 23 |

| 3.3     | 21064A IEEE Floating-Point Conformance                   | 25 |

| 3.4     | VAX Floating-Point Instructions                          | 28 |

| 3.5     | Required PALcode Function Codes                          | 29 |

| 3.6     | Opcodes Reserved for PALcode                             | 29 |

| 3.7     | Opcodes Reserved for Digital                             | 29 |

| 3.8     | Instructions Specific to the 21064A                      | 30 |

| 4       | Internal Processor Registers                             | 31 |

| 4.1     | Ibox Internal Processor Registers                        | 31 |

| 4.1.1   | Translation Buffer Tag Register (TB_TAG)                 | 31 |

| 4.1.2   | Instruction Translation Buffer Page Table Entry Register |    |

|         | (ITB_PTE)                                                | 32 |

| 4.1.3   | Instruction Cache Control and Status Register            |    |

|         | (ICCSR)                                                  | 33 |

| 4.1.3.1 | Performance Counters                                     | 36 |

| 4.1.4   | Instruction Translation Buffer Page Table Entry          |    |

|         | Temporary Register (ITB_PTE_TEMP)                        | 38 |

| 4.1.5   | Exceptions Address Register (EXC_ADDR)                   | 39 |

| 4.1.6   | Clear Serial Line Interrupt Register (SL_CLR)            | 40 |

| 4.1.7   | Serial Line Receive Register (SL_RCV)                    | 41 |

| 4.1.8   | Instruction Translation Buffer ZAP Register              |    |

|         | (ITBZAP)                                                 | 41 |

| 4.1.9   | Instruction Translation Buffer ASM Register              |    |

|         | (ITBASM)                                                 | 42 |

| 4.1.10  | Instruction Translation Buffer IS Register (ITBIS)       | 42 |

| 4.1.11  | Processor Status Register (PS)                           | 42 |

| 4.1.12  | Exception Summary Register (EXC_SUM)                     | 42 |

| 4.1.13  | PAL_BASE Address Register (PAL_BASE)                     | 44 |

| 4.1.14  | Hardware Interrupt Request Register (HIRR)               | 44 |

|         |                                                          |    |

| 4.1.15 | Software Interrupt Request Register (SIRR)         | 46 |

|--------|----------------------------------------------------|----|

| 4.1.16 | Asynchronous Trap Request Register (ASTRR)         | 47 |

| 4.1.17 | Hardware Interrupt Enable Register (HIER)          | 48 |

| 4.1.18 | Software Interrupt Enable Register (SIER)          | 49 |

| 4.1.19 | AST Interrupt Enable Register (ASTER)              | 50 |

| 4.1.20 | Serial Line Transmit Register (SL_XMIT)            | 50 |

| 4.2    | Abox Internal Processor Registers                  | 51 |

| 4.2.1  | Translation Buffer Control Register (TB_CTL)       | 51 |

| 4.2.2  | Data Translation Buffer Page Table Entry Register  |    |

|        | (DTB_PTE)                                          | 51 |

| 4.2.3  | Data Translation Buffer Page Table Entry Temporary |    |

|        | Register (DTB_PTE_TEMP)                            | 52 |

| 4.2.4  | Memory Management Control and Status Register      |    |

|        | (MM_CSR)                                           | 53 |

| 4.2.5  | Virtual Address Register (VA)                      | 54 |

| 4.2.6  | Data Translation Buffer ZAP Register (DTBZAP)      | 54 |

| 4.2.7  | Data Translation Buffer ASM Register (DTBASM)      | 54 |

| 4.2.8  | Data Translation Buffer Invalidate Single Register |    |

|        | (DTBIS)                                            | 54 |

| 4.2.9  | Flush Instruction Cache Register (FLUSH_IC)        | 54 |

| 4.2.10 | Flush Instruction Cache ASM Register               |    |

|        | (FLUSH_IC_ASM)                                     | 54 |

| 4.2.11 | Abox Control Register (ABOX_CTL)                   | 55 |

| 4.2.12 | Alternate Processor Mode Register (ALT_MODE)       | 58 |

| 4.2.13 | Cycle Counter Register (CC)                        | 58 |

| 4.2.14 | Cycle Counter Control Register (CC_CTL)            | 59 |

| 4.2.15 | Bus Interface Unit Control Register (BIU_CTL)      | 60 |

| 4.2.16 | Cache Status Register (C_STAT)                     | 65 |

| 4.2.17 | Bus Interface Unit Status Register (BIU_STAT)      | 66 |

| 4.2.18 | Bus Interface Unit Address Register (BIU_ADDR)     | 69 |

| 4.2.19 | Fill Address Register (FILL_ADDR)                  | 70 |

| 4.2.20 | Fill Syndrome Register (FILL_SYNDROME)             | 71 |

| 4.2.21 | Backup Cache Tag Register (BC_TAG)                 | 73 |

| 4.3    | PAL_TEMP Registers                                 | 74 |

| 4.4    | Lock Registers                                     | 74 |

| 4.5    | Internal Processor Registers Reset State           | 75 |

| 5      | Electrical Characteristics                         | 78 |

| 5.1    | DC Characteristics                                 | 79 |

| 5.2    | AC Characteristics                                 | 81 |

| 6      | Thermal Considerations                             | 94 |

| 6.1    | Critical Parameters of Thermal Design              | 96 |

| 7      | Mechanical Specifications                          | 99 |

| 7.1    | Package Information                                | 99 |

|        | 0                                                  |    |

| 7.2 | 21064A Pins      | 101 |

|-----|------------------|-----|

| 7.3 | Signal Pin Lists | 108 |

# Figures

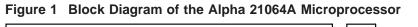

| 1  | Block Diagram of the Alpha 21064A Microprocessor         | 5  |

|----|----------------------------------------------------------|----|

| 2  | Translation Buffer Tag Register                          | 32 |

| 3  | Instruction Translation Buffer Page Table Entry Register | 33 |

| 4  | ICCSR Register                                           | 34 |

| 5  | ITB_PTE_TEMP Register                                    | 39 |

| 6  | Exception Address Register                               | 40 |

| 7  | Clear Serial Line Interrupt Register                     | 40 |

| 8  | Serial Line Receive Register                             | 41 |

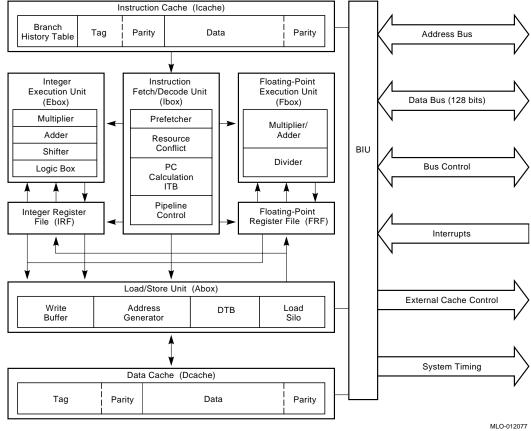

| 9  | Processor Status Register                                | 42 |

| 10 | Exception Summary Register                               | 43 |

| 11 | PAL_BASE Address Register                                | 44 |

| 12 | Hardware Interrupt Request Register                      | 45 |

| 13 | Software Interrupt Request Register                      | 46 |

| 14 | Asynchronous Trap Request Register                       | 47 |

| 15 | Hardware Interrupt Enable Register                       | 48 |

| 16 | Software Interrupt Enable Register                       | 49 |

| 17 | AST Interrupt Enable Register                            | 50 |

| 18 | Serial Line Transmit Register                            | 51 |

| 19 | Translation Buffer Control Register                      | 51 |

| 20 | Data Translation Buffer Page Table Entry Register        | 52 |

| 21 | Data Translation Buffer Page Table Entry Temporary       |    |

|    | Register                                                 | 52 |

| 22 | Memory Management Control and Status Register            | 53 |

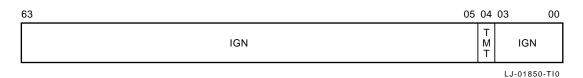

| 23 | Abox Control Register                                    | 55 |

| 24 | Alternate Processor Mode Register                        | 58 |

| 25 | Cycle Counter Register                                   | 59 |

| 26 | Cycle Counter Control Register                           | 59 |

| 27 | 21064A Bus Interface Unit Control Register               | 60 |

| 28 | Cache Status Register                                    | 65 |

| 29 | Bus Interface Unit Status Register                       | 67 |

| 30 | Bus Interface Unit Address Register                      | 69 |

| 31 | Fill Address Register                                    | 70 |

| 32     | FILL_SYNDROME Register                         | 71  |

|--------|------------------------------------------------|-----|

| 33     | Backup Cache Tag Register                      | 73  |

| 34     | Clock Termination                              | 82  |

| 35     | Input Clock Timing Diagram                     | 83  |

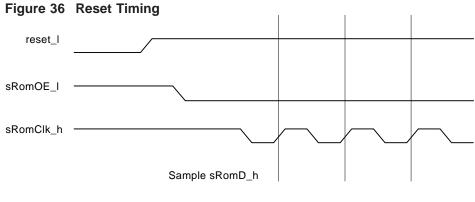

| 36     | Reset Timing                                   | 84  |

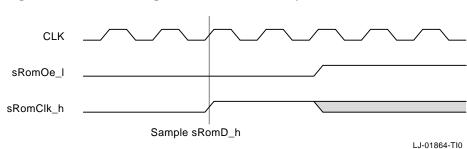

| 37     | Reset Timing—End of Preload Sequence           | 85  |

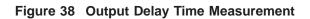

| 38     | Output Delay Time Measurement                  | 88  |

| 39     | Setup and Hold Time Measurement                | 89  |

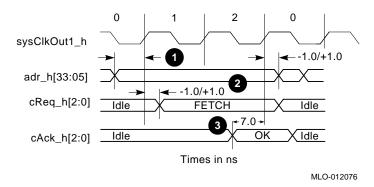

| 40     | READ_BLOCK Timing Diagram                      | 90  |

| 41     | WRITE_BLOCK Timing Diagram                     | 91  |

| 42     | BARRIER Timing Diagram                         | 92  |

| 43     | FETCH/FETCH_M Timing Diagram                   | 93  |

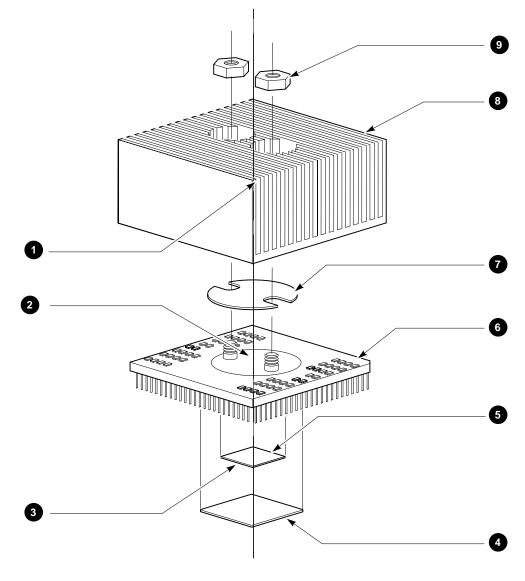

| 44     | Package Components and Temperature Measurement |     |

|        | Locations                                      | 95  |

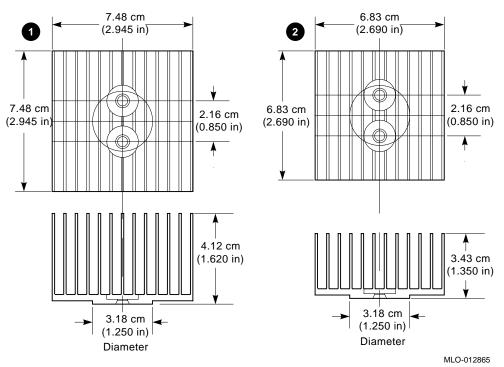

| 45     | Heat Sink Dimensions                           | 99  |

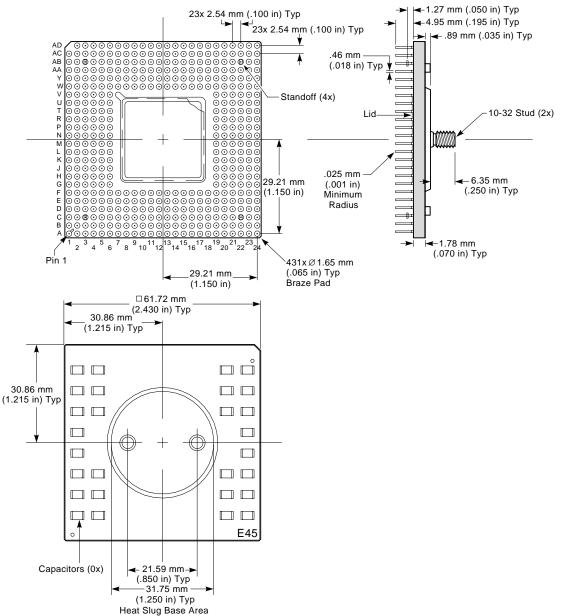

| 46     | Package Dimensions                             | 100 |

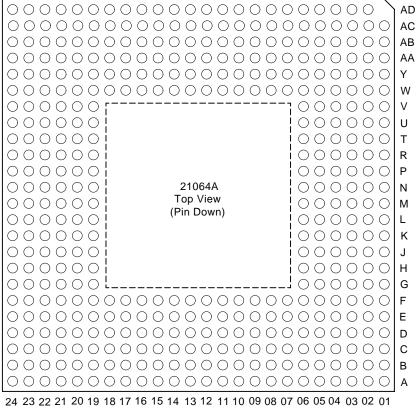

| 47     | PGA Cavity Down View                           | 101 |

|        |                                                |     |

| Tables |                                                |     |

| 1  | Data, Address, and Parity/ECC Bus Signals                 | 6  |

|----|-----------------------------------------------------------|----|

| 2  | Primary Cache Invalidate Signals                          | 6  |

| 3  | External Cache Control Signals                            | 7  |

| 4  | Fast Lock Mode Signals                                    | 9  |

| 5  | External Cycle Control Signals                            | 10 |

| 6  | Interrupt Signals                                         | 12 |

| 7  | Instruction Cache Initialization and Serial ROM Interface |    |

|    | Signals                                                   | 14 |

| 8  | Initialization Signals                                    | 15 |

| 9  | Clock Signals                                             | 15 |

| 10 | Performance Monitoring Signals                            | 16 |

| 11 | Other Signals                                             | 16 |

| 12 | Instruction Format and Opcode Notation                    | 17 |

| 13 | Architecture Instructions                                 | 18 |

| 14 | IEEE Floating-Point Instruction Function Codes            | 23 |

| 15 | VAX Floating-Point Instruction Function Codes             | 28 |

| 16 | Required PALcode Function Codes                           | 29 |

| 17 | Opcodes Specific to the 21064A                                 | 29  |

|----|----------------------------------------------------------------|-----|

| 18 | Opcodes Reserved for Digital                                   | 29  |

| 19 | Instructions Specific to the 21064A                            | 30  |

| 20 | ICCSR Fields and Description                                   | 34  |

| 21 | BHE, BPE Branch Prediction Selection (Conditional              |     |

|    | Branches Only)                                                 | 36  |

| 22 | Performance Counter 0 Input Selection (in ICCSR)               | 37  |

| 23 | Performance Counter 1 Input Selection (in ICCSR)               | 38  |

| 24 | Clear Serial Line Interrupt Register Fields                    | 41  |

| 25 | Exception Summary Register Fields                              | 43  |

| 26 | Hardware Interrupt Request Register Fields                     | 45  |

| 27 | Hardware Interrupt Enable Register Fields                      | 48  |

| 28 | Memory Management Control and Status Register                  | 53  |

| 29 | Abox Control Register Fields                                   | 55  |

| 30 | Alternate Processor Mode Register                              | 58  |

| 31 | Bus Interface Unit Control Register Fields                     | 60  |

| 32 | BC_SIZE                                                        | 64  |

| 33 | BC_PA_DIS                                                      | 64  |

| 34 | Cache Status Register Fields                                   | 65  |

| 35 | Bus Interface Unit Status Register Fields                      | 67  |

| 36 | Syndromes for Single-Bit Errors                                | 72  |

| 37 | Backup Cache Tag Register Fields                               | 74  |

| 38 | Internal Process Register Reset State                          | 75  |

| 39 | 21064A Maximum Ratings (PRELIMINARY                            |     |

|    | ESTIMATES)                                                     | 78  |

| 40 | DC Input/Output Characteristics                                | 80  |

| 41 | testClkIn Pin States                                           | 82  |

| 42 | Input Clock Timing                                             | 83  |

| 43 | External Cycles                                                | 85  |

| 44 | 21064A-200 Thermal Characteristics in a Forced-Air             |     |

|    | Environment                                                    | 96  |

| 45 | 21064A-233 Thermal Characteristics in a Forced-Air             |     |

|    | Environment                                                    | 97  |

| 46 | 21064A-275 and <b>21064A-275-PC</b> Thermal Characteristics in |     |

| 47 | a Forced-Air Environment                                       | 97  |

| 47 | 21064A-300 Thermal Characteristics in a Forced-Air             | 00  |

| 10 | Environment                                                    | 98  |

| 48 | Pin List                                                       | 102 |

| 49 | Data Signals Pin List                                      | 109 |

|----|------------------------------------------------------------|-----|

| 50 | Address Signals Pin List                                   | 111 |

| 51 | Parity/ECC Bus Signals Pin List                            | 112 |

| 52 | Primary Cache Invalidate Signals Pin List                  | 112 |

| 53 | External Cache Control Signals Pin List                    | 113 |

| 54 | Interrupt Signals Pin List                                 | 114 |

| 55 | Instruction Cache Initialization Signals Pin List          | 114 |

| 56 | Serial ROM Interface Signals Pin List                      | 114 |

| 57 | Initialization Signals Pin List                            | 115 |

| 58 | Load/Lock and Store/Conditional Fast Lock Mode Signals Pin |     |

|    | List                                                       | 115 |

| 59 | Clock Signals Pin List                                     | 115 |

| 60 | Performance Monitoring Signals Pin List                    | 115 |

| 61 | Other Signals Pin List                                     | 115 |

| 62 | Power Pin List                                             | 116 |

| 63 | Ground Pin List                                            | 117 |

| 64 | Spare Pin List                                             | 118 |

|    |                                                            |     |

### **1** Overview

This document describes the Alpha 21064A microprocessors (21064A). The five versions of the 21064A differ in clock frequency as indicated by their labels (200, 233, 275, 275-PC, and 300).

The 21064A-200, 21064A-233, 21064A-275, and the 21064A-300 are functionally identical. Their memory management operation is very flexible to allow them to enable multiple memory management functions for different operating system environments.

The 21064A-275-PC is functionally identical to the other four except that it differs in its memory management functions. The 21064A-275-PC will only support the memory management functions necessary for the Windows NT operating system and other operating systems using the Windows NT memory management model.

The label 21064A will be used to describe the functions and operations that are identical for the five devices. The label **21064A-275-PC** will be used to identify information that is unique to that one device.

The 21064A has the features listed here:

- 64-bit RISC microprocessor implements the Alpha architecture

- Super-scalar, 200, 233, 275, and 300 MHz

- System clock frequency is the processor clock frequency divided by any value from 2 to 17

- Dual instruction issue that yields a peak instruction execution rate of 400, 466, 550, or 600 MIPS

- Super pipelined

- Two on-chip caches (with data and tag parity protection)

- 16-Kbyte instruction cache (Icache)

- 16-Kbyte data cache (Dcache)

- 32 Integer registers and 32 floating-point registers (64-bit)

- 4K x 2-bit branch prediction history table

- External data path selectable for 128 bits or 64 bits

- Byte parity mode available for the external data bus

- Fast lock mode available for use with LDx/L and STx/C instructions

- Backward compatible with the 21064 pin layout and software

- Programmable external cache

- Set size

- Set speed

- 43-bit virtual address

- 34-bit physical address

- IEEE and VAX floating-point data types

- Performance monitoring

- 64-bit internal data paths

The 21064A and associated PALcode implement IEEE single- and doubleprecision, VAX F\_floating and G\_floating data types, and support longword (32-bit) and quadword (64-bit) integers. Byte (8-bit) and word (16-bit) support is provided by byte manipulation instructions. Limited hardware support is provided for the VAX D\_floating data type.

The 21064A consists of four independent functional units:

- Integer execution unit (Ebox)

- Floating-point unit (Fbox)

- Load/store or address unit (Abox)

- Branch unit

Other sections include the central control unit (Ibox), and the Icache and Dcache.

Ebox—Contains a 64-bit fully pipelined integer execution data path including: adder, logic box, barrel shifter, byte extract and mask, and independent integer multiplier. The Ebox also contains a 32-entry, 64-bit integer register file.

Fbox—Contains a fully pipelined floating-point unit and independent divider that supports both IEEE and VAX floating-point data types. IEEE singleprecision and double-precision floating-point data types are supported. VAX F\_floating and G\_floating data types are fully supported, and limited support is provided for the D\_floating data type.

Abox—Contains five major sections: address translation data path, load silo, write buffer, data cache interface, and the external bus interface unit (BIU). The Abox supports all integer and floating-point load and store instructions including address calculation and translation, and cache control logic.

Ibox—Performs instruction fetch, resource checks, and dual-instruction issue to the Ebox, Abox, Fbox, or branch unit. In addition, the Ibox controls pipeline stalls, aborts, and restarts.

#### **Pipeline Organization**

The 21064A uses a 7-stage pipeline for integer operate and memory reference instructions, and a 10-stage pipleline for floating-point operate instructions. The Ibox maintains state for all pipeline stages to track outstanding register writes.

#### **Cache Organization**

The 21064A contains two on-chip caches—data cache (Dcache) and instruction cache (Icache). The 21064A also supports an external cache.

Icache—Contains 16K bytes and is a direct-mapped cache with 32-byte blocks. Virtual address bit 13 and physical address bits [12:5] are the index into the cache.

Dcache—Contains 16K bytes and is a write through, read-allocate cache with 32-byte blocks. It can be used in either of two modes.

- 8K-byte direct-mapped cache (to support 21064 designs). Physical address [12:5] is the index into the cache.

- 16K-byte cache

- The Dcache appears externally as a 2-way set-associative cache.

Physical address [12:5] is the index into the cache.

- The Dcache appears internally as direct-mapped cache. Virtual address

[13] and physical address

[12:5] are the index into the cache.

External Cache—The 21064A supports an external cache that is made with readily available static RAMs. The 21064A directly controls RAM operation using its programmable external cache interface, allowing each hardware implementation to make its own external cache speed and configuration trade-offs.

The external cache interface supports cache sizes 0, 256K bytes, 512K bytes, 1M bytes, 2M bytes, 4M bytes, 8M bytes and 16M bytes. The range of operating speeds of the external cache are sub-multiples of the 21064A clock.

#### **Virtual Address Space**

The architecture virtual address is a 64-bit unsigned integer that specifies a byte location within the virtual address space. The 21064A implements a 43-bit subset of the virtual address space.

#### **Physical Address Space**

The 21064A uses a 34-bit physical address to support 16G bytes of physical address space.

#### **Backward Compatibility**

The 21064A is backward compatible with the 21064. The compatibility includes pin layout, PALcode, and application programs.

The following restrictions apply to the compatibility between the 21064A and 21064.

- The 21064A has internal pulldown resistors on inputs which are unused spare pins on the 21064. If these spare pins are unconnected on a module designed for the 21064, then there will be no migration problem with these pins.

- Two pins have been reallocated for other uses. If these pins were not used on a module designed for the 21064, then there will be no migration problem with these pins. On the 21064 the two pins are **tagEq\_l** and **tagAdr\_h 17**; on the 21064A they are **lockWE\_h** and **lockFlag\_h** respectively.

- The behavior of the **tagOK** protocol on the 21064A differs from that of the 21064. Designers should investigate the effect of the change if this protocol is used in existing 21064 modules.

Figure 1 shows a block diagram of the 21064A microprocessor.

## **2** Signal Names and Functions

The tables in this section list the various signals grouped by function. The information in the **Type** column identifies a signal as input (I), output (O), or bidirectional (B).

Signals with an **\_h** suffix are active (asserted) when high. Those with an **\_l** suffix are active (asserted) when low.

Table 1 describes the 21064A data, address, and parity/ECC bus signals.

| Signal         | Туре | Count | Function                                                                                                                                        |

|----------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| data_h [127:0] | В    | 128   | Provide the data path between the 21064A and the system.                                                                                        |

| adr_h [33:5]   | В    | 29    | Provide the address path between the 21064A and<br>the system. These address bits provide granularity<br>down to 32-byte internal cache blocks. |

| check_h [27:0] | В    | 28    | Provide a path for parity or ECC bits between the 21064A and the rest of the system.                                                            |

Table 1 Data, Address, and Parity/ECC Bus Signals

Table 2 describes the 21064A primary cache invalidate signals.

| Signal                          | Туре | Count | Function                                                                                |  |  |

|---------------------------------|------|-------|-----------------------------------------------------------------------------------------|--|--|

| iAdr_h [12:5]                   | Ι    | 8     | Used to index blocks in the Dcache for Dcache invalidates.                              |  |  |

| dInvReq_h<br>[1:0] <sup>1</sup> | Ι    | 2     | Used by external logic to invalidate the Dcache entry indexed by <b>iAdr_h [12:5]</b> . |  |  |

Table 2 Primary Cache Invalidate Signals

$^1 dInvReq\_h~1$  at PGA location C24 was a spare pin on the 21064. It has an internal pulldown that draws a maximum current of 200  $\mu A$  at 2.4 V dc.

Table 3 describes the 21064A external cache control signals.

| Signal                                | Туре | Count | Function                                                                         |                |                                           |                             |

|---------------------------------------|------|-------|----------------------------------------------------------------------------------|----------------|-------------------------------------------|-----------------------------|

| tagCEOE_h                             | 0    | 1     |                                                                                  | able during th | ol RAM chip e<br>ne 21064A cont           |                             |

| tagCtlWE_h                            | 0    | 1     | Controls tag control RAM write enable during the 21064A controlled transactions. |                |                                           |                             |

| tagCtlV_h,<br>tagCtlS_h,<br>tagCtlD_h | В    | 3     | Provide read/write path for external cache valid, shared, and dirty bits.        |                |                                           |                             |

|                                       |      |       |                                                                                  | The tagCtlS    | s of the tagCtl<br>_ <b>h</b> can be view |                             |

|                                       |      |       | tagCtIV_h                                                                        | tagCtIS_h      | tagCtID_h                                 | Meaning                     |

|                                       |      |       | L                                                                                | Х              | Х                                         | Invalid                     |

|                                       |      |       | Н                                                                                | L              | L                                         | Valid,<br>private           |

|                                       |      |       | Н                                                                                | L              | Н                                         | Valid,<br>private,<br>dirty |

|                                       |      |       |                                                                                  |                |                                           |                             |

|                                       |      |       | Н                                                                                | Н              | L                                         | Valid,<br>shared            |

Table 3 External Cache Control Signals

| Signal                         | Type Count |    | Function                                                                                                                                         |  |  |

|--------------------------------|------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| tagAdr_h<br>[33:18]            | Ι          | 16 | Carries the address contents of the tagAdr RAM to the 21064A address comparator and parity checker.                                              |  |  |

| tagAdrP_h                      | Ι          | 1  | Carries the parity contents of the tagAdr RAM to the 21064A address comparator and parity checker.                                               |  |  |

| tagOk_h,<br>tagOk_l            | Ι          | 2  | Bus interface control signals that allow external logic to stall a CPU-controlled access to the external cache RAMs at the last possible moment. |  |  |

| dataCEOE_h<br>[3:0]            | 0          | 4  | Controls data RAMs output enable or chip enable during the 21064A controlled cache accesses.                                                     |  |  |

| dataWE_h [3:0]                 | 0          | 4  | Controls data RAMs write enable during the 21064A controlled cache accesses.                                                                     |  |  |

| dataA_h [4:3]                  | 0          | 2  | Controls data RAMs <b>adr_h [4:3]</b> during the 21064A controlled cache accesses.                                                               |  |  |

| holdReq_h                      | Ι          | 1  | Asserted by external logic to gain access to the external cache.                                                                                 |  |  |

| holdAck_h                      | 0          | 1  | Asserted by the 21064A to indicate that external logic has access to the external cache.                                                         |  |  |

| dMapWE_h<br>[1:0] <sup>1</sup> | 0          | 2  | Controls the write enable inputs of the (optional)<br>data cache backmap RAM during the 21064A<br>controlled external cache reads.               |  |  |

Table 3 (Cont.)

External Cache Control Signals

<sup>1</sup>**dMapWE\_h 1** at PGA location M24 was a spare pin on the 21064.

Table 4 describes the signals which allow the 21064A to perform LDxL and STxC transactions to and from an external cache.

| Signal                  | Туре | Count | Function                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lockWE_h <sup>1</sup>   | 0    | 1     | The 21064A is able to probe Bcache for an LDxL transaction. If there is a Bcache hit, then the 21064A will assert <b>lockWE_h</b> allowing external logic to set a lock flag bit and load a lock address register.                                                                                                                                                                                    |

| lockFlag_h <sup>2</sup> | Ι    | 1     | This signal line allows external logic to indicate<br>the state of the lock flag bit (set or clear). When<br>the 21064A performs a STxC transaction, it may<br>probe the Bcache and test this signal. If the signa<br>is asserted, then the 21064A will perform the<br>write to Bcache while asserting <b>lockWE_h</b> . This<br>transaction allows the external logic to clear the<br>lock flag bit. |

Table 4 Fast Lock Mode Signals

<sup>2</sup>lockFlag\_h at PGA location R23 was used for the signal tagAdr\_h 17 by the 21064.

Table 5 describes the 21064A external cycle control signals.

| Signal        | Туре | Count | Function                                                                                                                                                                                       |              |                                  |                               |

|---------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------|-------------------------------|

| dOE_l         | Ι    | 1     |                                                                                                                                                                                                |              | to tell the 210<br>ernal write t | 064A to drive ransactions.    |

| dWSel_h [1:0] | Ι    | 2     | Used by external logic to tell the 21064A which part of the 32-byte block of write data should be driven onto the data bus.                                                                    |              |                                  |                               |

| dRAck_h [2:0] | Ι    | 3     | Informs the 21064A that read data is valid on<br>data bus, and indicates whether data should b<br>cached and whether ECC or parity checking sh<br>be attempted. Read data acknowledge types an |              |                                  | a should be<br>hecking should |

|               |      |       | dRAck_h<br>2                                                                                                                                                                                   | dRAck_h<br>1 | dRAck_h<br>0                     | Туре                          |

|               |      |       | L                                                                                                                                                                                              | L            | L                                | IDLE                          |

|               |      |       | Н                                                                                                                                                                                              | L            | L                                | OK_<br>NCACHE_<br>NCHK        |

|               |      |       | Н                                                                                                                                                                                              | L            | Н                                | OK_<br>NCACHE                 |

|               |      |       | Н                                                                                                                                                                                              | Н            | L                                | OK_<br>NCHK                   |

|               |      |       | Н                                                                                                                                                                                              | Н            | Н                                | OK                            |

Table 5

External Cycle Control Signals

| Signal         | Туре | Count | Function                                                                                           |                                               |               |                               |  |

|----------------|------|-------|----------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------|-------------------------------|--|

| cReq_h [2:0]   | 0    | 3     | Used by the 21064A to specify a cycle type at the start of an external cycle. The cycle types are: |                                               |               |                               |  |

|                |      |       | cReq_h 2                                                                                           | cReq_h 1                                      | cReq_h 0      | Туре                          |  |

|                |      |       | L                                                                                                  | L                                             | L             | IDLE                          |  |

|                |      |       | L                                                                                                  | L                                             | Н             | BARRIER                       |  |

|                |      |       | L                                                                                                  | Н                                             | L             | FETCH                         |  |

|                |      |       | L                                                                                                  | Н                                             | Н             | FETCH_M                       |  |

|                |      |       | Н                                                                                                  | L                                             | L             | READ_<br>BLOCK                |  |

|                |      |       | Н                                                                                                  | L                                             | Н             | WRITE_<br>BLOCK               |  |

|                |      |       | Н                                                                                                  | Н                                             | L             | LDL_L/<br>LDQ_L               |  |

|                |      |       | Н                                                                                                  | Н                                             | Н             | STL_C/<br>STQ_C               |  |

| cWMask_h [7:0] | 0    | 8     | during writ                                                                                        | ngword write<br>te cycles; con<br>information | tains miss ad | ldress bits and               |  |

| cAck_h [2:0]   | Ι    | 3     | Used by external logic to acknowledge an externation cycle. Acknowledge types are:                 |                                               |               |                               |  |

|                |      |       | cAck_h 2                                                                                           | cAck_h 1                                      | cAck_h 0      | Туре                          |  |

|                |      |       | L                                                                                                  | L                                             | L             | IDLE                          |  |

|                |      |       | L                                                                                                  | L                                             | Н             | HARD_<br>ERROR                |  |

|                |      |       | L                                                                                                  | Н                                             | L             | SOFT_<br>ERROR                |  |

|                |      |       | L                                                                                                  | Н                                             | Н             | STL_C_FAII<br>/STQ_C_<br>FAIL |  |

|                |      |       |                                                                                                    |                                               |               |                               |  |

Table 5 (Cont.)

External Cycle Control Signals

Table 6 describes the 21064A interrupt signals.

| Signal                   | Туре | Count | Function                                                               |                                  |                                                            |

|--------------------------|------|-------|------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------|

| irq_h [5:0]              | Ι    | 6     | These signa                                                            | l lines have two                 | uses:                                                      |

|                          |      |       |                                                                        |                                  | on they provide six<br>upts to the 21064A.                 |

|                          |      |       |                                                                        | t, they provide i<br>the 21064A. | nitialization informa-                                     |

| sysClkDiv_h <sup>1</sup> | Ι    | 1     | At reset, this line provides initialization information to the 21064A. |                                  |                                                            |

|                          |      |       | delay in CF                                                            |                                  | <b>rq_h [4:3]</b> encodes the<br>from <b>sysClkOut1</b> to |

|                          |      |       | irq_h 4                                                                | irq_h 3                          | Delay                                                      |

|                          |      |       | L                                                                      | L                                | 0                                                          |

|                          |      |       | L                                                                      | Н                                | 1                                                          |

|                          |      |       |                                                                        | т                                | 0                                                          |

|                          |      |       | Н                                                                      | L                                | 2                                                          |

Table 6

Interrupt Signals

<sup>1</sup>**sysClkDiv\_h** at PGA location AA16 was a spare pin on the 21064. It has an internal pulldown that draws a maximum current of 200  $\mu$ A at 2.4 V dc.

| Signal | Туре | Count | Function                 |                                                                              |               |

|--------|------|-------|--------------------------|------------------------------------------------------------------------------|---------------|

|        |      |       | irq_h [2:0] encode       | asserted, <b>sysClkDiv</b><br>e the value of the div<br>em clock from the CF | visor used to |

|        |      |       | sysClkDiv_h <sup>1</sup> | irq_h [2:0]                                                                  | Ratio         |

|        |      |       | L                        | LLL                                                                          | 2             |

|        |      |       | L                        | LLH                                                                          | 3             |

|        |      |       | L                        | LHL                                                                          | 4             |

|        |      |       | L                        | LHH                                                                          | 5             |

|        |      |       | L                        | H L L                                                                        | 6             |

|        |      |       | L                        | H L H                                                                        | 7             |

|        |      |       | L                        | H H L                                                                        | 8             |

|        |      |       | L                        | н н н                                                                        | 9             |

|        |      |       | Н                        | LLL                                                                          | 10            |

|        |      |       | Н                        | LLH                                                                          | 11            |

|        |      |       | Н                        | LHL                                                                          | 12            |

|        |      |       | Н                        | LHH                                                                          | 13            |

|        |      |       | Н                        | H L L                                                                        | 14            |

|        |      |       | Н                        | H L H                                                                        | 15            |

|        |      |       | Н                        | H H L                                                                        | 16            |

|        |      |       | Н                        | ННН                                                                          | 17            |

Table 6 (Cont.) Interrupt Signals

When **reset\_l** is asserted, **irq\_h 5** is used to select 128-bit or 64-bit mode. If **irq\_h 5** is asserted, then 128-bit mode is selected.

<sup>1</sup>**sysClkDiv\_h** at PGA location AA16 was a spare pin on the 21064. It has an internal pulldown that draws a maximum current of 200  $\mu$ A at 2.4 V dc.

Table 7 describes the 21064A instruction cache initialization and serial ROM interface signals.

| Signal                      | Туре | Count | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-----------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| icMode_h [2:0] <sup>1</sup> | Ι    | 3     | Determines which Icache initialization mode is<br>used after reset. The 21064A implements several<br>Icache modes used by Digital to support chip and<br>module level testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                             |      |       | icMode_h [2:0] Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                             |      |       | L L L Serial ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                             |      |       | L L H Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                             |      |       | All other combinations Digital reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| sRomOE_l                    | 0    | 1     | In serial ROM mode, supplies the output enable to<br>the external serial ROM, serving both as an output<br>enable and as a reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| sRomD_h                     | Ι    | 1     | In serial ROM mode, inputs external serial ROM data to the 21064A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| sRomClk_h                   | 0    | 1     | In serial ROM mode, supplies the clock to the external serial ROM that causes it to advance to the next bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                             |      |       | The signals <b>sRomOE_l</b> , <b>sRomD_h</b> , and<br><b>sRomClk_h</b> also serve as simple parallel I/O pins<br>to drive a diagnostic terminal. When the serial<br>ROM is not being read, output signal <b>sRomOE_l</b> is<br>false. This means that <b>sRomOE_l</b> can be wired to<br>the active high enable of an RS422 receiver driving<br>onto <b>sRomD_h</b> and to the active high enable of an<br>RS422 driver driving from <b>sRomClk_h</b> . The CPU<br>allows <b>sRomD_h</b> to be read and <b>sRomClk_h</b> to<br>be written by PALcode; this is sufficient hardware<br>support to implement a software-driven serial<br>interface. |  |

Table 7 Instruction Cache Initialization and Serial ROM Interface Signals

<sup>1</sup>**icMode\_h 2** at PGA location AD7 was a spare pin on the 21064. It has an internal pulldown that draws a maximum current of 200  $\mu$ A at 2.4 V dc.

Table 8 describes the initialization signal pins **dcOk\_h**, **reset\_l** and **reset\_SClk\_h**.

| Signal                    | Туре | Count | Function                                                                                     |

|---------------------------|------|-------|----------------------------------------------------------------------------------------------|

| dcOk_h                    | Ι    | 1     | Switches clock sources between an on-chip ring oscillator and the external clock oscillator. |

| reset_l                   | Ι    | 1     | Forces the CPU into a known state.                                                           |

| reset_SClk_h <sup>1</sup> | Ι    | 1     | A test signal. It forces the system clock divider into a known state.                        |

Table 8 Initialization Signals

$^1\textbf{reset\_SClk\_h}$  at PGA location AA11 was a spare pin on the 21064. It has an internal pulldown that draws a maximum current of 200  $\mu\text{A}$  at 2.4 V dc.

Table 9 describes the 21064A clock signals.

|                               | 0    |       |                                                                                                                                                                                                                             |

|-------------------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal                        | Туре | Count | Function                                                                                                                                                                                                                    |

| clkIn_h, clkIn_l              | Ι    | 2     | Supplies the 21064A with a differential clock from external logic.                                                                                                                                                          |

| testClkIn_h,<br>testClkIn_l   | Ι    | 2     | Test signals; should be tied to Vdd and Vss, respectively.                                                                                                                                                                  |

| cpuClkOut_h                   | 0    | 1     | Supplies the internal chip clock for use by the external interface. The low-to-high transition of <b>cpuClkOut_h</b> is the "CPU clock" used in the timing specification for the <b>tagOk_h</b> and <b>tagOk_l</b> signals. |

| sysClkOut1_h,<br>sysClkOut1_l | 0    | 2     | Provides the system clock for use by the external interface. The low-to-high transition of <b>sysClkOut1_h</b> provides the system clock that is used as a timing reference throughout this document.                       |

| sysClkOut2_h,<br>sysClkOut2_l | 0    | 2     | Provide delayed system clock to the external interface. The delay is between zero and three CPU clock cycles.                                                                                                               |

Table 9

Clock Signals

Table 10 describes the performance monitoring signals.

| Signal           | Туре | Count | Function                                                                                     |

|------------------|------|-------|----------------------------------------------------------------------------------------------|

| perf_cnt_h [1:0] | Ι    | 2     | Provides the 21064A internal performance monitoring hardware with access to off-chip events. |

Table 10

Performance Monitoring Signals

Table 11 describes some other signals common to the 21064A.

| Signal     | Туре | Count | Function                                                                                                                                    |

|------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| tristate_l | Ι    | 1     | The assertion of this signal forces all the 21064A signals, with the exception of <b>cpuClkOut_h</b> , to the high-impedance state.         |

| cont_l     | Ι    | 1     | The assertion of this signal causes the 21064A to connect all signals to Vss, with the exception of certain clock signals and <b>vRef</b> . |

| vRef       | Ι    | 1     | Supplies a reference voltage of 1.4 V to the input signal sense circuits.                                                                   |

| eclOut_h   | Ι    | 1     | Digital reserved; should be tied to Vss.                                                                                                    |

Table 11 Other Signals

## **3 Instruction Set**

This section provides information about instructions for the 21064A.

#### 3.1 Instruction Summary

This section contains a summary of all Alpha architecture instructions. All values are in hexadecimal radix. Table 12 describes the contents of the Format and Opcode columns that are in Table 13.

| Instruction<br>Format       | Format<br>Symbol | Opcode<br>Notation | Meaning                                                                                                                   |

|-----------------------------|------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| Branch                      | Bra              | 00                 | oo is the 6-bit opcode field.                                                                                             |

| Floating-<br>point          | F-P              | oo.fff             | oo is the 6-bit opcode field.<br>fff is the 11-bit function code field.                                                   |

| Memory                      | Mem              | 00                 | oo is the 6-bit opcode field.                                                                                             |

| Memory/<br>function<br>code | Mfc              | oo.ffff            | oo is the 6-bit opcode field.<br>ffff is the 16-bit function code in the<br>displacement field.                           |

| Memory/<br>branch           | Mbr              | oo.h               | oo is the 6-bit opcode field.<br>h is the high-order two bits of the<br>displacement field.                               |

| Operate                     | Opr              | oo.ff              | oo is the 6-bit opcode field.<br>ff is the 7-bit function code field.                                                     |

| PALcode                     | Pcd              | 00                 | oo is the 6-bit opcode field; the<br>particular PALcode instruction is<br>specified in the 26-bit function code<br>field. |

Table 12 Instruction Format and Opcode Notation

Table 13 shows architecture instructions. Table 14 shows qualifiers for IEEE floating-point instructions and Table 15 shows qualifiers for VAX floating-point instructions.

| Mnemonic | Format | Opcode | Description                   |

|----------|--------|--------|-------------------------------|

| ADDF     | F-P    | 15.080 | Add F_floating                |

| ADDG     | F-P    | 15.0A0 | Add G_floating                |

| ADDL     | Opr    | 10.00  | Add longword                  |

| ADDL/V   | Opr    | 10.40  | Add longword                  |

| ADDQ     | Opr    | 10.20  | Add quadword                  |

| ADDQ/V   | Opr    | 10.60  | Add quadword                  |

| ADDS     | F-P    | 16.080 | Add S_floating                |

| ADDT     | F-P    | 16.0A0 | Add T_floating                |

| AND      | Opr    | 11.00  | Logical product               |

| BEQ      | Bra    | 39     | Branch if $=$ zero            |

| BGE      | Bra    | 3E     | Branch if $\geq$ zero         |

| BGT      | Bra    | 3F     | Branch if $>$ zero            |

| BIC      | Opr    | 11.0   | Bit clear                     |

| BIS      | Opr    | 11.20  | Logical sum                   |

| BLBC     | Bra    | 38     | Branch if low bit clear       |

| BLBS     | Bra    | 3C     | Branch if low bit set         |

| BLE      | Bra    | 3B     | Branch if $\leq$ zero         |

| BLT      | Bra    | 3A     | Branch if $<$ zero            |

| BNE      | Bra    | 3D     | Branch if $\neq$ zero         |

| BR       | Bra    | 30     | Unconditional branch          |

| BSR      | Mbr    | 34     | Branch to subroutine          |

| CALL_PAL | Pcd    | 00     | Trap to PALcode               |

| CMOVEQ   | Opr    | 11.24  | CMOVE if = zero               |

| CMOVGE   | Opr    | 11.46  | CMOVE if $\geq$ zero          |

| CMOVGT   | Opr    | 11.66  | CMOVE if > zero               |

| CMOVLBC  | Opr    | 11.16  | CMOVE if low bit clear        |

| CMOVLBS  | Opr    | 11.14  | CMOVE if low bit set          |

| CMOVLE   | Opr    | 11.64  | CMOVE if $\leq$ zero          |

| CMOVLT   | Opr    | 11.44  | CMOVE if < zero               |

| CMOVNE   | Opr    | 11.26  | CMOVE if $\neq$ zero          |

| CMPBGE   | Opr    | 10.0F  | Compare byte                  |

| CMPEQ    | Opr    | 10.2D  | Compare signed quadword equal |

| CMPGEQ   | F-P    | 15.0A5 | Compare G_floating equal      |

Table 13 Architecture Instructions

| CMPGLEF-P15.0A7Compare G_floating less<br>equalCMPGLTF-P15.0A6Compare G_floating less<br>equalCMPLEOpr10.6DCompare signed quadw<br>than or equalCMPLTOpr10.4DCompare signed quadw<br>thanCMPTQF-P16.0A5Compare T_floating less<br>equalCMPTLEF-P16.0A6Compare T_floating less<br>equalCMPTLTF-P16.0A6Compare T_floating less<br>equalCMPTLTF-P16.0A6Compare T_floating less<br>equalCMPULEOpr10.3DCompare unsigned quad<br>less than or equalCMPULTOpr10.1DCompare unsigned quad<br>less than or equalCMPULTOpr10.1DCompare unsigned quad<br>less thanCPYSF-P17.020Copy signCPYSEF-P15.0ACConvert D_floating to GCVTGGF-P15.0ACConvert G_floating to GCVTGFF-P15.0ACConvert G_floating to qCVTQF-P15.0ACConvert G_floating to qCVTQFF-P15.0BCConvert quadword to FCVTQGF-P15.0BCConvert quadword to GCVTQLF-P17.030Convert quadword to IOCVTQL/VF-P17.30Convert quadword to IOCVTQSF-P16.0BCConvert quadword to IOCVTQSF-P16.0BCConvert quadword to IO                      |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| CMPGLTF-P15.0A6Compare G_floating lessCMPLEOpr10.6DCompare signed quadwer<br>than or equalCMPLTOpr10.4DCompare signed quadwer<br>thanCMPTEQF-P16.0A5Compare T_floating equ<br>equalCMPTLEF-P16.0A7Compare T_floating less<br>equalCMPTLTF-P16.0A6Compare T_floating less<br>equalCMPTUNF-P16.0A6Compare T_floating less<br>equalCMPULEOpr10.3DCompare tunsigned quad<br>less than or equalCMPULTOpr10.1DCompare unsigned quad<br>less than or equalCMPULTOpr10.1DCompare unsigned quad<br>less thanCPYSF-P17.020Copy signCPYSEF-P17.022Copy sign and exponentCVTGGF-P15.0ADConvert G_floating to GCVTGQF-P15.0AFConvert G_floating to GCVTGQF-P15.0AFConvert G_floating to GCVTQGF-P15.0BEConvert G_floating to GCVTQGF-P15.0BCConvert G_floating to GCVTQGF-P15.0BCConvert quadword to GCVTQSF-P15.0BEConvert quadword to GCVTQSF-P17.030Convert quadword to GCVTQSF-P17.030Convert quadword to IoCVTQSF-P16.0BEConvert quadword to IoCVTQSF-P16.0BEConvert quadword to Io | than or  |

| CMPLTOpr10.4DCompare signed quadwr<br>thanCMPTEQF-P16.0A5Compare T_floating equ<br>cqualCMPTLEF-P16.0A7Compare T_floating less<br>equalCMPTLTF-P16.0A6Compare T_floating less<br>equalCMPTUNF-P16.0A4Compare T_floating und<br>compare T_floating und<br>less than or equalCMPULEOpr10.3DCompare unsigned quad<br>less than or equalCMPULTOpr10.1DCompare unsigned quad<br>less thanCPYSF-P17.020Copy signCPYSEF-P17.022Copy sign and exponentCPYSNF-P15.09EConvert D_floating to GCVTGGF-P15.0ADConvert G_floating to GCVTGQF-P15.0AFConvert G_floating to quCVTQGF-P15.0AFConvert G_floating to quCVTQGF-P15.0BEConvert quadword to fCVTQGF-P17.030Convert quadword to FCVTQL/SVF-P17.30Convert quadword to IoCVTQSF-P16.0BCConvert quadword to IOCVTQSF-P16.0BEConvert quadword to IOCVTQTF-P16.0BCConvert quadword to T                                                                                                                                                 | than     |

| CMPTEQF-P16.0A5Compare T_floating equCMPTLEF-P16.0A7Compare T_floating less<br>equalCMPTLTF-P16.0A6Compare T_floating less<br>equalCMPTUNF-P16.0A6Compare T_floating und<br>Compare Unsigned quad<br>less than or equalCMPULEOpr10.3DCompare unsigned quad<br>less than or equalCMPULTOpr10.1DCompare unsigned quad<br>less thanCPYSF-P17.020Copy signCPYSEF-P17.022Copy sign and exponentCVTDGF-P15.04DConvert D_floating to GCVTGDF-P15.0ADConvert G_floating to DCVTGFF-P15.0ACConvert G_floating to PCVTGQF-P15.0AFConvert G_floating to QCVTQGF-P15.0BEConvert quadword to PCVTQGF-P17.030Convert quadword to GCVTQLF-P17.030Convert quadword to IOCVTQSF-P17.130Convert quadword to IOCVTQSF-P16.0BEConvert quadword to SCVTQTF-P16.0BEConvert quadword to T                                                                                                                                                                                                          | ord less |

| CMPTLEF-P16.0A7Compare T_floating less<br>equalCMPTLTF-P16.0A6Compare T_floating less<br>equalCMPTUNF-P16.0A4Compare T_floating und<br>Compare unsigned quad<br>less than or equalCMPULEOpr10.3DCompare unsigned quad<br>less than or equalCMPULTOpr10.1DCompare unsigned quad<br>less thanCPYSF-P17.020Copy signCPYSEF-P17.022Copy sign negateCVTDGF-P15.09EConvert D_floating to GCVTGDF-P15.0ACConvert G_floating to GCVTGQF-P15.0ACConvert G_floating to GCVTQGQF-P15.0ACConvert G_floating to qCVTQFF-P15.0ACConvert G_floating to qCVTQFF-P17.010Convert longword to quCVTQFF-P17.030Convert quadword to FCVTQLF-P17.030Convert quadword to IoCVTQL/VF-P17.30Convert quadword to IoCVTQSF-P16.0BCConvert quadword to IoCVTQTF-P16.0BCConvert quadword to Io                                                                                                                                                                                                           | ord less |

| CMPTLEF-P16.0A7Compare T_floating less<br>equalCMPTLTF-P16.0A6Compare T_floating less<br>equalCMPTUNF-P16.0A4Compare T_floating und<br>Compare unsigned quad<br>less than or equalCMPULEOpr10.3DCompare unsigned quad<br>less than or equalCMPULTOpr10.1DCompare unsigned quad<br>less thanCPYSF-P17.020Copy signCPYSEF-P17.022Copy sign negateCVTDGF-P15.09EConvert D_floating to GCVTGDF-P15.0ACConvert G_floating to GCVTGQF-P15.0ACConvert G_floating to GCVTQGQF-P15.0ACConvert G_floating to qCVTQFF-P15.0ACConvert G_floating to qCVTQFF-P17.010Convert longword to quCVTQFF-P17.030Convert quadword to FCVTQLF-P17.030Convert quadword to IoCVTQL/VF-P17.30Convert quadword to IoCVTQSF-P16.0BCConvert quadword to IoCVTQTF-P16.0BCConvert quadword to Io                                                                                                                                                                                                           | al       |

| CMPTUNF-P16.0A4Compare T_floating und<br>Compare unsigned quad<br>less than or equalCMPULEOpr10.3DCompare unsigned quad<br>less than or equalCMPULTOpr10.1DCompare unsigned quad<br>less thanCPYSF-P17.020Copy signCPYSEF-P17.022Copy sign and exponentCPYSNF-P15.09EConvert D_floating to GCVTDGF-P15.0ADConvert G_floating to DCVTGDF-P15.0ACConvert G_floating to FCVTGQF-P15.0AFConvert G_floating to qCVTQFF-P15.0BEConvert quadword to FCVTQGF-P15.0BEConvert quadword to GCVTQFF-P15.0BEConvert quadword to GCVTQLF-P17.030Convert quadword to GCVTQL/SVF-P17.30Convert quadword to loCVTQSF-P16.0BCConvert quadword to SCVTQTF-P16.0BEConvert s_floating to T                                                                                                                                                                                                                                                                                                       |          |

| CMPULEOpr10.3DCompare unsigned quad<br>less than or equalCMPULTOpr10.1DCompare unsigned quad<br>less thanCPYSF-P17.020Copy signCPYSEF-P17.022Copy sign negateCVTDGF-P15.09EConvert D_floating to GCVTGDF-P15.0ADConvert G_floating to DCVTGFF-P15.0AFConvert G_floating to GCVTGQF-P15.0AFConvert G_floating to GCVTQFF-P15.0AFConvert G_floating to GCVTQQF-P15.0AFConvert G_floating to GCVTQVF-P15.0AFConvert G_floating to GCVTQVF-P17.010Convert G_floating to GCVTQVF-P17.030Convert quadword to GCVTQL/SVF-P17.030Convert quadword to IoCVTQSF-P17.130Convert quadword to IoCVTQSF-P16.0BCConvert quadword to SCVTQTF-P16.0BEConvert quadword to T                                                                                                                                                                                                                                                                                                                   | than     |

| CMPULTOpr10.1DLess than or equal<br>compare unsigned quad<br>less thanCPYSF-P17.020Copy sign<br>Copy signCPYSEF-P17.022Copy sign and exponentCPYSNF-P17.021Copy sign negateCVTDGF-P15.09EConvert D_floating to GCVTGDF-P15.0ADConvert G_floating to DCVTGFF-P15.0ACConvert G_floating to FCVTGQF-P15.0AFConvert G_floating to GCVTQQF-P15.0AFConvert G_floating to GCVTQQF-P15.0AFConvert G_floating to GCVTQQF-P15.0AFConvert G_floating to GCVTQFF-P15.0BEConvert G_floating to GCVTQFF-P17.010Convert longword to quCVTQFF-P15.0BEConvert quadword to FCVTQGF-P17.030Convert quadword to GCVTQL/SVF-P17.130Convert quadword to loCVTQSF-P16.0BCConvert quadword to SCVTQTF-P16.0BEConvert quadword to T                                                                                                                                                                                                                                                                  | rdered   |

| CMPULTOpr10.1DCompare unsigned quad<br>less thanCPYSF-P17.020Copy signCPYSEF-P17.022Copy sign and exponentCPYSNF-P17.021Copy sign negateCVTDGF-P15.09EConvert D_floating to GCVTGDF-P15.0ADConvert G_floating to DCVTGFF-P15.0ACConvert G_floating to FCVTGQF-P15.0AFConvert G_floating to qCVTQQF-P15.0AFConvert G_floating to qCVTQQF-P15.0BEConvert quadword to quCVTQFF-P15.0BEConvert quadword to GCVTQLF-P17.030Convert quadword to GCVTQL/SVF-P17.530Convert quadword to loCVTQSF-P16.0BCConvert quadword to SCVTQTF-P16.0BEConvert quadword to T                                                                                                                                                                                                                                                                                                                                                                                                                    | word     |

| CPYSEF-P17.022Copy sign and exponentCPYSNF-P17.021Copy sign negateCVTDGF-P15.09EConvert D_floating to GCVTGDF-P15.0ADConvert G_floating to DCVTGFF-P15.0ACConvert G_floating to FCVTGQF-P15.0AFConvert G_floating to quCVTQGF-P15.0AFConvert G_floating to quCVTQQF-P15.0BEConvert longword to quCVTQFF-P15.0BEConvert quadword to FCVTQGF-P15.0BEConvert quadword to GCVTQLF-P17.030Convert quadword to loCVTQL/SVF-P17.130Convert quadword to loCVTQSF-P16.0BCConvert quadword to SCVTQTF-P16.0BEConvert quadword to TCVTSTF-P16.2ACConvert S_floating to T                                                                                                                                                                                                                                                                                                                                                                                                               | word     |

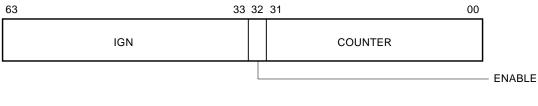

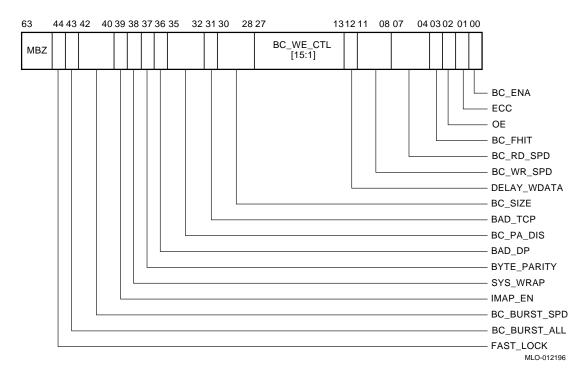

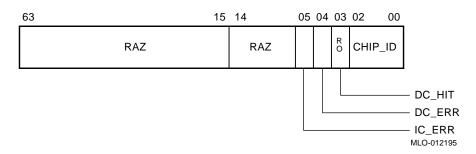

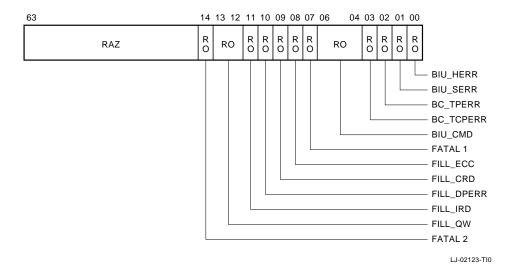

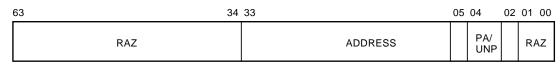

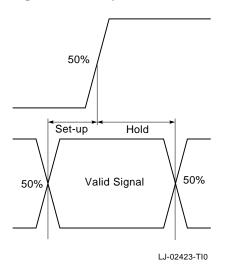

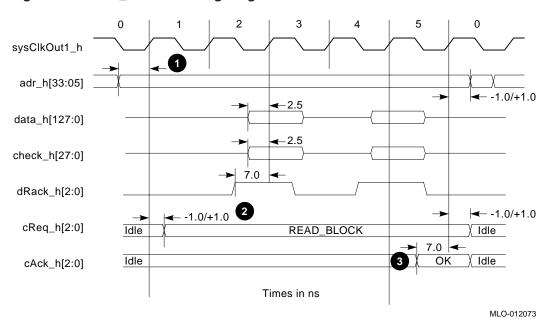

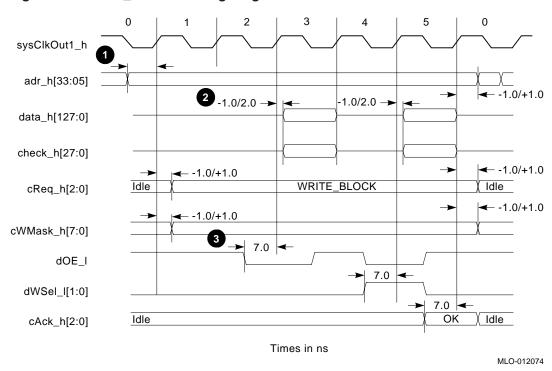

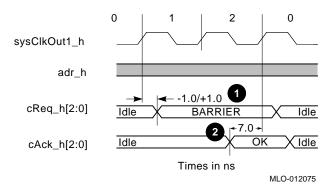

| CPYSEF-P17.022Copy sign and exponentCPYSNF-P17.021Copy sign negateCVTDGF-P15.09EConvert D_floating to GCVTGDF-P15.0ADConvert G_floating to DCVTGFF-P15.0ACConvert G_floating to FCVTGQF-P15.0AFConvert G_floating to quCVTQQF-P15.0AFConvert G_floating to quCVTQQF-P17.010Convert longword to quCVTQFF-P15.0BEConvert quadword to FCVTQGF-P15.0BEConvert quadword to GCVTQLF-P17.030Convert quadword to loCVTQL/SVF-P17.130Convert quadword to loCVTQSF-P16.0BCConvert quadword to SCVTQTF-P16.0BEConvert quadword to TCVTSTF-P16.2ACConvert S_floating to T                                                                                                                                                                                                                                                                                                                                                                                                               |          |