## Digital Semiconductor Alpha 21064 and Alpha 21064A Microprocessors

## Hardware Reference Manual

Order Number: EC-Q9ZUC-TE

Abstract: This document contains information about the following Alpha microprocessors: 21064-150, 21064-166, 21064-200, 21064A-200, 21064A-233, 21064A-275, 21064A-275-PC, and 21064A-300.

Revision/Update Information:

This manual supersedes the *Alpha 21064* and *Alpha 21064A Microprocessors Hardware Reference Manual* (EC–Q9ZUB–TE).

Digital Equipment Corporation Maynard, Massachusetts

#### June 1996

While Digital believes the information included in this publication is correct as of the date of publication, it is subject to change without notice.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

© Digital Equipment Corporation 1996. All rights reserved. Printed in U.S.A.

AlphaGeneration, Digital, Digital Semiconductor, OpenVMS, VAX, VAX DOCUMENT, the AlphaGeneration design mark, and the DIGITAL logo are trademarks of Digital Equipment Corporation.

Digital Semiconductor is a Digital Equipment Corporation business.

GRAFOIL is a registered trademark of Union Carbide Corporation. Windows NT is a trademark of Microsoft Corporation.

All other trademarks and registered trademarks are the property of their respective owners.

This document was prepared using VAX DOCUMENT Version 2.1.

# Contents

| Pı | Preface |                                        | xix  |

|----|---------|----------------------------------------|------|

| 1  | Introdu | uction to the 21064/21064A             |      |

|    | 1.1     | Introduction                           | 1–1  |

|    | 1.2     | The Architecture                       | 1–1  |

|    | 1.3     | Chip Features                          | 1–2  |

|    | 1.4     | Backward Compatibility                 | 1–4  |

|    | 1.5     | Section 1.5 21064A-275-PC Differences  | 1–4  |

| 2  | Interna | I Architecture                         |      |

|    | 2.1     | Introduction                           | 2–1  |

|    | 2.2     | 21064/21064A Overview                  | 2–3  |

|    | 2.3     | Ibox                                   | 2–4  |

|    | 2.3.1   | Branch Prediction Logic                | 2–5  |

|    | 2.3.1.1 | 21064 Branch Prediction Logic          | 2–5  |

|    | 2.3.1.2 | 21064A Branch Prediction Logic         | 2–5  |

|    | 2.3.1.3 |                                        | 2–6  |

|    | 2.3.2   | Instruction Translation Buffers (ITBs) | 2–6  |

|    | 2.3.3   | Interrupt Logic                        | 2–7  |

|    | 2.3.4   | Performance Counters                   | 2–8  |

|    | 2.4     | Ebox                                   | 2–10 |

|    | 2.5     | Abox                                   | 2–10 |

|    | 2.5.1   | Data Translation Buffer (DTB)          | 2–10 |

|    | 2.5.2   | Bus Interface Unit (BIU)               | 2–12 |

|    | 2.5.3   | Load Silos                             | 2–12 |

|    | 2.5.4   | Write Buffer                           | 2–13 |

|    | 2.6     | Fbox                                   | 2–15 |

|    | 2.6.1   | Fbox Exception Handling                | 2–16 |

|    | 2.7     | IEEE Floating-Point Conformance        | 2–19 |

|    | 2.8     | Cache Organization                     | 2–22 |

|    |         |                                        |      |

| 2.8.1   | 21064/21064A Instruction Cache (Icache)       | 2–22 |

|---------|-----------------------------------------------|------|

| 2.8.1.1 | 21064 Instruction Cache (Icache)              | 2–22 |

| 2.8.1.2 | 21064A Instruction Cache (Icache)             | 2–22 |

| 2.8.1.3 | 21064/21064A Icache Stream Buffer             | 2–22 |

| 2.8.2   | 21064/21064A Data Cache (Dcache)              | 2–23 |

| 2.8.2.1 | 21064 Data Cache (Dcache)                     | 2–23 |

| 2.8.2.2 | 21064A Data Cache (Dcache)                    | 2–23 |

| 2.9     | Pipeline Organization                         | 2–23 |

| 2.9.1   | Static and Dynamic Stages                     | 2–25 |

| 2.9.2   | Aborts                                        | 2–25 |

| 2.9.3   | Non-Issue Conditions                          | 2–26 |

| 2.10    | Scheduling and Issuing Rules                  | 2–27 |

| 2.10.1  | Instruction Class Definition                  | 2–27 |

| 2.10.2  | Producer-Consumer Latency                     | 2–28 |

| 2.10.3  | Producer-Producer Latency                     | 2–30 |

| 2.10.4  | Instruction Issue Rules                       | 2–30 |

| 2.10.5  | Dual Issue Table                              | 2–31 |

| 2.11    | PALcode                                       | 2–34 |

| 2.11.1  | Architecturally Reserved PALcode Instructions | 2–34 |

#### 3 Instruction Set

| 3.1   | Scope                            | 3–1  |

|-------|----------------------------------|------|

| 3.1.1 | Instruction Summary              | 3–1  |

| 3.1.2 | IEEE Floating-Point Instructions | 3–7  |

| 3.1.3 | VAX Floating-Point Instructions  | 3–9  |

| 3.1.4 | Required PALcode Function Codes  | 3–10 |

| 3.1.5 | Opcodes Reserved for PALcode     | 3–10 |

| 3.1.6 | Opcodes Reserved for Digital     | 3–10 |

## 4 Privileged Architecture Library Code

| 4.1     | Introduction         | 4–1  |

|---------|----------------------|------|

| 4.2     | PALcode              | 4–1  |

| 4.3     | PALmode Environment  | 4–2  |

| 4.4     | Invoking PALcode     | 4–3  |

| 4.4.1   | CALL_PAL Instruction | 4–5  |

| 4.5     | PALcode Entry Points | 4–6  |

| 4.6     | PALmode Restrictions | 4–9  |

| 4.7     | Memory Management    | 4–16 |

| 4.7.1   | TB Miss Flows        | 4–16 |

| 4.7.1.1 | ITB Miss             | 4–16 |

| 4.7.1.2 | DTB Miss             | 4–18 |

| 4.8   | 21064/21064A Implementation of the Architecturally Reserved |      |

|-------|-------------------------------------------------------------|------|

|       | Opcodes Instructions                                        | 4–19 |

| 4.8.1 | HW_MFPR and HW_MTPR Instructions                            | 4–20 |

| 4.8.2 | HW_LD and HW_ST Instructions                                | 4–23 |

| 4.8.3 | HW_REI Instruction                                          | 4–24 |

| 4.8.4 | Required PALcode Instructions                               | 4–25 |

|       |                                                             |      |

## 5 Internal Processor Registers

| 5.1     | Introduction                                              | 5–1  |

|---------|-----------------------------------------------------------|------|

| 5.2     | Ibox Internal Processor Registers                         | 5–1  |

| 5.2.1   | Translation Buffer Tag Register (TB_TAG)                  | 5–1  |

| 5.2.2   | Instruction Translation Buffer Page Table Entry Register  |      |

|         | (ITB_PTE)                                                 | 5–2  |

| 5.2.3   | Instruction Cache Control and Status Register (ICCSR)     | 5–3  |

| 5.2.3.1 | Performance Counters                                      | 5–6  |

| 5.2.4   | Instruction Translation Buffer Page Table Entry Temporary |      |

|         | Register (ITB_PTE_TEMP)                                   | 5–8  |

| 5.2.5   | Exceptions Address Register (EXC_ADDR)                    | 5–9  |

| 5.2.6   | Clear Serial Line Interrupt Register (SL_CLR)             | 5–10 |

| 5.2.7   | Serial Line Receive Register (SL_RCV)                     | 5–11 |

| 5.2.8   | Instruction Translation Buffer ZAP Register (ITBZAP)      | 5–11 |

| 5.2.9   | Instruction Translation Buffer ASM Register (ITBASM)      | 5–12 |

| 5.2.10  | Instruction Translation Buffer IS Register (ITBIS)        | 5–12 |

| 5.2.11  | Processor Status Register (PS)                            | 5–12 |

| 5.2.12  | Exception Summary Register (EXC_SUM)                      | 5–12 |

| 5.2.13  | PAL_BASE Address Register (PAL_BASE)                      | 5–14 |

| 5.2.14  | Hardware Interrupt Request Register (HIRR)                | 5–14 |

| 5.2.15  | Software Interrupt Request Register (SIRR)                | 5–16 |

| 5.2.16  | Asynchronous Trap Request Register (ASTRR)                | 5–17 |

| 5.2.17  | Hardware Interrupt Enable Register (HIER)                 | 5–18 |

| 5.2.18  | Software Interrupt Enable Register (SIER)                 | 5–19 |

| 5.2.19  | AST Interrupt Enable Register (ASTER)                     | 5–20 |

| 5.2.20  | Serial Line Transmit Register (SL_XMIT)                   | 5–20 |

| 5.3     | Abox Internal Processor Registers                         | 5–21 |

| 5.3.1   | Translation Buffer Control Register (TB_CTL)              | 5–21 |

| 5.3.2   | Data Translation Buffer Page Table Entry Register         |      |

|         | (DTB_PTE)                                                 | 5–21 |

| 5.3.3   | Data Translation Buffer Page Table Entry Temporary        |      |

|         | Register (DTB_PTE_TEMP)                                   | 5–22 |

| 5.3.4   | Memory Management Control and Status Register             |      |

|         | (MM_CSR)                                                  | 5–23 |

| 5.3.5   | Virtual Address Register (VA)                             | 5–24 |

| Data Translation Buffer ZAP Register (DTBZAP)      | 5–24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Translation Buffer ASM Register (DTBASM)      | 5–24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Data Translation Buffer Invalidate Single Register |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (DTBIS)                                            | 5–24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Flush Instruction Cache Register (FLUSH_IC)        | 5–24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Flush Instruction Cache ASM Register               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (FLUSH_IC_ASM)                                     | 5–24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

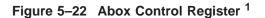

| Abox Control Register (ABOX_CTL)                   | 5–24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Alternate Processor Mode Register (ALT_MODE)       | 5–28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

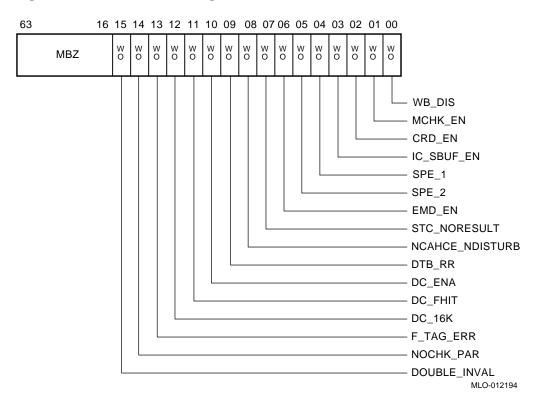

| Cycle Counter Register (CC)                        | 5–28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

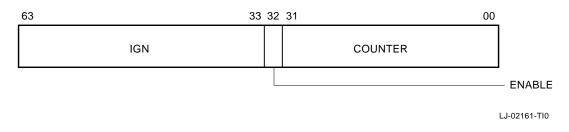

| Cycle Counter Control Register (CC_CTL)            | 5–29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bus Interface Unit Control Register (BIU_CTL)      | 5–30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\partial$ $\langle$ = $J'$                        | 5–35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                    | 5–35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

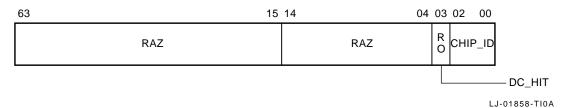

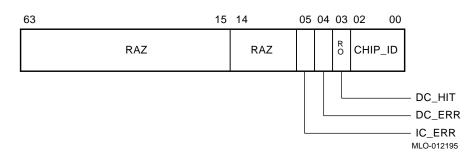

| Bus Interface Unit Status Register (BIU_STAT)      | 5–36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\partial$ $\langle$ $=$ $\rangle$                 | 5–39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fill Address Register (FILL_ADDR)                  | 5–40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fill Syndrome Register (FILL_SYNDROME)             | 5–41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Backup Cache Tag Register (BC_TAG)                 | 5–43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PAL_TEMP Registers                                 | 5–44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Lock Registers                                     | 5–44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Internal Processor Registers Reset State           | 5–45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                    | Data Translation Buffer ASM Register (DTBASM)Data Translation Buffer Invalidate Single Register(DTBIS)Flush Instruction Cache Register (FLUSH_IC)Flush Instruction Cache ASM Register(FLUSH_IC_ASM)Abox Control Register (ABOX_CTL)Alternate Processor Mode Register (ALT_MODE)Cycle Counter Register (CC)Cycle Counter Control Register (DC_STAT—21064 Only)Bus Interface Unit Control Register (BIU_CTL)Data Cache Status Register (C_STAT, 21064A Only)Bus Interface Unit Status Register (BIU_ADDR)Fill Address Register (FILL_ADDR)Fill Syndrome Register (FILL_SYNDROME)Backup Cache Tag Register (BC_TAG)PAL_TEMP Registers |

## 6 External Interface

| Introduction                               | 6–1          |

|--------------------------------------------|--------------|

| Logic Symbol                               | 6–1          |

| Signal Names and Functions                 | 6–4          |

| Bus Transactions                           | 6–14         |

| Reset                                      | 6–14         |

|                                            | 6–18         |

| Fast External Cache Write Hit              | 6–19         |

| External Cache Write Timing (Delayed Data) | 6–20         |

| READ_BLOCK                                 | 6–21         |

|                                            | 6–24         |

|                                            | 6–24         |

|                                            | 6–28         |

|                                            | 6–29         |

|                                            | 6–29         |

|                                            | 6–29         |

|                                            | 6–29         |

|                                            | 6–30         |

| 3 Noncached Loads                          | 6–31         |

|                                            | Logic Symbol |

| 6.4.11  | BARRIER                                               | 6–32         |

|---------|-------------------------------------------------------|--------------|

| 6.4.12  | FETCH                                                 | 6–33         |

| 6.4.13  | FETCH_M                                               | 6–34         |

|         | terface Operation                                     | 6–34         |

| 6.5.1   | Clocks                                                | 6–34         |

| 6.5.2   | 21064/21064A Initialization                           | 6–36         |

| 6.5.3   | Internal Cache/Primary Cache Invalidate               | 6–38         |

| 6.5.3.1 | 21064 Primary Cache Invalidate                        | 6–38         |

| 6.5.3.2 | 21064A Primary Cache Invalidate                       | 6–39         |

| 6.5.3.3 | Backmap                                               | 6–39         |

| 6.5.4   | External Cache Control                                | 6–41         |

| 6.5.4.1 | tagAdr RAM                                            | 6–42         |

| 6.5.4.2 | tagCtl RAM                                            | 6–43         |

| 6.5.4.3 | Data RAM                                              | 6–44         |

| 6.5.4.4 | holdReq_h and holdAck_h External Cache Access         | 6–45         |

| 6.5.4.5 | tagOk_h and tagOk_l External Cache Access             | 6–46         |

| 6.5.4.6 | External RAM Timing                                   | 6–47         |

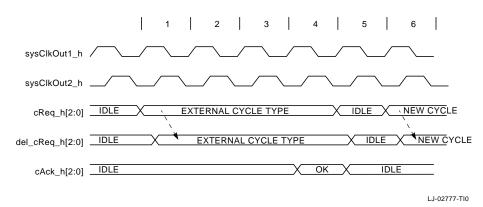

| 6.5.5   | Bus Cycle Control                                     | 6–48         |

| 6.5.5.1 | Cycle Request.                                        | 6–48         |

| 6.5.5.2 | Cycle Write Masks                                     | 6–49         |

| 6.5.5.3 | Cycle Acknowledgment                                  | 6–50         |

| 6.5.5.4 | Read Data Acknowledgment                              | 6–51         |

| 6.5.5.5 | Support for Wrapped Read Transactions                 | 6-52         |

| 6.5.5.6 | Enabling the Data Bus                                 | 6–53         |

| 6.5.5.7 | Selecting Write Data                                  | 6–54         |

| 6.5.6   | 64-Bit Mode                                           | 0–54<br>6–54 |

| 6.5.7   | Instruction Cache Initialization/Serial ROM Interface | 0–54<br>6–56 |

| 6.5.7.1 | Implementing the Serial Line Interface                | 0–50<br>6–58 |

| 6.5.8   |                                                       | 6–58<br>6–59 |

|         | Interrupts                                            | 6–59<br>6–59 |

| 6.5.9   |                                                       |              |

| 6.5.9.1 | Address Bus—adr_h [33:5]                              | 6–59         |

| 6.5.9.2 | Data Bus—data_h [127:0]                               | 6-60         |

| 6.5.9.3 | Parity/ECC Bus—check_h [27:0]                         | 6-60         |

| 6.5.10  | Performance Monitoring                                | 6–63         |

| 6.5.11  | Various Other Signals                                 | 6–63         |

|         | ardware Error Handling                                | 6-64         |

| 6.6.1   | Single-bit Errors                                     | 6–65         |

| 6.6.2   | Double-bit ECC Errors                                 | 6–66         |

| 6.6.3   | BIU Single Errors                                     | 6–67         |

| 6.6.4   | Multiple Errors                                       | 6–69         |

| 6.6.5   | Cache Parity Errors—21064A Only                       | 6–70         |

| 6.6.5.1 | Dcache Parity Errors—21064A Only                      | 6–70         |

| 6.6.5.2 | Icache Parity Errors—21064A Only                      | 6–70         |

|         |                                                       |              |

#### 7 Electrical Data

| 7.1     | Introduction                                | 7–1  |

|---------|---------------------------------------------|------|

| 7.2     | Absolute Maximum Ratings                    | 7–1  |

| 7.2.1   | Absolute Operating Limits                   | 7–2  |

| 7.3     | dc Electrical Data                          | 7–2  |

| 7.3.1   | Power Supply                                | 7–2  |

| 7.3.1.1 | Power Consideration                         | 7–2  |

| 7.3.1.2 | Reference Supply                            | 7–3  |

| 7.3.2   | Input Clocks                                | 7–3  |

| 7.3.3   | Signal Pins                                 | 7–4  |

| 7.3.4   | dc Power Dissipation                        | 7–5  |

| 7.4     | ac Electrical Data                          | 7–6  |

| 7.4.1   | Reference Supply                            | 7–6  |

| 7.4.2   | Input Clocks Frequency                      | 7–7  |

| 7.4.3   | Test Specification                          | 7–9  |

| 7.4.4   | Fast Cycles on External Cache               | 7–10 |

| 7.4.4.1 | Fast Read Cycles                            | 7–11 |

| 7.4.4.2 | Fast Write Cycles                           | 7–11 |

| 7.4.5   | External Cycles                             | 7–12 |

| 7.4.6   | tagEq_l (21064 only)                        | 7–22 |

| 7.4.7   | 21064 tagOk Synchronization                 | 7–22 |

| 7.4.8   | 21064A tagOk Synchronization                | 7–23 |

| 7.4.9   | Tester Considerations                       | 7–24 |

| 7.4.9.1 | Asynchronous Inputs                         | 7–24 |

| 7.4.9.2 | Signals Timed from CPU Clock                | 7–24 |

| Therma  | al Management                               |      |

| 8.1     | Introduction                                | 8–1  |

| 8.2     | Thermal Device Characteristics              | 8–2  |

| 8.2.1   | 21064/21064A Die and Package                | 8-2  |

| 8.2.2   | Power Consideration                         | 8–3  |

| 8.2.3   | Relationships Between Thermal Impedance and | 0-0  |

| 0.2.0   | Temperatures                                | 8–3  |

| 8.3     | Thermal Management Techniques               | 8–6  |

| 0.0     | merman management recumques                 | 00   |

| 8.3     | Thermal Management Techniques                       | 8–6  |

|---------|-----------------------------------------------------|------|

| 8.3.1   | Thermal Characteristics with a Heat Sink and Forced |      |

|         | Air                                                 | 8–6  |

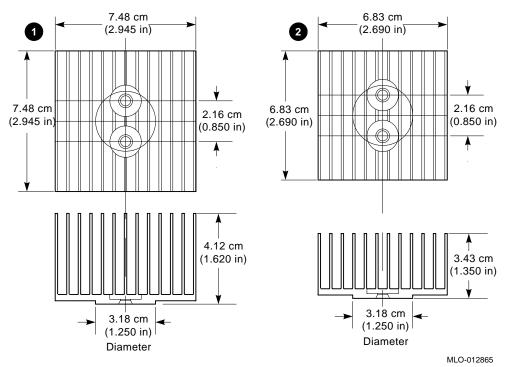

| 8.3.2   | Heat Sink Design Considerations                     | 8–7  |

| 8.3.3   | Package and Heat Sink Thermal Performance           | 8–7  |

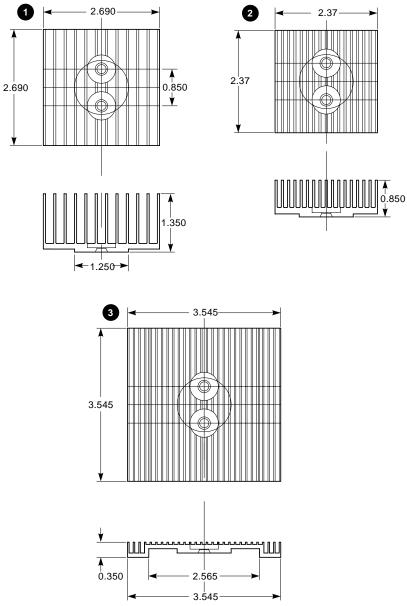

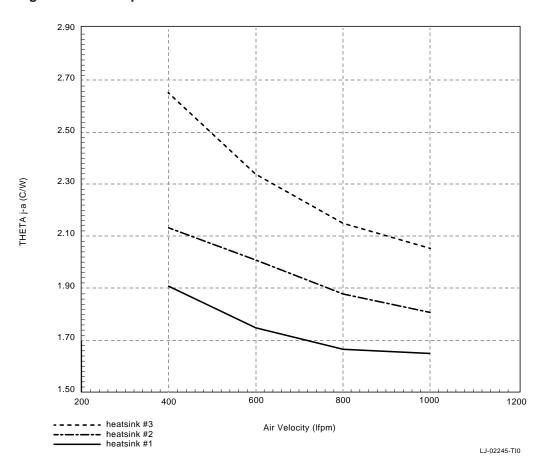

| 8.3.3.1 | Comparison of Thermal Performance of Various Heat   |      |

|         | Sink Designs                                        | 8–12 |

| 8.3.4 | Device Thermal Characteristics in Forced Air Without Heat |      |

|-------|-----------------------------------------------------------|------|

|       | Sink                                                      | 8–16 |

| 8.4   | Critical Parameters of Thermal Design                     | 8–16 |

|       |                                                           |      |

## 9 Signal Integrity

| 9.1     | Introduction                                              | 9—1  |

|---------|-----------------------------------------------------------|------|

| 9.2     | Power Supply Considerations                               | 9—1  |

| 9.2.1   | Decoupling                                                | 9–2  |

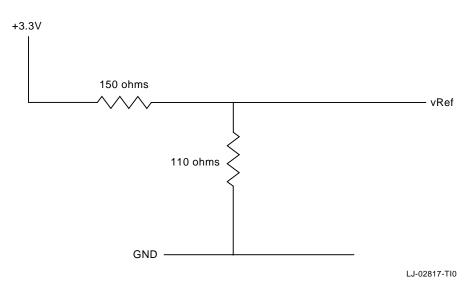

| 9.2.2   | Reference Voltage (vRef)                                  | 9–2  |

| 9.2.3   | Power Supply Sequencing                                   | 9–3  |

| 9.3     | I/O Drivers                                               | 9–4  |

| 9.3.1   | I/O Driver Pins                                           | 9–4  |

| 9.3.1.1 | Maximum Received Voltage Levels                           | 9–5  |

| 9.3.1.2 | Clamping Action of I/Os                                   | 9–5  |

| 9.3.1.3 | Pin Capacitances                                          | 9–5  |

| 9.3.2   | I/O Driver Characteristics                                | 9–5  |

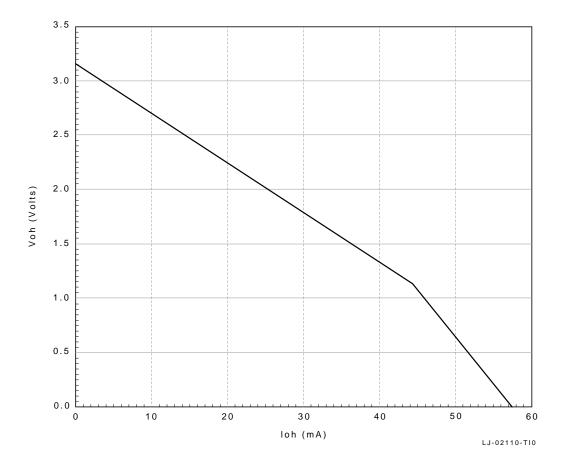

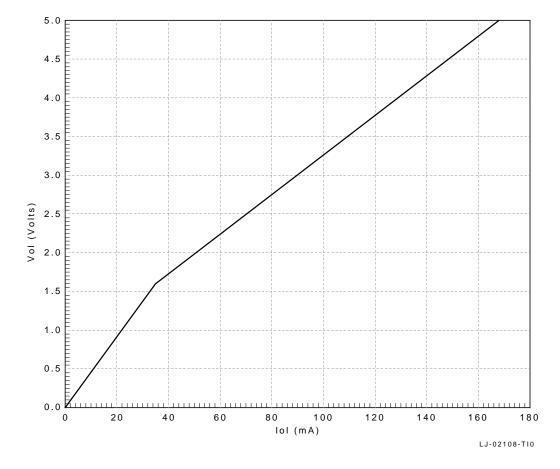

| 9.3.2.1 | Voltage/Current (VI) Curves                               | 9–5  |

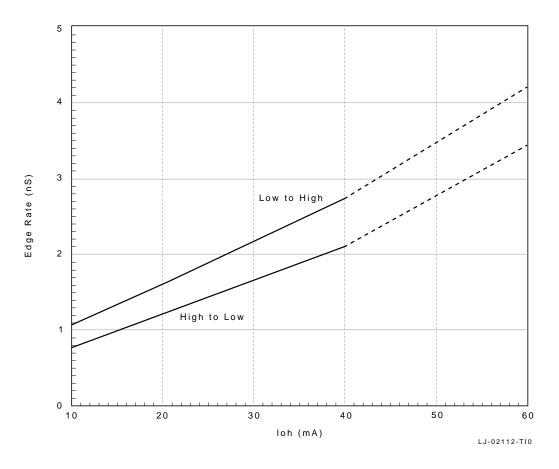

| 9.3.2.2 | Switching Characteristics                                 | 9–7  |

| 9.4     | Input Clock                                               | 9–9  |

| 9.4.1   | Clock Termination and Impedance Levels                    | 9–9  |

| 9.4.1.1 | AC Coupling                                               | 9–11 |

| 9.4.1.2 | DC Coupling                                               | 9–11 |

| 9.5     | Voltage/Current (VI) Characteristics Curves and Edge Rate |      |

|         | Curves                                                    | 9–12 |

| 9.5.1   | VI and Edge Rate Curves—Example One                       | 9–12 |

| 9.5.2   | VI and Edge Rate Curves—Example Two                       | 9–13 |

| 9.5.3   | VI and Edge Rate Curves—Example Three                     | 9–14 |

| 9.5.4   | Graphical Representation Methods                          | 9–16 |

| 9.6     | References                                                | 9–16 |

## **10** Mechanical Data and Packaging Information

| 10–1  |

|-------|

| 10–1  |

| 10–1  |

| 10–1  |

| 10–5  |

| 10–15 |

|       |

## A Designing a System with the 21064

| A.1     | Introduction                                     | A-1  |

|---------|--------------------------------------------------|------|

| A.2     | General Concepts                                 | A–2  |

| A.3     | Basic 21064 Power, Input Level, and Clock Issues | A–9  |

| A.3.1   | Power Supply and Input Levels                    | A–9  |

| A.3.2   | Input Level Sensing                              | A–10 |

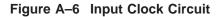

| A.3.3   | Input Clocks                                     | A–12 |

| A.3.4   | Unused Inputs                                    | A–13 |

| A.4     | Booting the 21064                                | A–14 |

| A.5     | Cache/Memory Interface Details                   | A–17 |

| A.5.1   | Bcache Timing for 21064 Access                   | A–18 |

| A.5.1.1 | Bcache Read Cycle                                | A–23 |

| A.5.1.2 | Bcache Write Cycle                               | A–27 |

| A.5.2   | Bcache Miss and External Request                 | A–31 |

| A.5.3   | Read Block Request                               | A–35 |

| A.5.4   | Write Block Request                              | A–42 |

| A.5.5   | Victim Write                                     | A–47 |

| A.5.6   | Non-Cached Memory Write                          | A–50 |

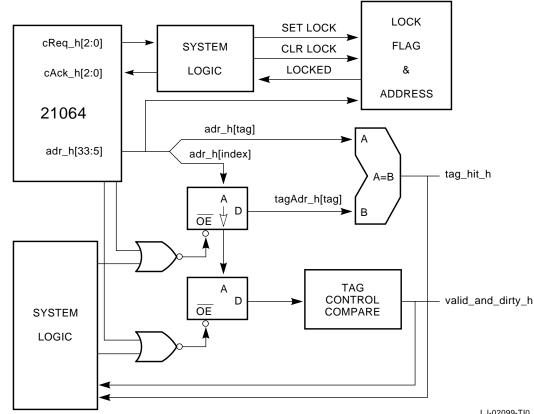

| A.6     | Load Locked and Store Conditional                | A–51 |

| A.7     | Special Request Cycles                           | A–53 |

| A.8     | DMA Access                                       | A–54 |

| A.9     | Backmapping the Internal 21064 Dcache            | A–55 |

| A.10    | I/O Interface                                    | A–56 |

|         |                                                  |      |

## **B** Technical Support and Ordering Information

| B.1 | Obtaining Technical Support               | B–1 |

|-----|-------------------------------------------|-----|

|     | Ordering Digital Semiconductor Products   | B–1 |

| B.3 | Ordering AlphaPC64 Boards                 | B–2 |

| B.4 | Ordering Digital Semiconductor Literature | B–2 |

## Glossary

#### Index

## Figures

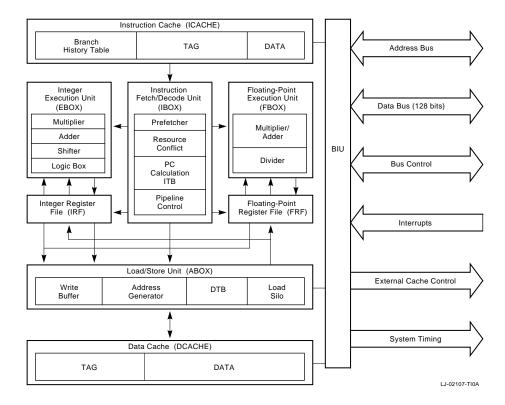

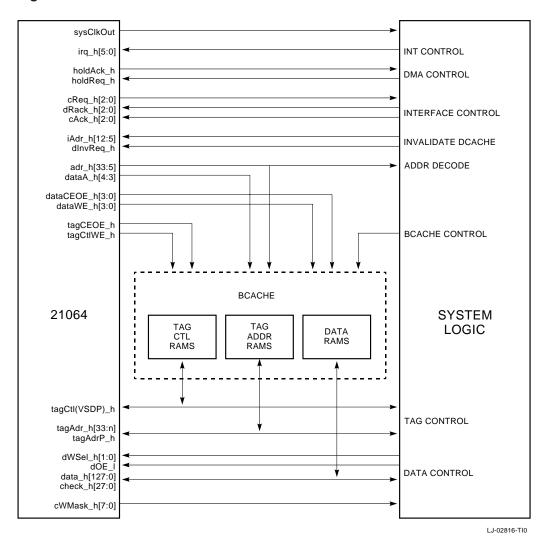

| 2–1  | Block Diagram of the 21064                               | 2–2  |

|------|----------------------------------------------------------|------|

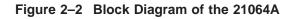

| 2–2  | Block Diagram of the 21064A                              | 2–3  |

| 2–3  | 21064 Floating-Point Control Register (FPCR) Format      | 2–16 |

| 2–4  | 21064A Floating-Point Control Register (FPCR) Format     | 2–17 |

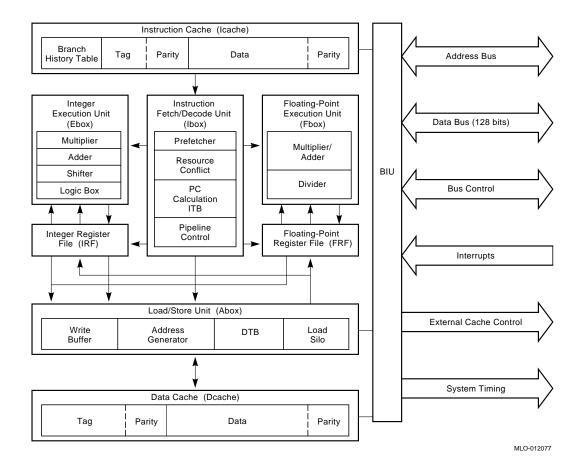

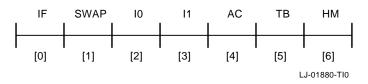

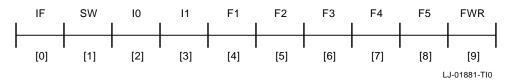

| 2–5  | Integer Operate Pipeline                                 | 2–24 |

| 2–6  | Memory Reference Pipeline                                | 2–24 |

| 2–7  | Floating-Point Operate Pipeline                          | 2–24 |

| 2–8  | Producer-Consumer Latency Matrix                         | 2–29 |

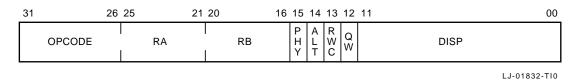

| 4–1  | HW_MFPR and HW_MTPR Instruction Format                   | 4–21 |

| 4–2  | HW_LD and HW_ST Instructions Format                      | 4–23 |

| 4–3  | HW_REI Instruction Format                                | 4–25 |

| 5–1  | Translation Buffer Tag Register                          | 5–2  |

| 5–2  | Instruction Translation Buffer Page Table Entry Register | 5–3  |

| 5–3  | ICCSR Register                                           | 5–4  |

| 5–4  | ITB_PTE_TEMP Register                                    | 5–9  |

| 5–5  | Exception Address Register                               | 5–10 |

| 5–6  | Clear Serial Line Interrupt Register                     | 5–10 |

| 5–7  | Serial Line Receive Register                             | 5–11 |

| 5–8  | Processor Status Register                                | 5–12 |

| 5–9  | Exception Summary Register                               | 5–13 |

| 5–10 | PAL_BASE Address Register                                | 5–14 |

| 5–11 | Hardware Interrupt Request Register                      | 5–15 |

| 5–12 | Software Interrupt Request Register                      | 5–16 |

| 5–13 | Asynchronous Trap Request Register                       | 5–17 |

| 5–14 | Hardware Interrupt Enable Register                       | 5–18 |

| 5–15 | Software Interrupt Enable Register                       | 5–19 |

| 5–16 | AST Interrupt Enable Register                            | 5–20 |

| 5–17 | Serial Line Transmit Register                            | 5–21 |

| 5–18 | Translation Buffer Control Register                      | 5–21 |

| 5–19 | Data Translation Buffer Page Table Entry Register        | 5–22 |

| 5–20 | Data Translation Buffer Page Table Entry Temporary       |      |

|      | Register                                                 | 5–22 |

| 5–21 | Memory Management Control and Status Register            | 5–23 |

| 5–22 | Abox Control Register                                    | 5–25 |

| 5–23 | Alternate Processor Mode Register                        | 5–28 |

| 5–24 | Cycle Counter Register                             | 5–29 |

|------|----------------------------------------------------|------|

| 5–25 | Cycle Counter Control Register                     | 5–29 |

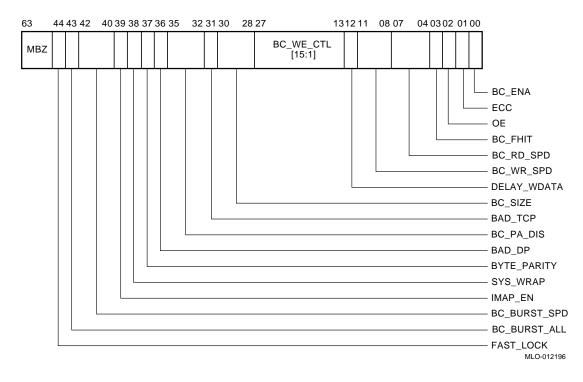

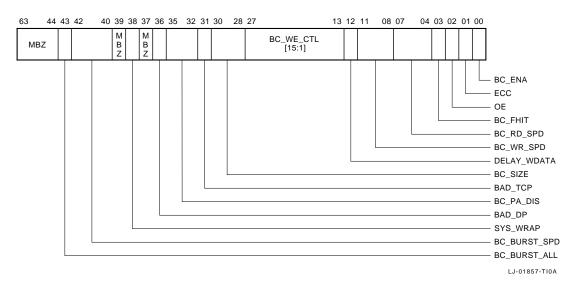

| 5–26 | 21064/21064A Bus Interface Unit Control Register   | 5–30 |

| 5–27 | Data Cache Status Register                         | 5–35 |

| 5–28 | Cache Status Register                              | 5–36 |

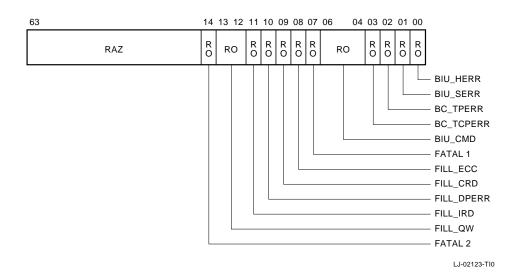

| 5–29 | Bus Interface Unit Status Register                 | 5–37 |

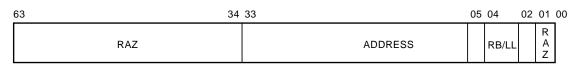

| 5–30 | Bus Interface Unit Address Register                | 5–40 |

| 5–31 | Fill Address Register                              | 5–40 |

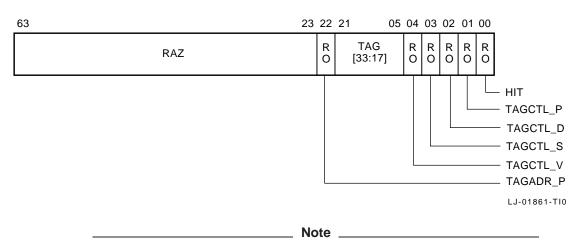

| 5–32 | FILL_SYNDROME Register                             | 5–41 |

| 5–33 | Backup Cache Tag Register                          | 5–43 |

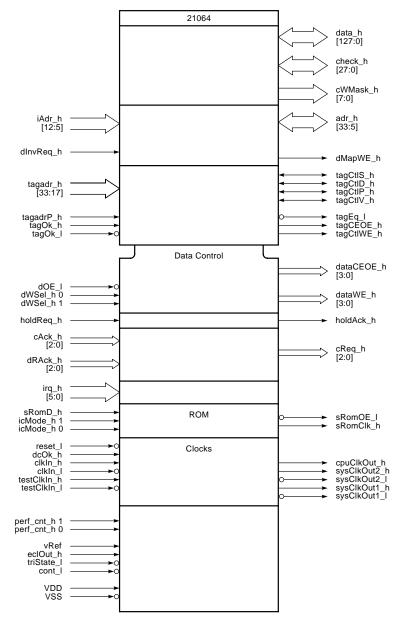

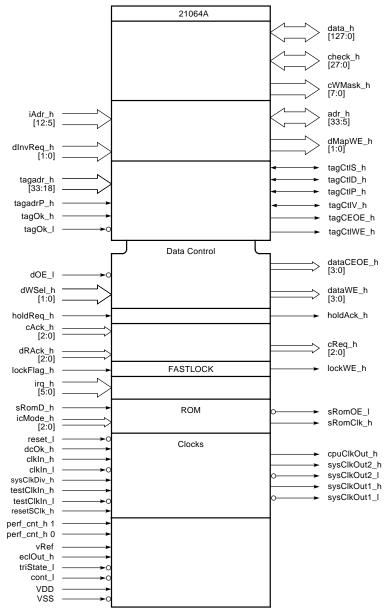

| 6–1  | 21064 Logic Symbol                                 | 6–2  |

| 6–2  | 21064A Logic Symbol                                | 6–3  |

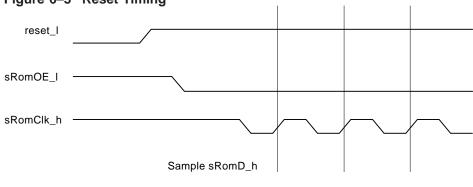

| 6–3  | Reset Timing                                       | 6–16 |

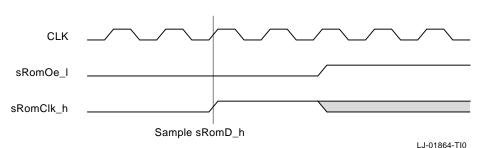

| 6–4  | Reset Timing — End of Preload Sequence             | 6–17 |

| 6–5  | Fast External Read Hit                             | 6–18 |

| 6–6  | Fast External Cache Write Hit                      | 6–19 |

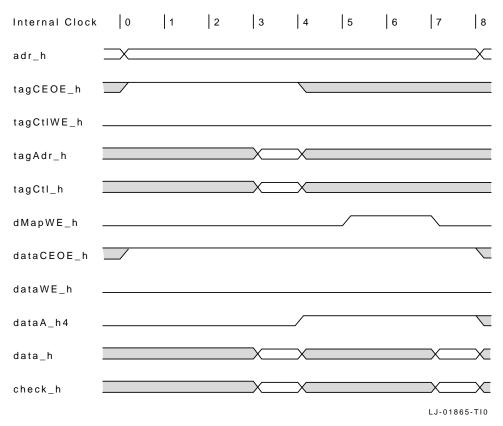

| 6–7  | External Cache Write Timing                        | 6–20 |

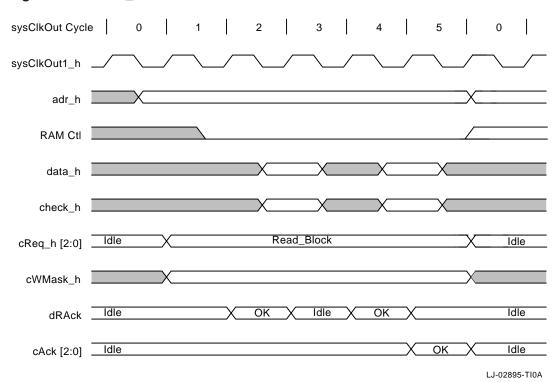

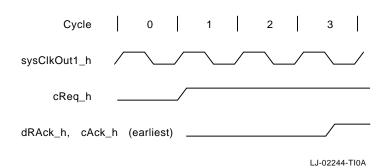

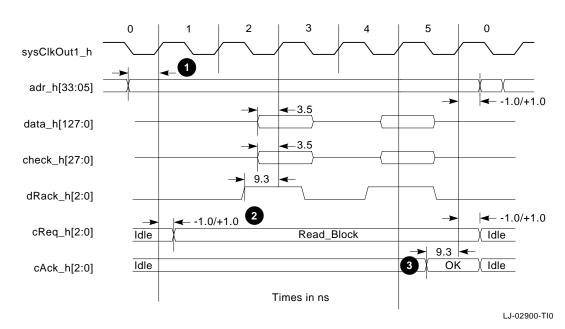

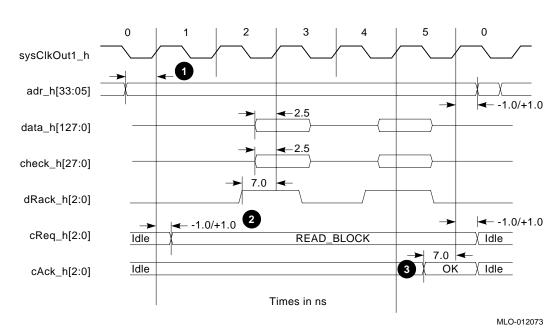

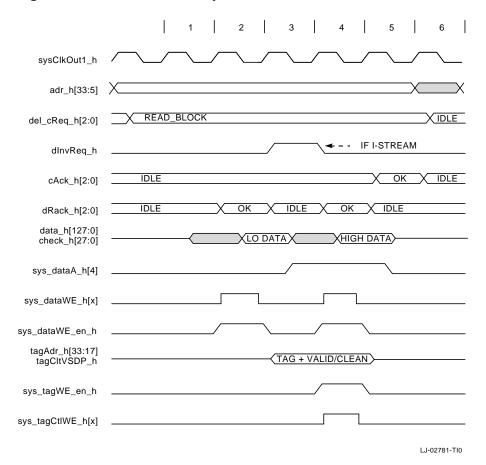

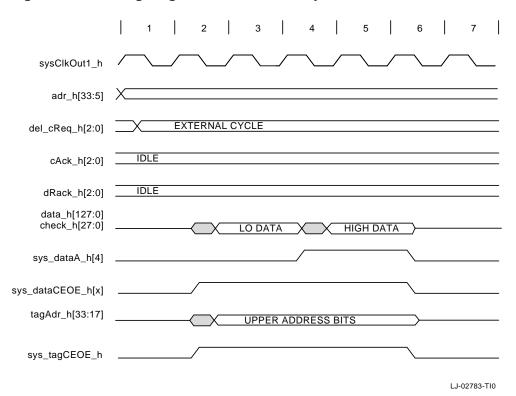

| 6–8  | READ_BLOCK Transaction                             | 6–21 |

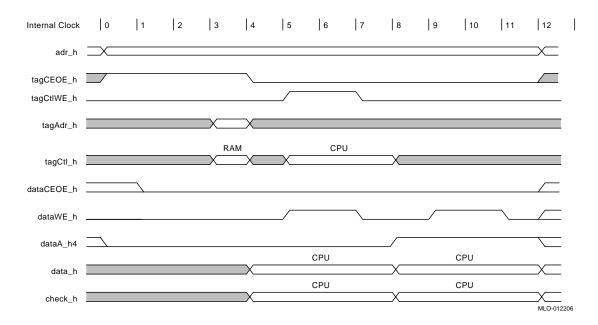

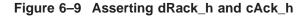

| 6–9  | Asserting dRack_h and cAck_h                       | 6–23 |

| 6–10 | READ_BLOCK Transaction — Minimum Cycle Time        | 6–24 |

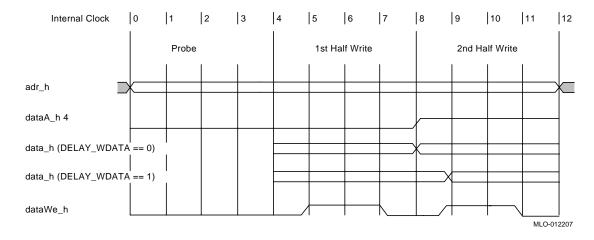

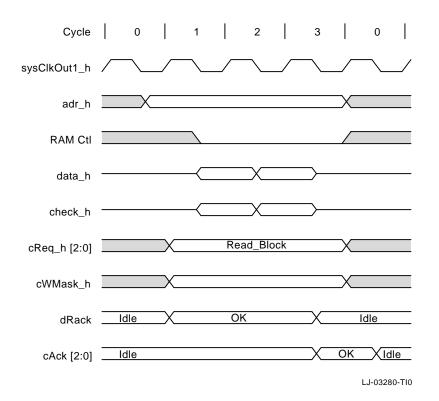

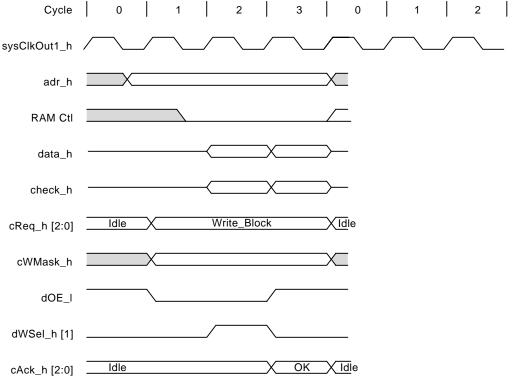

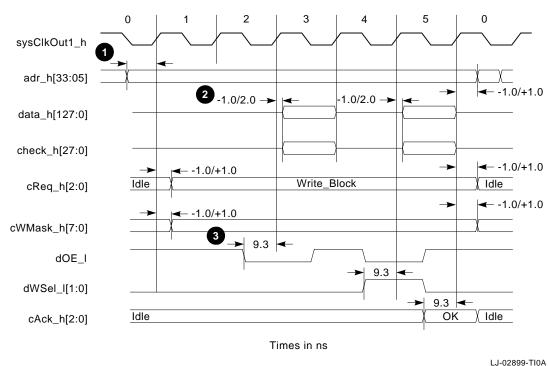

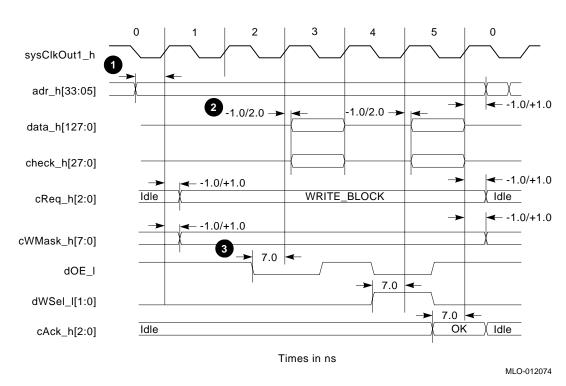

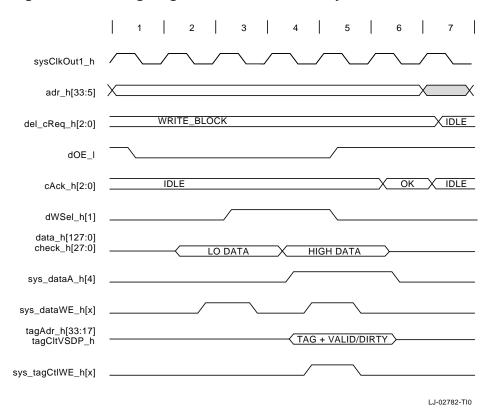

| 6–11 | WRITE_BLOCK Transaction Timing                     | 6–25 |

| 6–12 | WRITE_BLOCK Transaction—Minimum Cycle Time         | 6–27 |

| 6–13 | WRITE_BLOCK Transaction Timing Without an External |      |

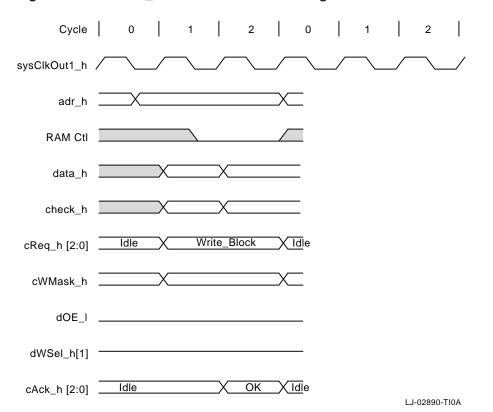

|      | Cache                                              | 6–28 |

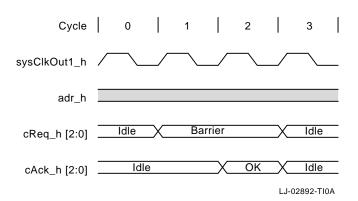

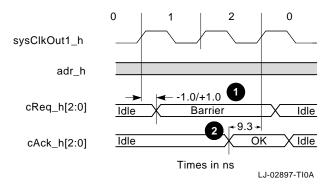

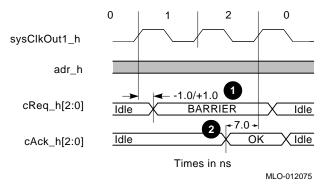

| 6–14 | BARRIER Transaction                                | 6–32 |

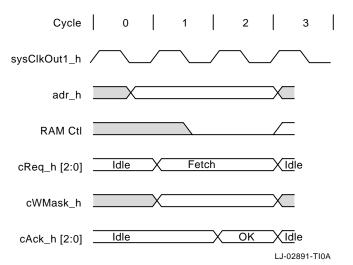

| 6–15 | FETCH Transaction                                  | 6–33 |

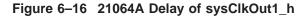

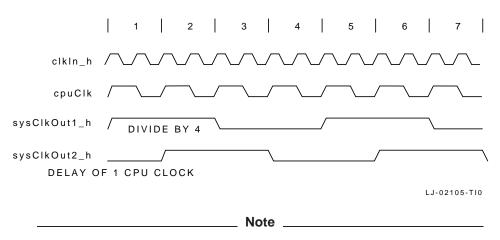

| 6–16 | 21064A Delay of <b>sysClkOut1_h</b>                | 6–36 |

| 6–17 | Icache Load Order                                  | 6–58 |

| 6–18 | ECC Code                                           | 6–61 |

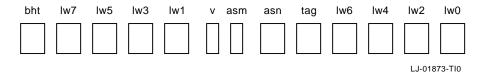

| 7–1  | Clock Termination                                  | 7–8  |

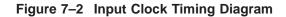

| 7–2  | Input Clock Timing Diagram                         | 7–9  |

| 7–3  | Flow-Through Delay (External Cache)                | 7–11 |

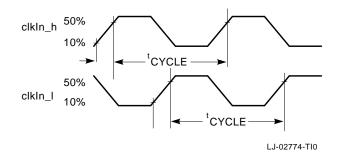

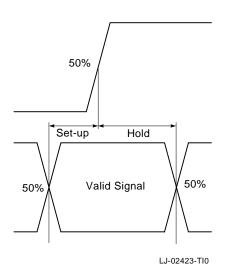

| 7–4  | Output Delay Measurement                           | 7–14 |

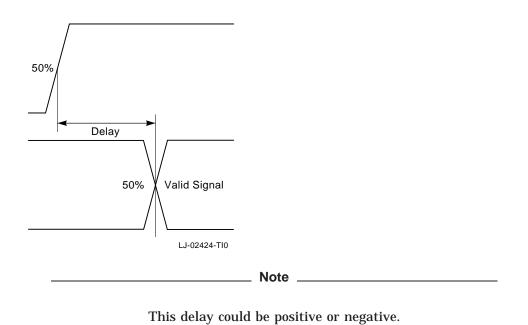

| 7–5  | Setup and Hold Time Measurement                    | 7–15 |

| 7–6  | 21064 READ_BLOCK Timing Diagram                    | 7–16 |

| 7–7  | 21064A READ_BLOCK Timing Diagram                   | 7–17 |

| 7–8  | 21064 WRITE_BLOCK Timing Diagram                   | 7–18 |

| 7–9  | 21064A WRITE_BLOCK Timing Diagram                  | 7–19 |

|------|----------------------------------------------------|------|

| 7–10 | 21064 BARRIER Timing Diagram                       | 7–20 |

| 7–11 | 21064A BARRIER Timing Diagram                      | 7–20 |

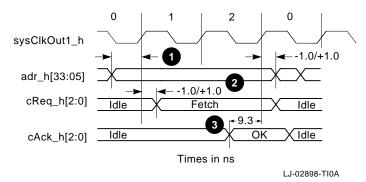

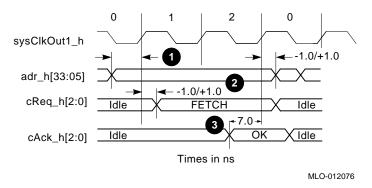

| 7–12 | 21064 FETCH/FETCH_M Timing Diagram                 | 7–21 |

| 7–13 | 21064A FETCH/FETCH_M Timing Diagram                | 7–21 |

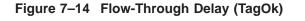

| 7–14 | Flow-Through Delay (TagOk)                         | 7–23 |

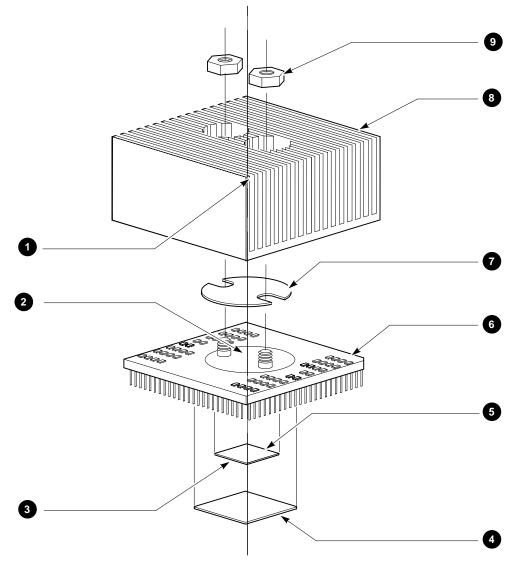

| 8–1  | Package Components and Temperature Measurement     |      |

|      | Locations                                          | 8–5  |

| 8–2  | Heat Sinks Dimensions                              | 8–7  |

| 8–3  | Comparison of Dimensions for Heat Sink Designs     | 8–13 |

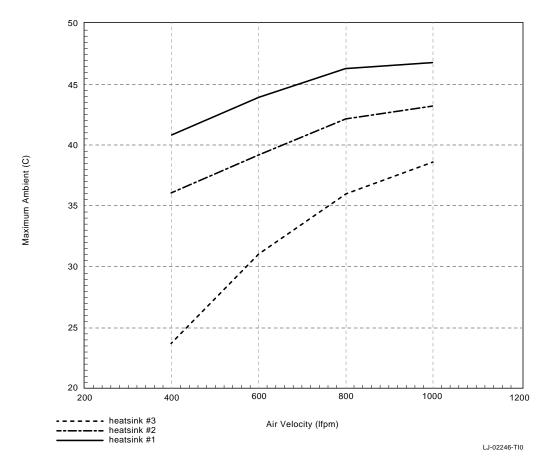

| 8–4  | Microprocessor Thermal Performance                 | 8–14 |

| 8–5  | Heat Sink Maximum Ambient Temperature              | 8–15 |

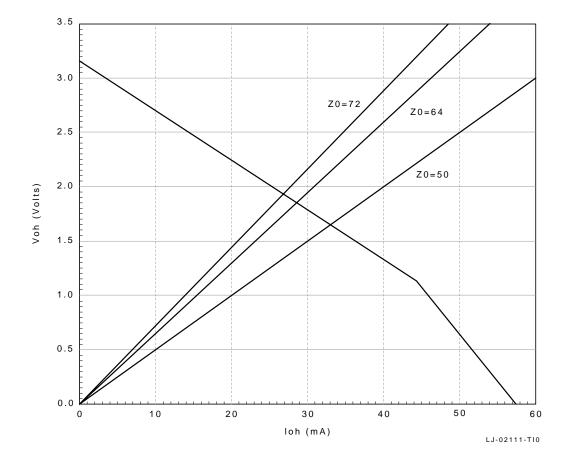

| 9–1  | High Level Output Voltage versus High Level Output |      |

|      | Current                                            | 9–6  |

| 9–2  | Low Level Output Voltage versus Low Level Output   |      |

|      | Current                                            | 9–7  |

| 9–3  | Edge Rate versus Load                              | 9–8  |

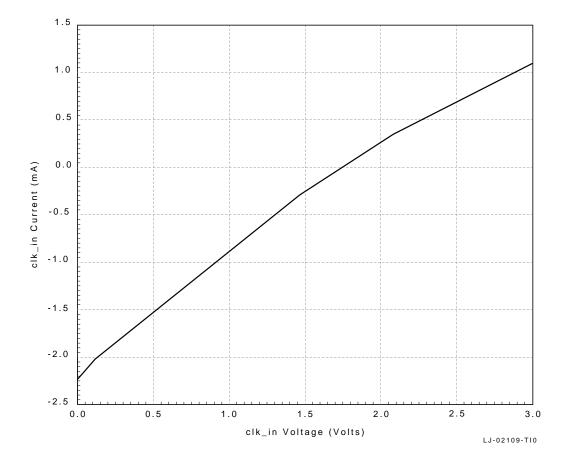

| 9–4  | Clock Current versus Clock Voltage                 | 9–10 |

| 9–5  | Low to High Load Line Analysis                     | 9–15 |

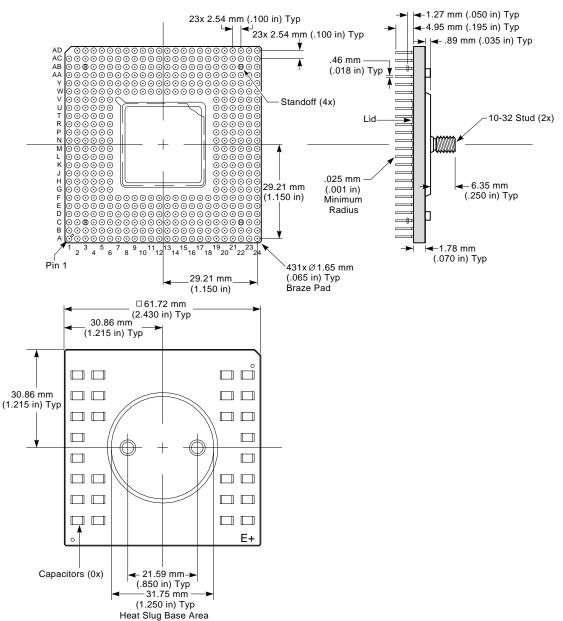

| 10–1 | 21064 Package Dimensions                           | 10–2 |

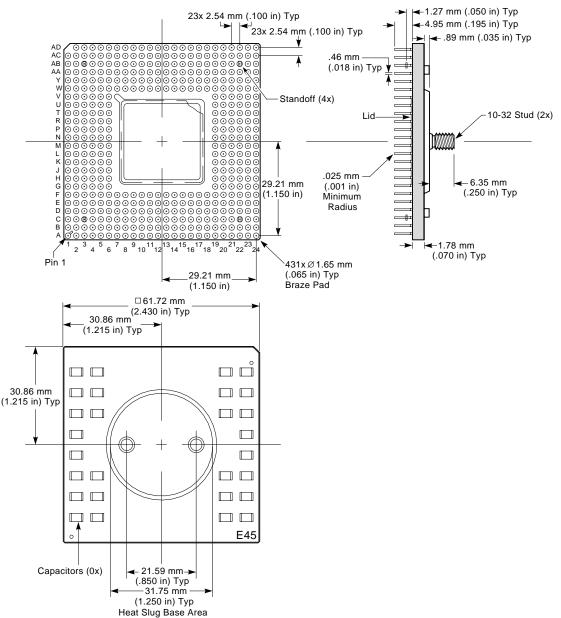

| 10–2 | 21064A Package Dimensions                          | 10–3 |

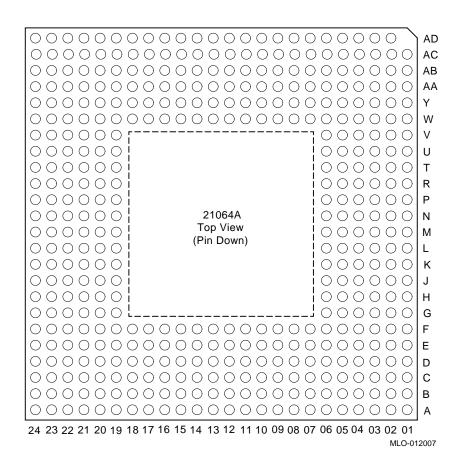

| 10–3 | 21064A PGA Cavity Down View                        | 10–4 |

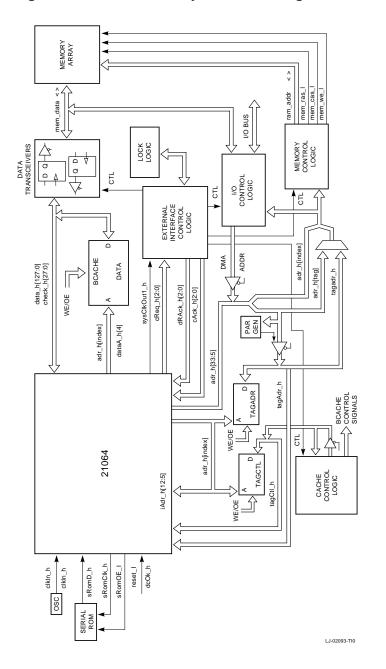

| A–1  | 21064 External Interface                           | A–3  |

| A–2  | 21064-Based System Block Diagram                   | A–5  |

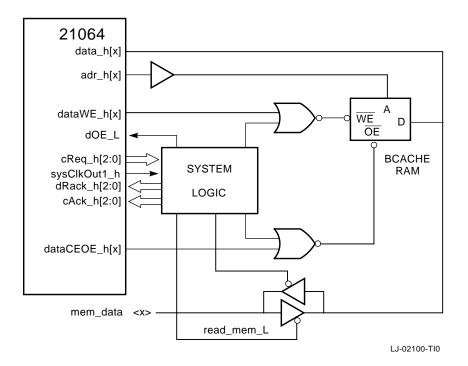

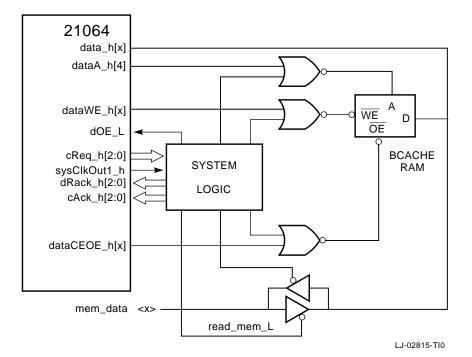

| A–3  | Bcache Control Logic                               | A-7  |

| A–4  | Lower Bcache Address                               | A–8  |

| A–5  | Input Reference Voltage Circuit                    | A–11 |

| A–6  | Input Clock Circuit                                | A–12 |

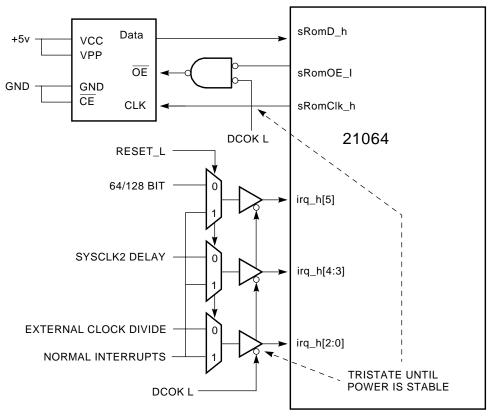

| A–7  | Serial ROM and Programmable Clock Inputs           | A–14 |

| A–8  | Example of 21064 Clock Configuration               | A–16 |

| A–9  | 21064 BIU_CTL Internal Processor Register          | A–18 |

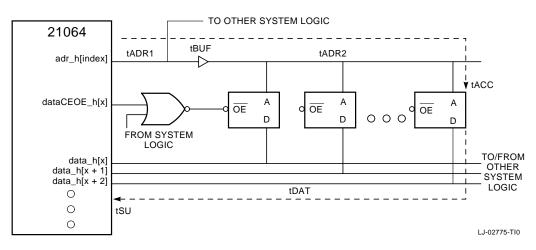

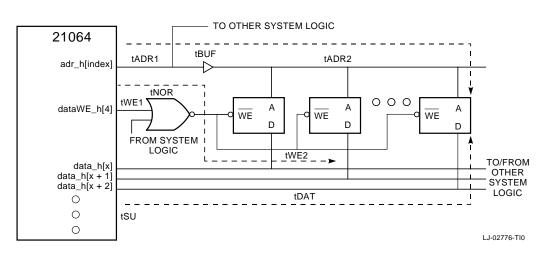

| A–10 | Bcache Access Path for 21064                       | A–24 |

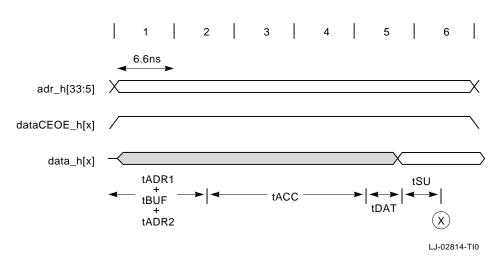

| A–11 | Timing Diagram for Bcache Read Access              | A–25 |

| A–12 | Cache Write Path for 21064                         | A–27 |

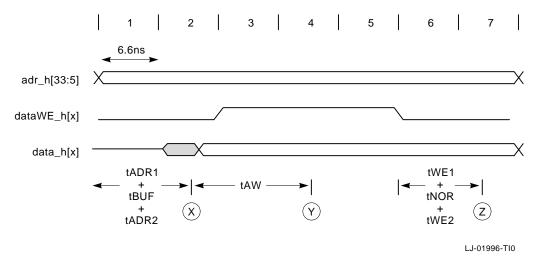

| A–13 | Timing Diagram for Bcache Write Access             | A–28 |

| A–14 | External Cycle                                     | A–33 |

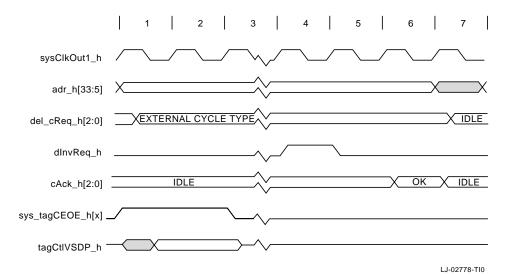

| A–15 | Tag Control Probe Before External Cycle            | A–34 |

|      |                                                    |      |

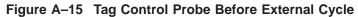

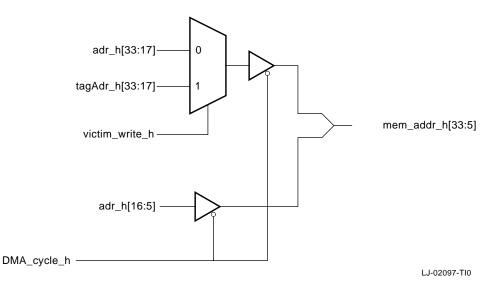

| A–16 | Tag Access and Write Circuit                | A–36 |

|------|---------------------------------------------|------|

| A–17 | Timing Diagram of READ_BLOCK Cycle          | A–37 |

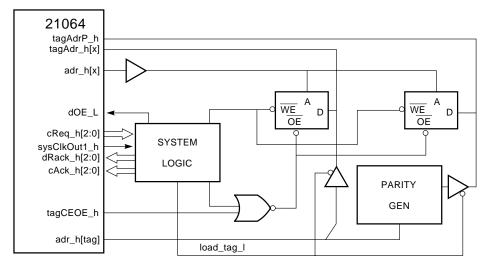

| A–18 | Clock Skew from System to 21064             | A–39 |

| A–19 | READ_BLOCK Cycle with Write Pulse           | A–41 |

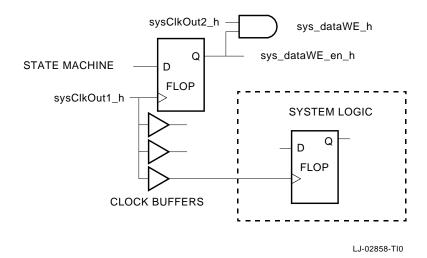

| A–20 | Write Pulse Circuit                         | A–42 |

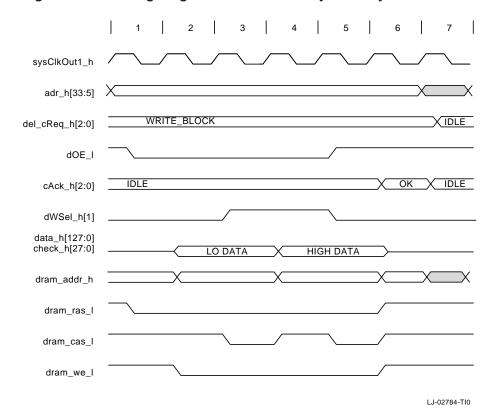

| A–21 | Timing Diagram of WRITE_BLOCK Cycle         | A-44 |

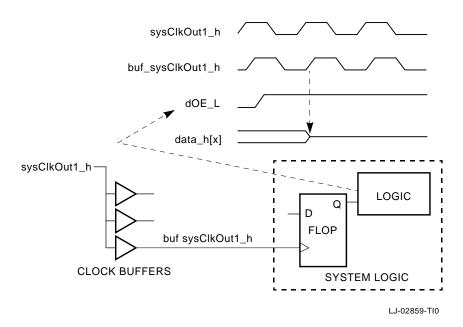

| A–22 | Clock Skew from System to 21064 for Write   | A–46 |

| A–23 | Timing Diagram of Victim Write Cycle        | A–48 |

| A–24 | Address MUX for Victim Write                | A–49 |

| A–25 | Timing Diagram of Direct Memory Write Cycle | A–50 |

| A–26 | Tag Address Compare Circuit                 | A–52 |

## Tables

| 1   | Register Field Type Notation                          | xxiii |

|-----|-------------------------------------------------------|-------|

| 2   | Register Field Notation                               | xxiv  |

| 2–1 | Architected JSR Hint Bits                             | 2–6   |

| 2–2 | Floating-Point Control Register Bit Descriptions      | 2–18  |

| 2–3 | Producer-Consumer Classes                             | 2–27  |

| 2–4 | Opcode Summary with Instruction Issue Bus             | 2–32  |

| 2–5 | Reserved PALcode Instructions (21064/21064A Specific) | 2–34  |

| 3–1 | Instruction Format and Opcode Notation                | 3–1   |

| 3–2 | Architecture Instructions                             | 3–2   |

| 3–3 | IEEE Floating-Point Instruction Function Codes        | 3–7   |

| 3–4 | VAX Floating-Point Instruction Function Codes         | 3–9   |

| 3–5 | Required PALcode Function Codes                       | 3–10  |

| 3–6 | Opcodes Specific to the 21064/21064A                  | 3–10  |

| 3–7 | Opcodes Reserved for Digital                          | 3–10  |

| 4–1 | PALcode Entry Points                                  | 4–7   |

| 4–2 | D-stream Error PALcode Entry Points                   | 4–8   |

| 4–3 | HW_MTPR Restrictions                                  | 4–12  |

| 4–4 | HW_MTPR Cycle Delay                                   | 4–15  |

| 4–5 | Instructions Specific to the 21064/21064A             | 4–20  |

| 4–6 | HW_MFPR and HW_MTPR Format Description                | 4–21  |

| 4–7 | Internal Processor Register Access                    | 4–22  |

| 4–8 | HW_LD and HW_ST Format Description                    | 4–24  |

| 4–9 | The HW_REI Format Description                         | 4–25  |

|     |                                                       |       |

| 4–10 | Required PALcode Instructions                         | 4–25 |

|------|-------------------------------------------------------|------|

| 5–1  | ICCSR Fields and Description                          | 5–4  |

| 5–2  | BHE, BPE Branch Prediction Selection (Conditional     |      |

|      | Branches Only)                                        | 5–6  |

| 5–3  | Performance Counter 0 Input Selection (in ICCSR)      | 5–7  |

| 5–4  | Performance Counter 1 Input Selection (in ICCSR)      | 5–8  |

| 5–5  | Clear Serial Line Interrupt Register Fields           | 5–11 |

| 5–6  | Exception Summary Register Fields                     | 5–13 |

| 5–7  | Hardware Interrupt Request Register Fields            | 5–15 |

| 5–8  | Hardware Interrupt Enable Register Fields             | 5–18 |

| 5–9  | Memory Management Control and Status Register         | 5–23 |

| 5–10 | Abox Control Register Fields                          | 5–25 |

| 5–11 | Alternate Processor Mode Register                     | 5–28 |

| 5–12 | Bus Interface Unit Control Register Fields            | 5–30 |

| 5–13 | BC_SIZE                                               | 5–34 |

| 5–14 | BC_PA_DIS                                             | 5–34 |

| 5–15 | Dcache Status Register Fields                         | 5–35 |

| 5–16 | Cache Status Register Fields                          | 5–36 |

| 5–17 | Bus Interface Unit Status Register Fields             | 5–38 |

| 5–18 | Syndromes for Single-Bit Errors                       | 5–42 |

| 5–19 | Backup Cache Tag Register Fields                      | 5–44 |

| 5–20 | Internal Process Register Reset State                 | 5–45 |

| 6–1  | Data, Address, and Parity/ECC Buses                   | 6–4  |

| 6–2  | Primary Cache Invalidate                              | 6–4  |

| 6–3  | External Cache Control                                | 6–5  |

| 6–4  | External Cycle Control                                | 6–7  |

| 6–5  | Interrupts                                            | 6–9  |

| 6–6  | Instruction Cache Initialization/Serial ROM Interface | 6–11 |

| 6–7  | Initialization                                        | 6–12 |

| 6–8  | Fast Lock Mode Signals ( <b>21064A only</b> )         | 6–12 |

| 6–9  | Performance Monitoring                                | 6–12 |

| 6–10 | Clocks                                                | 6–13 |

| 6–11 | Other Signals                                         | 6–14 |

| 6–12 | State of Pins at Reset                                | 6–15 |

| 6–13 | Tag Control Encodings                                 | 6–43 |

| 6–14 | Cycle Types                                           | 6–48 |

| 6–15 | FETCH/FETCH_M Cycle Write Mask Addresses              | 6–49 |

|      |                                                       |      |

| 6–16 | Acknowledgment Types                                           | 6–50  |

|------|----------------------------------------------------------------|-------|

| 6–17 | Read Data Acknowledgment Types                                 | 6–51  |

| 6–18 | dWSel_h Byte Selection                                         | 6–55  |

| 6–19 | 21064 Icache Test Modes                                        | 6–56  |

| 6–20 | 21064A Icache Test Modes                                       | 6–57  |

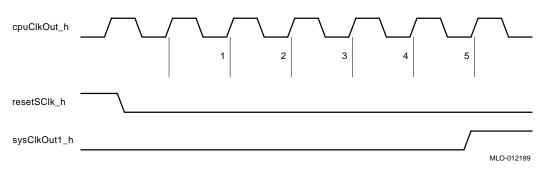

| 6–21 | Icache Field Size                                              | 6–58  |

| 6–22 | 21064A Data Protection Mode Selection                          | 6–60  |

| 6–23 | LW Parity Check Bits                                           | 6–62  |

| 6–24 | <b>21064A</b> Byte Parity <b>check_h</b> Bits                  | 6–62  |

| 7–1  | 21064/21064A Maximum Ratings                                   | 7–1   |

| 7–2  | DC Input/Output Characteristics                                | 7–4   |

| 7–3  | testClkIn Pins State                                           | 7–7   |

| 7–4  | 21064 Input Clock Timing                                       | 7–8   |

| 7–5  | 21064A Input Clock Timing                                      | 7–8   |

| 7–6  | External Cycles                                                | 7–12  |

| 7–7  | tagEq_l Timing                                                 | 7–22  |

| 7–8  | Asynchronous Signals During Test                               | 7–24  |

| 8–1  | 21064-150 Thermal Characteristics in a Forced-Air              |       |

|      | Environment                                                    | 8–8   |

| 8–2  | 21064-166 Thermal Characteristics in a Forced-Air              |       |

|      | Environment                                                    | 8–9   |

| 8–3  | 21064-200 Thermal Characteristics in a Forced-Air              |       |

| 0.4  | Environment                                                    | 8–9   |

| 8–4  | 21064A-200 Thermal Characteristics in a Forced-Air Environment | 8–10  |

| 8–5  | 21064A-233 Thermal Characteristics in a Forced-Air             | 0-10  |

| 0-0  | Environment                                                    | 8–10  |

| 8–6  | 21064A-275 and <b>21064A-275-PC</b> Thermal Characteristics in | 0 10  |

| 0 0  | a Forced-Air Environment                                       | 8–11  |

| 8–7  | 21064A-300 Thermal Characteristics in a Forced-Air             |       |

|      | Environment                                                    | 8–11  |

| 10–1 | 21064 and 21064A Pin List Differences                          | 10–5  |

| 10–2 | Data Pin List (Type B)                                         | 10–6  |

| 10–3 | Address Pin List (Type B)                                      | 10–7  |

| 10–4 | Parity/ECC Bus Pin List (Type B)                               | 10–8  |

| 10–5 | Primary Cache Invalidate Pin List (Type I)                     | 10–8  |

| 10–6 | External Cache Control Pin List                                | 10–9  |

| 10–7 | Interrupts Pin List (Type I)                                   | 10–11 |

| 10–8  | Instruction Cache Initialization Pin List (Type I)    | 10–11 |

|-------|-------------------------------------------------------|-------|

| 10–9  | Serial ROM Interface Pin List                         | 10–11 |

| 10–10 | Initialization Pin List (Type I)                      | 10–11 |

| 10–11 | 21064 Clock Pin List                                  | 10–12 |

| 10–12 | 21064A Load/Lock and Store/Conditional Fast Lock Mode | 10–12 |

| 10–13 | Performance Monitoring Pin List                       | 10–12 |

| 10–14 | Other Signals Pin List                                | 10–12 |

| 10–15 | Power Pin List (Type P)                               | 10–13 |

| 10–16 | Ground Pin List                                       | 10–14 |

| 10–17 | Spare Pin List (Type N)                               | 10–15 |

| 10–18 | 21064/21064A PGA Pin List                             | 10–16 |

| A–1   | System Clock Divisor                                  | A–15  |

| A–2   | System Clock Delay                                    | A–16  |

| A–3   | Bus Interface Unit Control Register Fields            | A–19  |

| A–4   | BC_SIZE                                               | A–22  |

| A–5   | BC_PA_DIS                                             | A–22  |

## Preface

#### **Audience**

This reference manual is for system designers who use the Alpha 21064 or Alpha 21064A microprocessors.

#### Manual Organization

The information in this manual is organized into ten chapters and two appendixes.

The internal chip architecture, Alpha architecture instruction set, privileged architecture code (PALcode) and internal registers are described before the external interface. The final chapters of the manual contain electrical, thermal, signal integrity, and mechanical information.

Appendix A contains information for designing systems using the Alpha 21064. Appendix B contains information about technical support and ordering related documentation. A glossary comes next followed by an index and ordering information.

Alpha architecture information is contained in the companion volume to this manual, the *Alpha Architecture Handbook*.

#### **Terminology and Conventions**

The following sections describe the terminology and conventions used in this manual.

#### **Microprocessor Terms**

The term 21064/21064A will be used where information applies to both the Alpha 21064 and the Alpha 21064A microprocessors. The term **21064** or **21064A** will be used where information applies to only one of these microprocessors. The term **21064A-275-PC** will be used where information applies only to that one microprocessor.

#### Numbering

All numbers are decimal unless otherwise indicated. Where there is ambiguity, numbers other than decimal are indicated with the name of the base following the number in parentheses, for example FF (hex).

#### **Security Holes**

Security holes exist when unprivileged software (that is, software running outside of kernel mode) can:

- Affect the operation of another process without authorization from the operating system

- Amplify its privilege without authorization from the operating system

- Communicate with another process, either overtly or covertly, without authorization from the operating system

#### UNPREDICTABLE and UNDEFINED

Throughout this manual, the terms UNPREDICTABLE and UNDEFINED are used. Their meanings are quite different and must be carefully distinguished.

In particular, only privileged software (that is, software running in kernel mode) can trigger UNDEFINED operations. Unprivileged software cannot trigger UNDEFINED operations. However, either privileged or unprivileged software can trigger UNPREDICTABLE results or occurrences.

UNPREDICTABLE results or occurrences do not disrupt the basic operation of the processor; it continues to execute instructions in its normal manner. In contrast, an UNDEFINED operation can halt the processor or cause it to lose information.

The terms UNPREDICTABLE and UNDEFINED can be further described as follows:

#### UNPREDICTABLE

- Results or occurrences specified as UNPREDICTABLE may vary from moment to moment, implementation to implementation, and instruction to instruction within implementations. Software can never depend on results specified as UNPREDICTABLE.

- An UNPREDICTABLE result may acquire an arbitrary value subject to a few constraints. Such a result may be an arbitrary function of the input operands or of any state information that is accessible to the process in its current access mode. UNPREDICTABLE results may be unchanged from their previous values.

Operations that produce UNPREDICTABLE results may also produce exceptions.

• An occurrence specified as UNPREDICTABLE may happen or not based on an arbitrary choice function. The choice function is subject to the same constraints as are UNPREDICTABLE results and, in particular, must not constitute a security hole.

Specifically, UNPREDICTABLE results must not depend upon, or be a function of the contents of memory locations or registers which are inaccessible to the current process in the current access mode.

Also, operations that may produce UNPREDICTABLE results must not:

- Write or modify the contents of memory locations or registers to which the current process in the current access mode does not have access.

- Halt or hang the system or any of its components.

For example, a security hole would exist if some UNPREDICTABLE result depended on the value of a register in another process, on the contents of processor temporary registers left behind by some previously running process, or on a sequence of actions of different processes.

#### UNDEFINED

- Operations specified as UNDEFINED may vary from moment to moment, implementation to implementation, and instruction to instruction within implementations. The operation may vary in effect from nothing, to stopping system operation.

- UNDEFINED operations may halt the processor or cause it to lose information. However, UNDEFINED operations must not cause the processor to hang, that is, reach an unhalted state from which there is no transition to a normal state in which the machine executes instructions.

#### **Ranges and Extents**

Ranges are specified by a pair of numbers separated by a ".." and are inclusive. For example, a range of integers 0..4 includes the integers 0, 1, 2, 3, and 4.

Extents are specified by a pair of numbers in brackets separated by a colon and are inclusive. For example, bits [7:3] specify an extent of bits including bits 7, 6, 5, 4, and 3.

#### ALIGNED and UNALIGNED

In this manual the terms ALIGNED and NATURALLY ALIGNED are used interchangeably to refer to data objects that are powers of two in size. An aligned datum of size 2\*\*N is stored in memory at a byte address that is a multiple of 2\*\*N, that is, one that has N low-order zeros. Thus, an aligned 64-byte stack frame has a memory address that is a multiple of 64.

If a datum of size  $2^{**}N$  is stored at a byte address that is not a multiple of  $2^{**}N$ , it is called UNALIGNED.

#### Must Be Zero (MBZ)

Fields specified as Must Be Zero (MBZ) must never be filled by software with a non-zero value. If the processor encounters a non-zero value in a field specified as MBZ, a Reserved Operand exception occurs.

#### Should Be Zero (SBZ)

Fields specified as Should Be Zero (SBZ) should be filled by software with a zero value. Non-zero values in SBZ fields produce UNPREDICTABLE results and may produce extraneous instruction-issue delays.

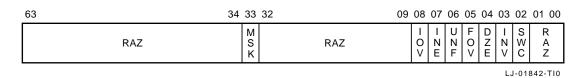

#### Read As Zero (RAZ)

Fields specified as Read As Zero (RAZ) return a zero when read.

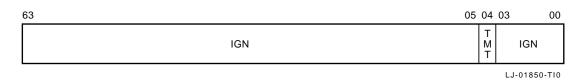

#### Ignore (IGN)

Fields specified as Ignore (IGN) are ignored when written.

#### **Register Format Notation**

This manual contains a number of figures that show the format of various registers. Some registers are followed by a description of each field. The fields on the register are labeled with either a name or a mnemonic. The description of each field includes the name or mnemonic, the bit extent, and the type.

The "Type" column in the field description includes both the actual type of the field, and an optional initialized value, separated from the type by a comma. The type denotes the functional operation of the field, and may be one of the values shown in Table 1. If present, the initialized value indicates that the field is initialized by hardware to the specified value at powerup. If the initialized value is not present, the field is not initialized at powerup.

| Notation | Description                                                                                                                                                                                                                                                                                                                           |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RW       | A read-write bit or field. The value may be read and written by software.                                                                                                                                                                                                                                                             |  |  |

| RO       | A read-only bit or field. The value may be read by software. It is written by hardware; software writes are ignored.                                                                                                                                                                                                                  |  |  |

| WO       | A write-only bit or field. The value may be written by soft-<br>ware. It is used by hardware and reads by software return an<br>UNPREDICTABLE result.                                                                                                                                                                                 |  |  |

| WZ       | A write bit or field. The value may be written by software. It is used by hardware and reads by software return a 0.                                                                                                                                                                                                                  |  |  |

| W1C      | A write-one-to-clear bit. If reads are allowed to the register then th value may be read by software. If it is a write-only register then a read by software returns an UNPREDICTABLE result. Software writes of a 1 cause the bit to be cleared by hardware. Software writes of a 0 do not modify the state of the bit.              |  |  |

| W0C      | A write-zero-to-clear bit. If reads are allowed to the register then<br>the value may be read by software. If it is a write-only register the<br>a read by software returns an UNPREDICTABLE result. Software<br>writes of a 0 cause the bit to be cleared by hardware. Software<br>writes of a 1 do not modify the state of the bit. |  |  |

| WA       | A write-anything-to-the-register-to-clear bit. If reads are allowed to<br>the register then the value may be read by software. If it is a write<br>only register then a read by software returns an UNPREDICTABL<br>result. Software write of any value to the register cause the bit to<br>be cleared by hardware.                   |  |  |

| RC       | A read-to-clear field. The value is written by hardware and remains<br>unchanged until read. The value may be read by software, at which<br>point, hardware may write a new value into the field.                                                                                                                                     |  |  |

Table 1 Register Field Type Notation

In addition to named fields in registers, other bits of the register may be labeled with one of the three symbols listed in Table 2. These symbols denote the type of the unnamed fields in the register.

Table 2 Register Field Notation

| Notation | Description                                                                                                |

|----------|------------------------------------------------------------------------------------------------------------|

| RAZ      | Denotes a register bit(s) that is read as a zero.                                                          |

| IGN      | Denotes a register bit(s) that is ignored on write and UNPREDICTABLE when read if not otherwise specified. |

| MBZ      | Denotes a register bit(s) that must be a zero value.                                                       |

#### Alpha 21064 and Alpha 21064A Differences Sections

The Alpha 21064 and Alpha 21064A are alike in most ways but they have some differences. Throughout this manual the bold labels **21064** and **21064A** are used to indicate that the feature or operation only applies to one of the microprocessors.

The sections, figures, and tables where these differences occur are listed here:

- Parity and ECC features in Section 1.3

- Backward compatibility of the **21064A** in Section 1.4

- **21064** Block Diagram in Figure 2–1 and **21064A** Block Diagram in Figure 2–2

- Branch prediction in Section 2.3.1.1 and Section 2.3.1.2

- Internal cache hit signals in Section 2.3.4

- Resetting the write buffer counter in Section 2.5.4

- Fbox inexact flag in Section 2.6

- Inexact disable bit added to FPCR. See Figure 2-3 and Figure 2-4

- Inexact (INE) part of IEEE floating-point conformance in Section 2.7

- Primary cache differences in Section 2.8

- FDIV F/S and FDIV G/T in Section 2.10.2

- ABOX\_CTL Register [15:12] in Figure 5–22 and Table 5–10

- BIU\_CTL Register [44,39,37,7:4] in Figure 5–26 and Table 5–12

- Cache status registers in Section 5.3.16 and Section 5.3.17

- Microprocessors logic symbols in Figure 6–1 and Figure 6–2

- **dInvReq\_h** in Table 6–2

- tagAdr\_h, tagEq\_l and dMapWE\_h in Table 6-3

- irq\_h and sysClkDiv\_h in Table 6–5

- **icMode\_h** in Table 6–6

- resetSClk\_h in Table 6–7

- Fast lock mode signals in Table 6–8

- Reset signal states in Section 6.4.1

- LDL\_L/LDQ\_L and STL\_C/STQ\_C transactions in Section 6.4.10

- System clock divisor and assertion delay in Section 6.5.1

- Primary cache invalidates in Section 6.5.3

- Fast lock mode effect on LDL\_L/LDQ\_L in Section 6.5.4

- Tristate driver note in Section 6.5.4.4

- tagOK synchronization in Section 6.5.4.5

- Check bits during reads in Section 6.5.5.2

- 21064A data protection mode selection in Section 6.5.9.3

- 21064A byte parity data protection in Table 6–24

- 20164A cache parity errors in Section 6.6.5

- Maximum electrical ratings in Table 7–1

- Reference voltage for **tagOK\_h** and **tagOK\_l** in Section 7.2.1 and Section 7.4.1.

- Input clock timing in Table 7–4 and Table 7–5

- Subtable with input setup relative to sysClkOut1\_h in Section 7.4.5

- READ\_BLOCK Timing in Figure 7–6 and Figure 7–7

- WRITE\_BLOCK Timing in Figure 7–8 and Figure 7–9

- BARRIER Timing in Figure 7–10 and Figure 7–11

- FETCH/FETCH\_M Timing in Figure 7–12 and Figure 7–13

- tagEq\_l in Section 7.4.6

- tagOK\_h and tagOK\_l synchronization in Section 7.4.7 and Section 7.4.8

- Power considerations in Section 8.2.2

- Thermal characteristics and parameters with heat sink in a forced-air environment in Tables 8–1 through 8–3 and Tables 8–4 through 8–7

- Pin List differences in Table 10–1

# Introduction to the 21064/21064A

#### **1.1 Introduction**

This chapter introduces the 21064/21064A. The descriptions and lists are meant to familiarize the reader with the microprocessors but are not in great detail or depth. The chapter is organized as follows:

- Architecture

- Chip features

- Backward compatibility

#### **1.2 The Architecture**

The Alpha architecture is a 64-bit load/store RISC architecture designed with particular emphasis on speed, multiple instruction issue, multiple processors, and software migration from other operating systems.

All registers are 64 bits in length and all operations are performed between 64-bit registers. All instructions are 32 bits in length. Memory operations are either loads or stores. All data manipulation is done between registers.

The Alpha architecture supports the following data types:

- 8-, 16-, 32- and 64-bit integers

- IEEE 32-bit and 64-bit floating-point formats

- VAX computer 32-bit and 64-bit floating-point formats

In the Alpha architecture, instructions interact with each other only by one instruction writing to a register or memory location and another instruction reading from that register or memory location. This use of resources makes it easy to build implementations that issue multiple instruction cycles every CPU cycle.

The 21064/21064A uses a set of subroutines, called privileged architecture library code (PALcode), that is specific to a particular Alpha architecture operating system implementation and hardware platform. These subroutines provide operating system primitives for context switching, interrupts, exceptions, and memory management. These subroutines can be invoked by hardware or CALL\_PAL instructions. CALL\_PAL instructions use the function field of the instruction to vector to a specified subroutine. PALcode is written in standard machine code with some implementation-specific extensions to provide direct access to low-level hardware functions. PALcode supports optimizations for multiple operating systems, flexible memory management implementations, and multi-instruction atomic sequences.

The Alpha architecture performs byte shifting and masking with normal 64-bit register-to-register instructions; it does not include single byte load/store instructions. The software implementor must determine the precision of arithmetic traps.

For a complete introduction to the Alpha architecture, see the companion volume, the *Alpha Architecture Handbook*.

#### 1.3 Chip Features

The Alpha 21064/21064A microprocessors are some of the first in a family of chips implementing the Alpha architecture. The 21064/21064A are CMOS super-scalar super-pipelined microprocessors using dual instruction issue.

The 21064/21064A and associated PALcode implements IEEE single and double precision, VAX F\_floating and G\_floating datatypes and supports longword (32-bit) and quadword (64-bit) integers. Byte (8-bit) and word (16-bit) support is provided by byte manipulation instructions. Limited hardware support is provided for the VAX D\_floating datatype.

Other 21064/21064A features include:

- 21064 peak instruction execution rate of

- 300 million operations per second at 150 MHz clock rate

- 332 million operations per second at 166 MHz clock rate

- 400 million operations per second at 200 MHz clock rate

- **21064A** peak instruction execution rate of

- 466 million operations per second at 233 MHz clock rate

- 550 million operations per second at 275 MHz clock rate

- An internal clock generator providing a high-speed chip clock and a pair of programmable system clocks with a frequency of

- CPU clock/2 to CPU clock/8 for 21064

- CPU clock/2 to CPU clock/17 for 21064A

- Flexible external interface supporting a complete range of system sizes and performance levels while maintaining peak CPU execution speed

- Selectable data bus width of 64 bit or 128 bit

- Selectable data bus speed. For example 75 MHz to 18.75 MHz bus speed at 150 MHz CPU clock rate

- Support for external secondary cache including programmable cache size and speed

- An on-chip write buffer with four 32-byte entries

- An on-chip pipelined floating-point unit

- 21064 on-chip cache

- An 8K byte instruction cache

- An 8K byte data cache

- 21064A on-chip cache

- A 16K byte instruction cache

- A 16K byte data cache

- An on-chip demand paged memory management unit consisting of:

- A 12-entry I-stream translation buffer (ITB) with 8 entries for 8K pages and 4 entries for 4 MB pages

- A 32-entry D-stream translation buffer (DTB) with each entry able to map a single 8K, 64K, 512K, or 4 MB page

- Parity and ECC

- 21064 provides on-chip support for data bus parity and ECC

- 21064A provides parity for on-chip Icache and Dcache as well as on-chip support for data bus parity and ECC

- Chip and module level test support

- 3.3-volt power supply with interface to 5-volt logic

See Chapter 7 for the 21064/21064A electrical characteristics (dc and ac).

### **1.4 Backward Compatibility**

The **21064A** is backward compatible with the **21064**. The compatibility includes pin layout, PALcode, and application programs.

The following restrictions apply to the compatibility between the **21064A** and **21064**:

- The **21064A** has internal pulldown resistors on inputs which are unused spare pins on the **21064**. If these spare pins are unconnected on a module designed for the **21064**, then there will be no migration problem with these pins.