# MODEL NS23P ADD-IN MEMORY SYSTEM SERVICE MANUAL

# MODEL NS23P ADD-IN MEMORY SYSTEM SERVICE MANUAL

This document, and all subject matter disclosed herein, are proprietary items which National Semiconductor Corporation retains the exclusive rights of dissemination, reproduction, manufacture, and sale. This document is submitted in confidence for consideration by the designated recipient or intended using organization alone, unless permission for further disclosure is expressly granted in writing by National Semiconductor Corporation.

Copyright <sup>C</sup> 1978 National Semiconductor Corporation

### PREFACE

This service manual provides information required to install and maintain the National Semiconductor Corporation (NSC) Model NS23P Add-In Memory System.

The information provided in this manual is comprised of the following:

- System Overview

- Theory of Operation

- Installation

- Maintenance

- Troubleshooting

- Reference Drawings

For additional documentation information, contact:

National Semiconductor Corporation Memory Systems Division 2900 Semiconductor Drive Santa Clara, Ca. 95051 (408) 733-2600

|  |  | • |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

# TABLE OF CONTENTS

| Section |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SYSTEM OVE                                                                                                                                                                                                              | ERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-1                                                                                                                                                         |

|         | 1.1<br>1.2<br>1.2.1<br>1.2.1.1<br>1.2.1.2<br>1.2.1.3<br>1.2.1.4<br>1.2.2<br>1.2.2.1<br>1.2.2.2<br>1.2.2.3<br>1.3<br>1.4<br>1.4.1<br>1.4.2<br>1.4.3<br>1.5                                                               | General Description                                                                                                                                                                                                                                                                                                                                                                                                    | 1-1<br>1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-3<br>1-3<br>1-4                                                                     |

| 2       | THEORY OF                                                                                                                                                                                                               | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                              | 2-1                                                                                                                                                         |

|         | 2.1<br>2.1.1<br>2.1.1.2<br>2.1.1.3<br>2.1.1.4<br>2.1.1.5<br>2.1.1.6<br>2.1.1.7<br>2.1.1.8<br>2.1.2<br>2.1.2.1<br>2.1.2.2<br>2.1.2.1<br>2.1.2.2<br>2.2.2<br>2.2.3<br>2.3<br>2.4<br>2.5<br>2.5.1<br>2.5.2<br>2.5.3<br>2.6 | Interface Description. Input Signals to Memory System. BDOUT. BDIN. BSYNC. BWTBT. BREF. REF KILL. BDCOK. BINIT. Output Signals. PARERR. BRPLY. Bi-Directional Signals (BDALOO-BDAL17 Functional Overview. READ Cycle Overview. WIRTE Cycle Overview. Other Cycles. DC Power Circuitry. Memory Organization. Data Paths. READ Cycle/Parity Check. WRITE Cycle/Parity Generation. READ-MODIFY-WRITE. Timing and Control. | 2-1<br>2-3<br>2-3<br>2-3<br>2-3<br>2-4<br>2-4<br>2-4<br>2-4<br>2-4<br>2-13<br>)2-13<br>2-13<br>2-14<br>2-14<br>2-14<br>2-17<br>2-18<br>2-18<br>2-18<br>2-19 |

# TABLE OF CONTENTS (Continued)

| Section |                                                                                     |                                                                                                                                                        | PAGE                                         |

|---------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2       | THEORY OF                                                                           | OPERATION (continued)                                                                                                                                  |                                              |

|         | 2.6<br>2.6.1<br>2.6.1.1<br>2.6.1.2<br>2.6.1.3<br>2.6.1.4<br>2.6.1.5<br>2.6.2<br>2.7 | Timing and Control.  Cycle Timing.  External Request.  Read Cycle.  Write Cycle.  Read-Modify-Write  Refresh Cycle.  Reserved I/O.  Memory Addressing. | 2-19<br>2-20<br>2-23<br>2-23<br>2-23<br>2-24 |

| 3       | INSTALLAT                                                                           | ION                                                                                                                                                    | 3-1                                          |

|         | 3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.4<br>3.5                          | Tools Required                                                                                                                                         | 3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-4       |

| 4       | MAINTENAN                                                                           | CE AND TROUBLESHOOTING                                                                                                                                 | 4-1                                          |

|         | 4.1<br>4.2                                                                          | Maintenance Troubleshooting                                                                                                                            |                                              |

| Appendi | x                                                                                   |                                                                                                                                                        |                                              |

| А       | REFERENCE                                                                           | DRAWINGS                                                                                                                                               | A-1                                          |

## LIST OF ILLUSTRATIONS

| Figure       |                                                 | Page |

|--------------|-------------------------------------------------|------|

| 2-1          | Read (DATI) Timing                              | 2-5  |

| 2-2          |                                                 |      |

| 2-3          |                                                 |      |

| 2 4          |                                                 | 2-11 |

| 2 <b>-</b> 5 | NS 11/02P Block Diagram                         |      |

| 2 <b>-</b> 6 | Block Diagram Timing and Control                |      |

| 2-7          | Read Cycle (DATI) - Internal Timing Diagram     |      |

| 2-8          | Write Cycle (DATO-B) - Interface Timing Diagram |      |

| 2-9          | Read-Modify-Write (DATIO-B) - Internal Timing   |      |

|              | Diagram                                         | 2-29 |

| 2-10         | Internal Refresh Cycle                          | 2-31 |

| 2-11         | External Refresh Cycle                          |      |

| 3-1          | Switch and Jumper Locations                     | 3-3  |

| 3-2          | Module Installation                             | 3-8  |

# LIST OF TABLES

| <u>Table</u> |                                  | Page |

|--------------|----------------------------------|------|

| 2-1          | I/O Connector Pin List           | 2-2  |

| 3-1          | Address Range Switch Programming | 3-5  |

| 3-2          | Option Jumper                    | 3-7  |

Model NS23P Add-In Memory System

#### SECTION 1

#### SYSTEM OVERVIEW

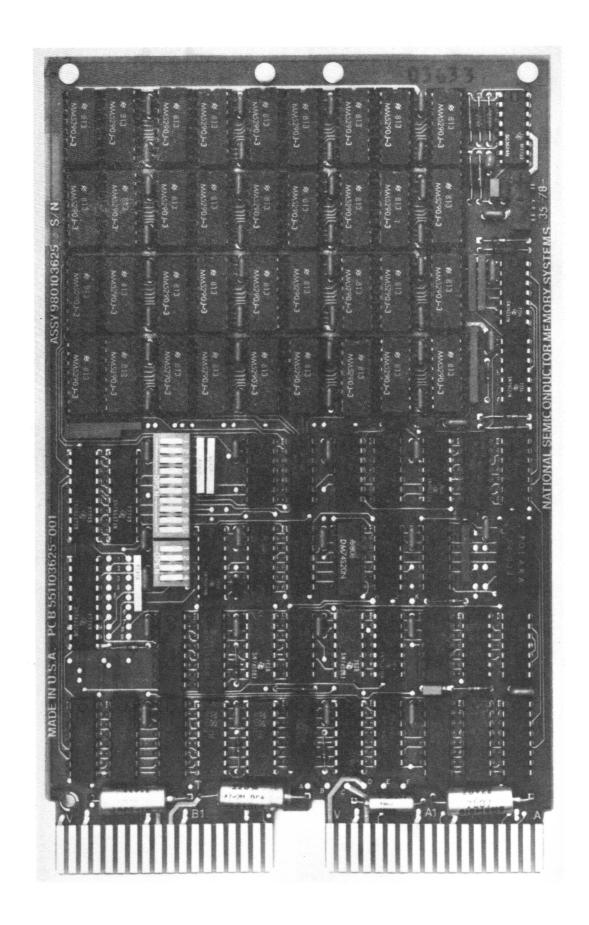

This section provides a general description of the NS23P memory card, including compatibility with other cards and systems; features and options; a mechanical description; power and environmental requirements for proper use; and other documentation.

## 1.1 GENERAL DESCRIPTION

The NS23P memory card is an add-in memory designed to be compatible with the DEC\* (Digital Equipment Corp.) LSI-11/23, PDP-11/03, and LSI-11/2 Microcomputer Systems. The card can be installed in the H928l or H9270 backplanes and works in conjunction with the DEC MSV11-D and MSV11-E series semiconductor memory cards.

Its standard memory capacity is 32,768 words by 18 bits ( $32k \times 18$ ). The 32,768 words can be assigned anywhere within the LSI-11 128k word address space in any one or multiple 4k word increments.

## 1.2 FEATURES AND OPTIONS

## 1.2.1 FEATURES

The following paragraphs discuss the user controllable features of the NS23P memory card.

<sup>\*</sup>DEC, LSI 11, LSI 11/23, LSI 11/2 and PDP-11/03 are registered trademarks of the Digital Equipment Corporation.

## 1.2.1.1 Internal or External Refresh

The user can select whether refresh is controlled by the LSI-11 processor or by the refresh circuitry on the card itself through jumper points provided on the board.

## 1.2.1.2 Battery Back-up Provisions

The NS23P memory card can be used with battery back-up for LSI-11 semiconductor memory systems. The card comes with +5VB and +12VB battery back-up voltage pins, compatible with the voltage pins DEC provided on the MSV11 MOS memory card.

## 1.2.1.3 BRPLY External Refresh Response

The NS23P memory card can be configured for external refresh operations during installation. Jumper points are provided on the card which permit the user to allow the generation of a BRPLY signal to an external refresh command.

## 1.2.1.4 Expanded Address Space Operation

The standard NS23P memory card can operate anywhere within the 128k address space of the LSI-11/23 system.

#### 1.2.2 OPTIONS

There are the following factory installable options for the NS23P memory card.

### 1.2.2.1 Parity Generation and Check

See paragraphs 2.1.2.1, 2.5.1, and 2.5.2 for discussions of parity generation and check.

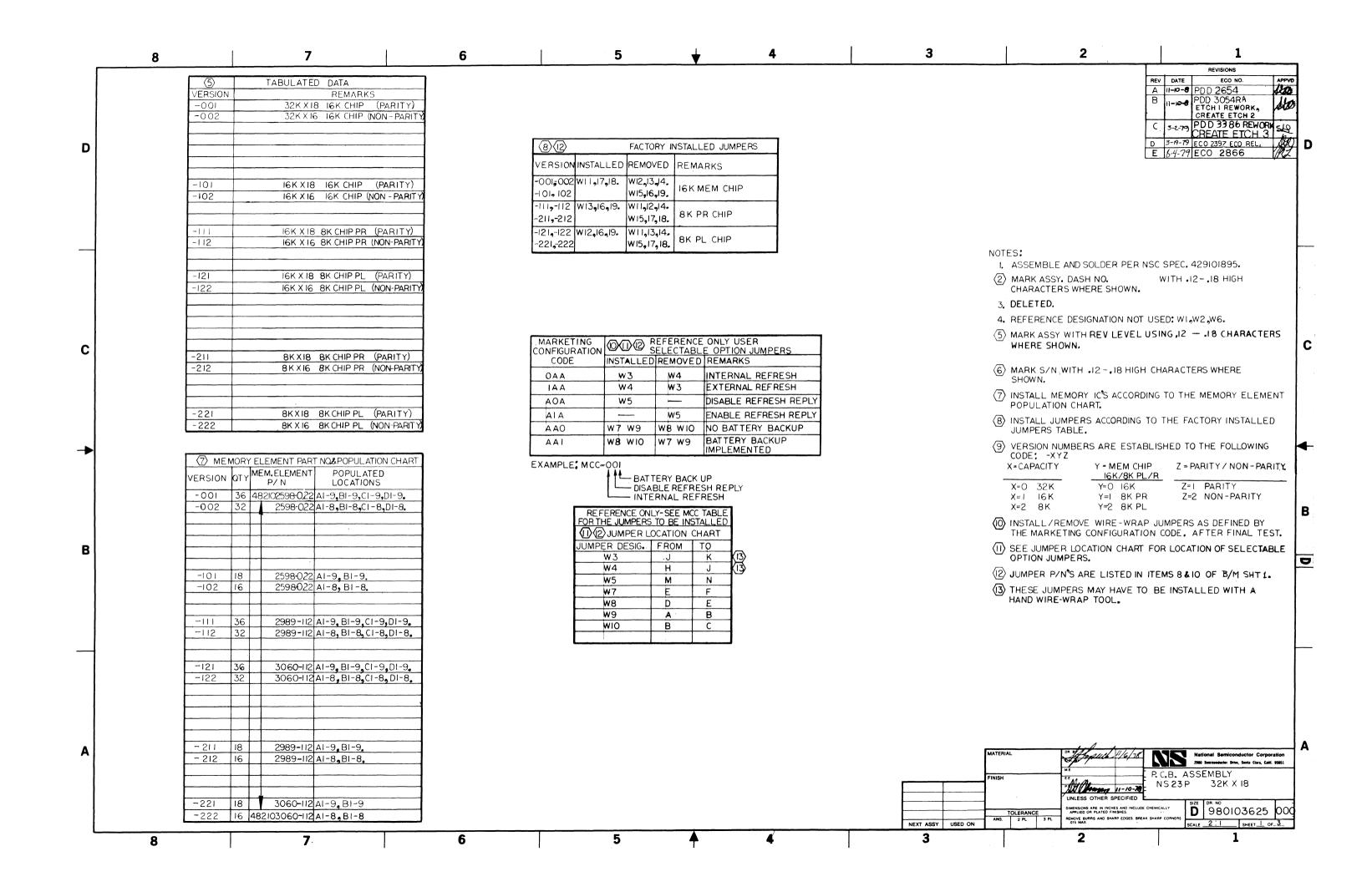

### 1.2.2.2 8k or 16k RAM Operation

The standard NS23P card uses 16k RAMs as the memory elements, providing a maximum storage capacity per card of 32k words. The user can select 8k RAMs as the memory elements when ordering. This option permits maximum storage capacity per card of 16k words.

## 1.2.2.3 Optional Capacities

Optional capacities are available from a minimum of 4,096 words by 16 bits  $(4k \times 16)$  to a maximum of 32,768 words by 18 bits  $(32k \times 18)$ .

### 1.3 MECHANICAL DESCRIPTION

The NS23P memory is completely contained on one multilayer printed circuit card. It is designed to plug directly into standard H9270 ("Quad"), H9281 ("Dual") LSI-ll backplane/card guide assemblies, and the DDV11-B ("Hex") expansion unit. Its dimensions are:

| PCB  | Thickness        | 0.056" | Nominal                    |

|------|------------------|--------|----------------------------|

|      | Width            | 5.19"  |                            |

|      | Length           | 8.93"  | (Includes plastic handles) |

| Max. | component height | 0.375" |                            |

| Max. | total thickness  | 0.490" |                            |

#### 1.4 POWER REQUIREMENTS

The following are power requirements for the use of the NS23P memory card.

## 1.4.1 PARAMETERS AND CONDITIONS

The NS23P requires both of the following voltages: +5.0 volts +5% and +12.0 volts +5%.

### 1.4.2 POWER CONSUMPTION

The NS23P memory card in a 32k  $\times$  18 configuration has the following current requirements:

|             | Standby     | <u>Operating</u> |  |

|-------------|-------------|------------------|--|

| +5.0 volts  | 2.0 A max.  | 2.0 A max.       |  |

| +12.0 volts | 110 mA max. | 450 mA max.      |  |

## 1.4.3 BATTERY BACK-UP VOLTAGE REQUIREMENTS

The battery back-up voltages must meet requirements (per card) of +12 volts  $\pm$  5% at 110 mA max. and +5 volts  $\pm$  5% at 775 mA max.

# 1.5 ENVIRONMENTAL REQUIREMENTS

The NS23P memory card will operate at a temperature of  $5^{\circ}C$  to  $50^{\circ}C$  and at a humidity of 10% to 90% (no condensation).

#### SECTION 2

#### THEORY OF OPERATION

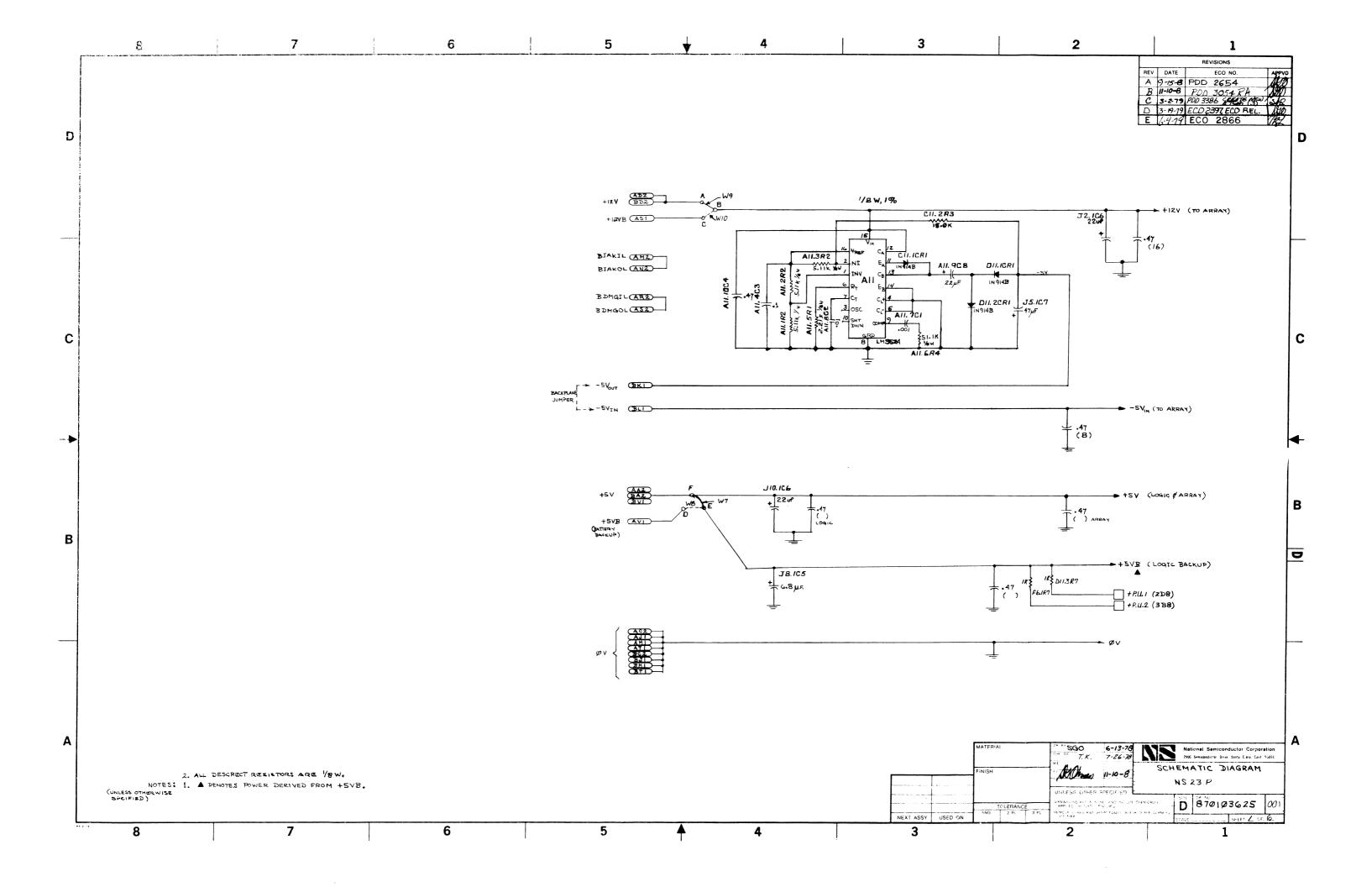

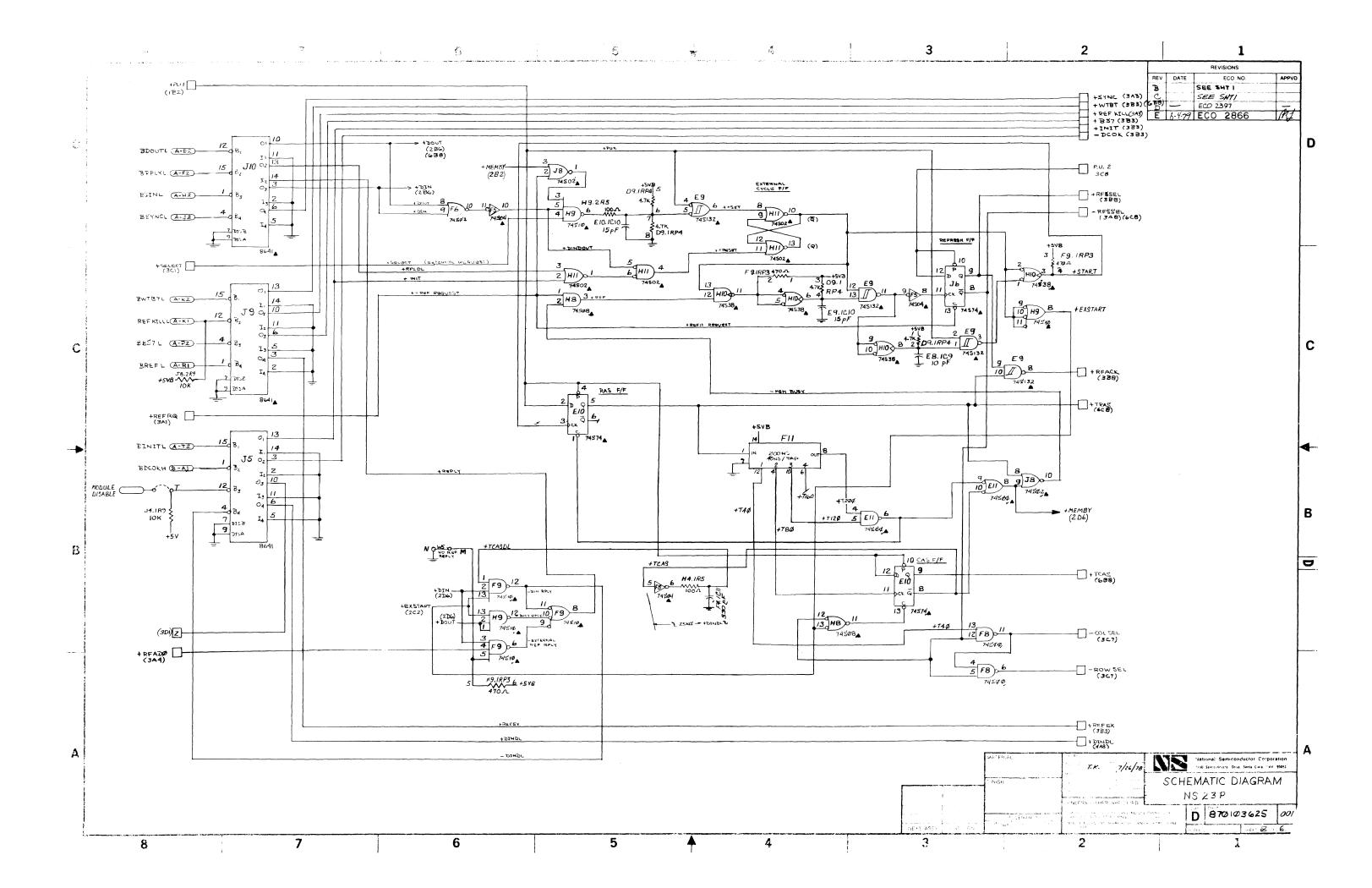

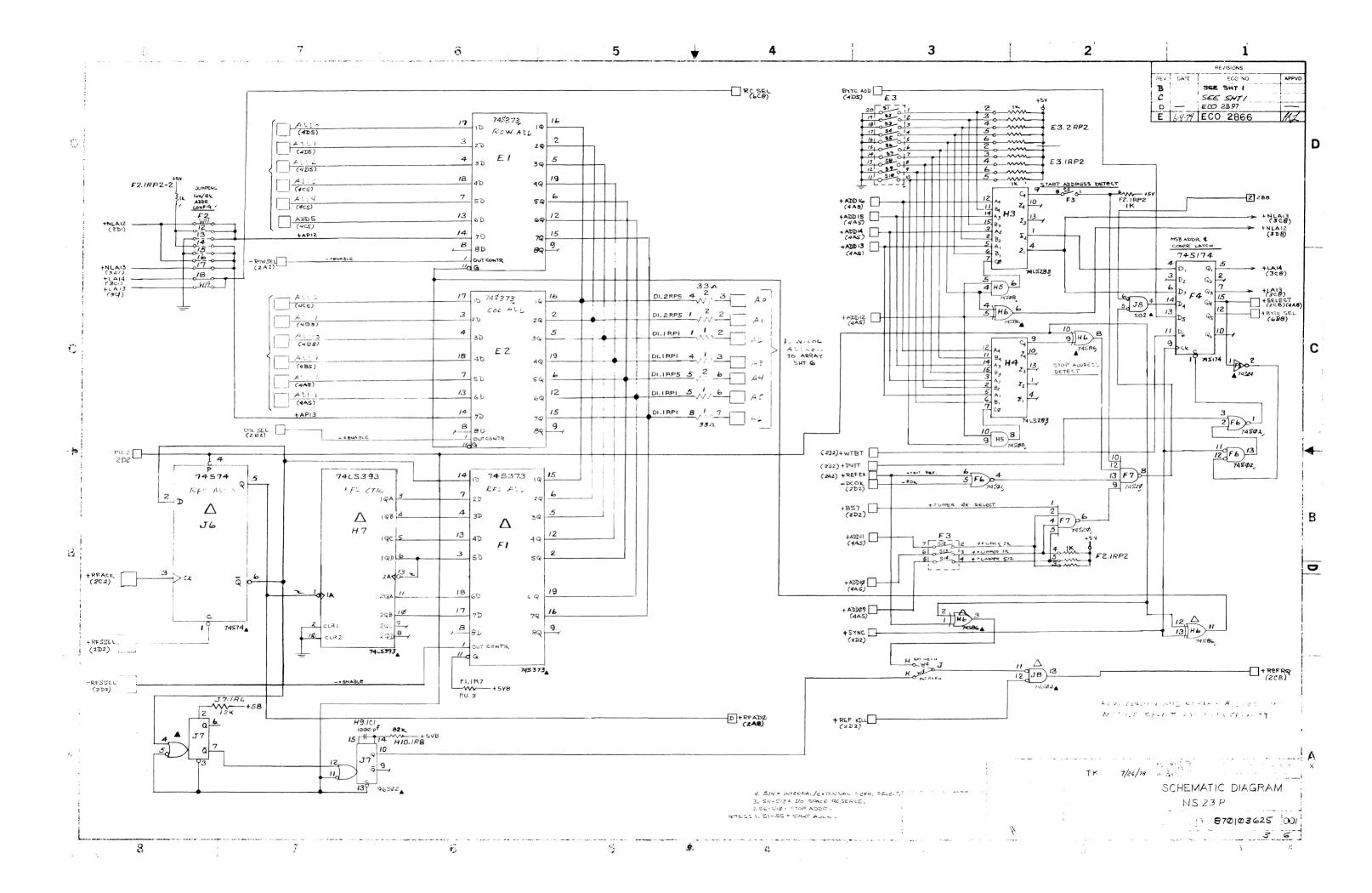

This section provides a detailed discussion of the operation of the NS23P add-in memory. Beginning with an interface description, the discussion proceeds with a functional overview of the card, using a block diagram. Individual functional blocks, data paths, and timing considerations are then covered, with an emphasis on use of the schematics in Appendix A.

## 2.1 INTERFACE DESCRIPTION

Interface between the NS23P add-in memory system and the Digital Equipment Corporation LSI-ll Microcomputer System (or others) is conducted by means of eight input signals to the NS23P, two output signals to the CPU, and 18 bi-directional signal lines (address and data) on the memory card. Table 2-l gives the connector assignments of signals, power, and other elements of the interface.

The memory card presents one standard bus load to the LSI-ll bus for each of the signals.

## 2.1.1 INPUT SIGNALS TO MEMORY SYSTEM

The eight input signals from the LSI-11 CPU to the NS23P are described briefly in this section. The specific purpose of each signal in the operation of the memory system will become clear as each functional module of the system is described in detail later in this section.

Table 2-1. I/O Connector Pin List

| Component Side                         | Pin                                          | Pin                                          | Solder Side                                                    |

|----------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------------------------|

| A Connector                            |                                              |                                              |                                                                |

| BDAL16 L<br>BDAL17 L                   | A1<br>B1<br>C1<br>D1<br>E1<br>F1             | A2<br>B2<br>C2<br>D2<br>E2<br>F2             | +5 Volts<br>Ground<br>+12 Volts<br>BDOUT L<br>BRPLY L          |

| Ground<br>REF KILL L<br>Ground         | H1<br>J1<br>K1<br>L1<br>M1<br>N1             | H2<br>J2<br>K2<br>L2<br>M2<br>N2             | BDIN L<br>BSYNC L<br>BWTBT L<br>BIAKI L<br>BIAKO L             |

| BREF L<br>+12V BATT<br>Ground          | P1<br>R1<br>S1<br>T1<br>U1                   | P2<br>R2<br>S2<br>T2<br>U2<br>V2             | BBS7 L<br>BDMGI L<br>BDMGO L<br>BINIT L<br>BDAL00 L            |

| +5V BATT                               | V1                                           | V2                                           | BDAL01 L                                                       |

| B Connector                            |                                              |                                              |                                                                |

| BDCOK                                  | Al<br>Bl<br>Cl<br>Dl<br>El<br>Fl<br>Hl       | A2<br>B2<br>C2<br>D2<br>E2<br>F2<br>H2       | +5 Volts  Ground +12 Volts BDAL02 L BDAL03 L BDAL04 L          |

| Ground -5 Volts out -5 Volts in Ground | J1<br>K1<br>L1<br>M1<br>N1<br>P1<br>R1<br>S1 | J2<br>K2<br>L2<br>M2<br>N2<br>P2<br>R2<br>S2 | BDAL05 L BDAL06 L BDAL07 L BDAL08 L BDAL09 L BDAL10 L BDAL11 L |

| Ground                                 | Tl .<br>Ul                                   | T2<br>U2                                     | BDAL12 L<br>BDAL13 L<br>BDAL14 L                               |

| +5 Volts                               | V1                                           | V2                                           | BDAL15 L                                                       |

## 2.1.1.1 BDOUT

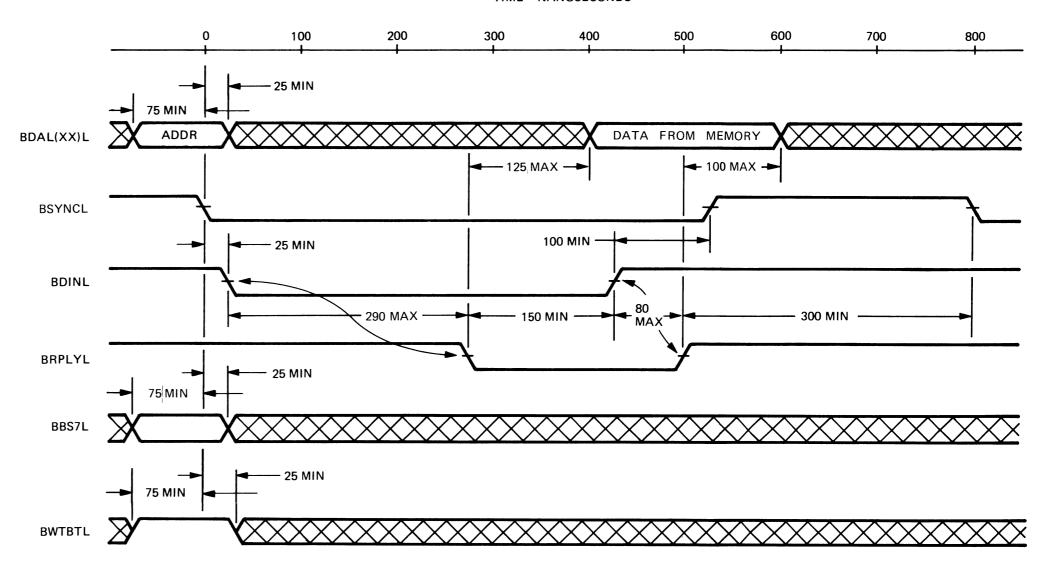

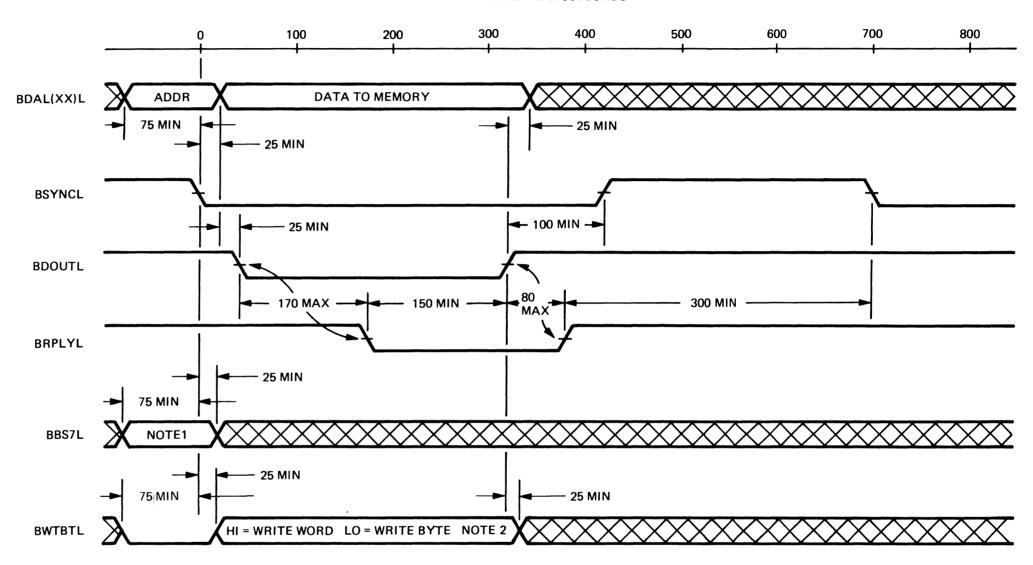

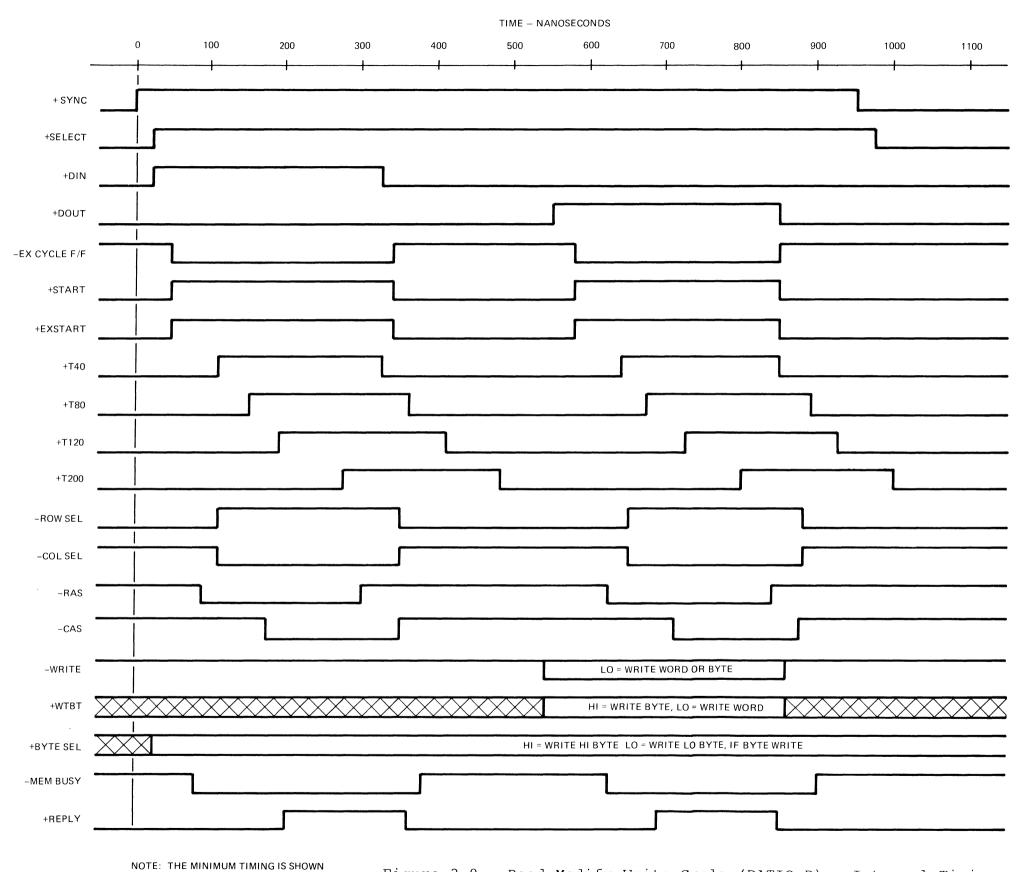

This signal is an indication to the memory card that a write (DATO) cycle is to be performed. It must be activated as shown in the timing diagrams in Figures 2-1 and 2-2 in the proper relationship to BSYNC.

### 2.1.1.2 BDIN

This signal is an indication to the memory card that the BRPLY response from the memory card is to be activated during a read cycle (DATI), the read portion of read-modify-write, or an external refresh cycle. It must be activated as shown in Figures 2-1, 2-3, and 2-4 in proper time relationship with BSYNC.

## 2.1.1.3 BSYNC

This signal is an indication to the memory card that either a read (DATI) or read-modify-write (DATIO-B) cycle will be initiated, a write cycle will be initiated when BDOUT is received, or an external refresh cycle should be initiated. The type of cycle initiated is a function of the state of the BDIN, BDOUT, and BREF lines when BSYNC goes to its active state as shown in Figures 2-1 through 2-4.

### 2.1.1.4 BWTBT

This signal, when used in conjunction with BSYNC and BDOUT, allows the board to determine whether a whole word (16 bits) or a byte (8 bits) is to be written during a write (DATO) or a read-modify-write (DATIO-B) cycle. Activating BWTBT during a write cycle as shown in Figures 2-2 and 2-3 is an indication to the card to write into the byte specified by address bit AOO.

#### 2.1.1.5 BREF

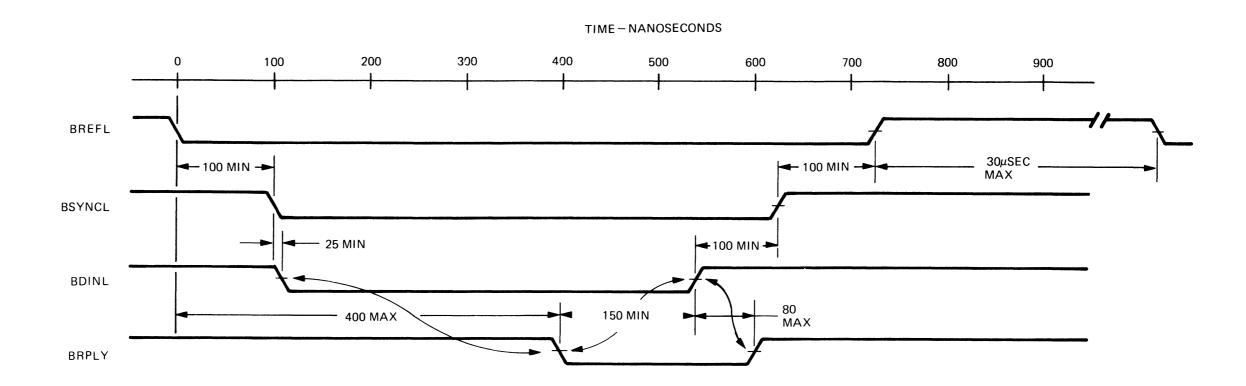

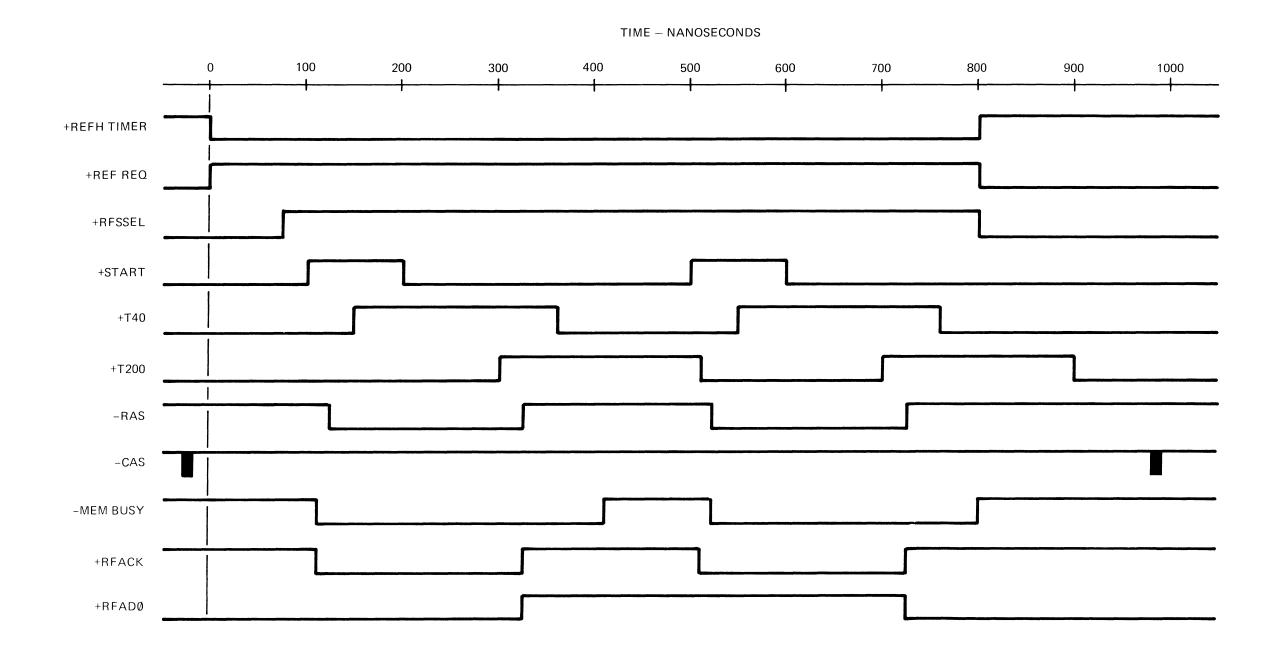

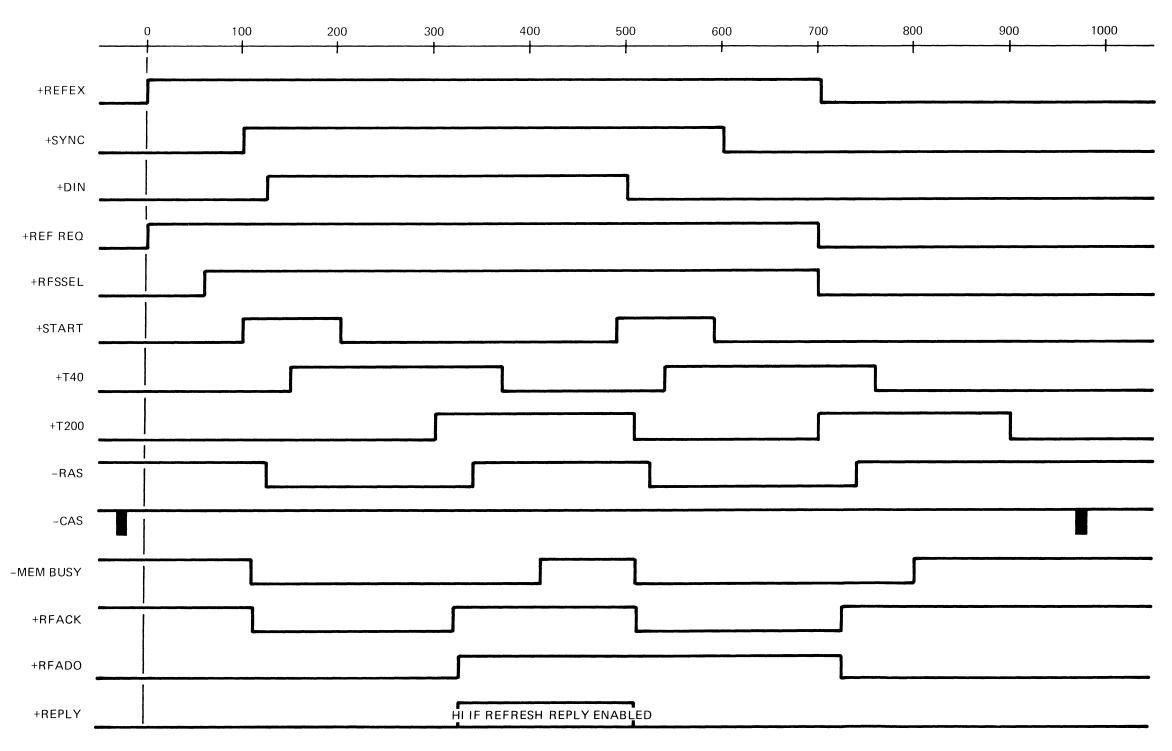

This signal, in conjunction with BSYNC (as shown in Figure 2-4), is an indication to the card to perform a refresh cycle. The card will respond to this signal only if it has been configured for external refresh operation.

## 2.1.1.6 REF KILL

This signal, when active, will disable the internal refresh circuitry from executing a cycle.

## 2.1.1.7 BDCOK

This signal is an indication to the memory card that the LSI-ll system has lost its dc power. It is used to prevent the memory card from being inadvertently selected on power up or power down.

## 2.1.1.8 BINIT

This signal is used to reset internal select registers.

#### 2.1.1 OUTPUT SIGNALS

The two output signals from the NS23P to the LSI-11 CPU are described briefly in this section. The specific purpose of each signal in the operation of the memory system will become clear as each functional module of the system is described in detail later in this section.

#### 2.1.2.1 PARERR

If the parity generation and check option has been selected, PARERR indicates a parity error. Parity is generated on a byte basis on all write cycles and checked on a byte basis on all read cycles. The PARERR signal appears on the address 16 signal line (BDAL 16L).

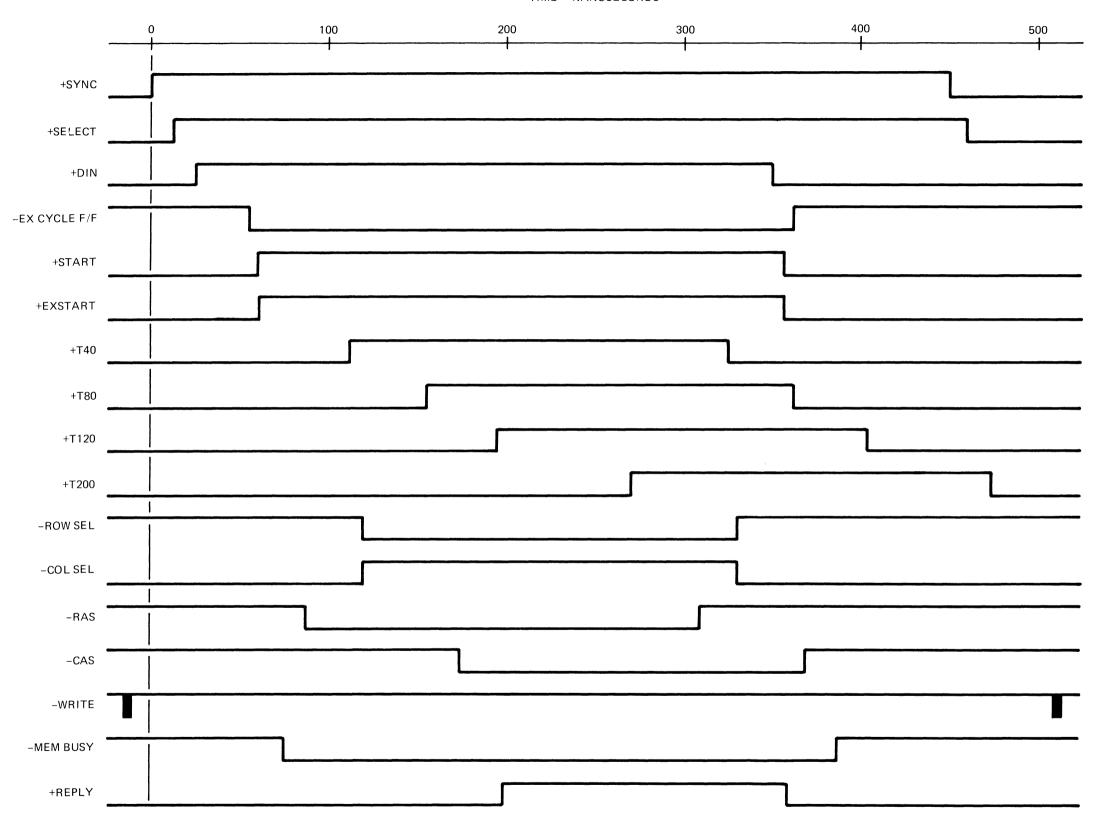

### TIME - NANOSECONDS

- NOTES: 1. BBS7L IS A MEMORY ADDRESS SELECT TERM. BBS7L HI, MEMORY SHALL RESPOND. BBS7L LO AND BANK SELECT SWITCHES OPEN, MEMORY SHALL NOT RESPOND.

- 2. FOR BWTBTL HI DURING DATA TIME, A FULL WORD IS WRITTEN, FOR BWTBTL LO DURING DATA TIME, A BYTE IS WRITTEN ACCORDING TO BDALOOL AT ADDRESS TIME, IF BDALOOL IS HI, BITS 00-07 ARE WRITTEN, IF BDALOOL IS LO, BITS 08-15 ARE WRITTEN.

Figure 2-1. Read (DATI) Timing

## TIME - NANOSECONDS

- NOTES: 1. BBS7L IS A MEMORY ADDRESS SELECT TERM. BBS7L HI, MEMORY SHALL RESPOND. BBS7L LO AND BANK SELECT SWITCHES OPEN, MEMORY SHALL NOT RESPOND.

- 2. FOR BWTBTL HI DURING DATA TIME, A FULL WORD IS WRITTEN, FOR BWTBTL LO DURING DATA TIME, A BYTE IS WRITTEN ACCORDING TO BDAL00L AT ADDRESS TIME, IF BDAL00L IS HI, BITS 00-07 ARE WRITTEN, IF BDAL00L IS LO, BITS 08-15 ARE WRITTEN.

Figure 2-2. Write (DATO-B) Timing

## TIME - NANOSECONDS 900 100 500 600 700 800 1000 1100 1200 1300 200 300 400 BDAL(XX)L ADDR DATA TO MEMORY **→** 100 MAX → **←** 125 MAX **→** — 25 MIN 75 MIN **BSYNCL** 100 MAX - 25 MIN BDINL 290 MAX 150 MIN MAX BRPLYL — 170 MAX —▶ 150 MIN 200 MIN -300 MIN BDOUTL **←** 25 MIN **75 MIN** BBS7L **→** 25 MIN — 25 MIN **◄**— 25 MIN **75 MIN** HI=WRITE WORD LO=WRITE BYTE

Figure 2-3. Read-Modify-Write (DATIO-B) Timing

Figure 2-4. Refresh (EXTERNAL) Timing

## 2.1.2.2 BRPLY

This signal is an acknowledgement by the card of the receipt of a BDIN or BDOUT during a read, write, or read-modify-write mode of operation. It is also an acknowledgement of the receipt of BREF if the card has been configured for external refresh operation.

## 2.1.3 BI-DIRECTIONAL SIGNALS (BDAL00-BDAL17)

The 18 bi-directional signal lines provide the memory card with address and data information. These lines are time-multiplexed between the address and data in/out during any cycle externally requested of the memory card. As shown in Figures 2-1 and 2-2, the card interprets the data on these lines in relationship to BSYNC, BDIN, BDOUT, and BRPLY. At -75 to +25 nanoseconds either side of the falling edge of BSYNC, the data is interpreted as address information; at all other times, as data into or out of the card.

#### 2.2 FUNCTIONAL OVERVIEW

This section describes the operation of the NS23P during write and read cycles from a general standpoint. Detailed discussion of the timing for each of these cycles is provided elsewhere in the manual.

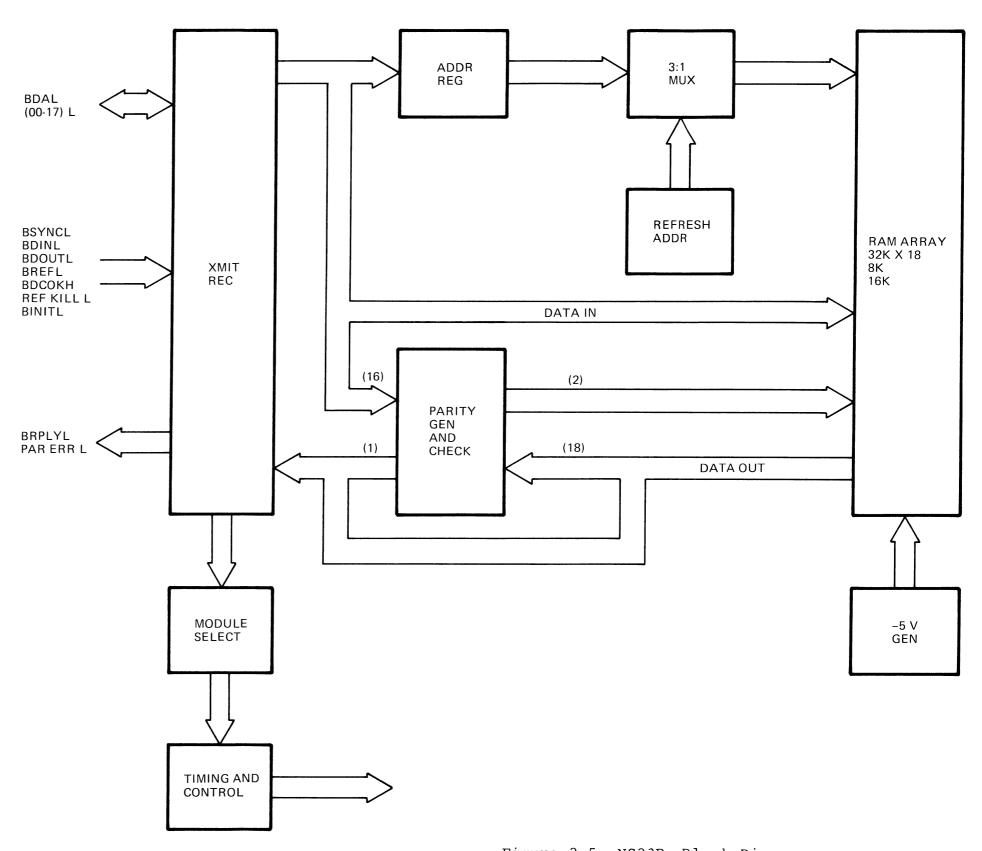

Figure 2-5 is the block diagram for the NS23P. The major blocks of the memory system are the interface transmitter-receiver, the address register, the parity generation and checking unit, the refresh address, module select, timing and control, the three-to-one multiplexer, and the memory array itself. The memory array may be configured from 8k x 16 bit minimum to 32k x 18 bit maximum; the 18-bit width with parity, the 16-bit width without.

#### 2.2.1 READ CYCLE OVERVIEW

Data coming from the interface transmitter-receiver along the BDAL lines (0-17) is asserted 75 nanoseconds (ns) before the low-going edge of the BSYNC line and held for 25 ns beyond it, thus defining address time (see Figure 2-1). Simultaneously with address time, the bank select signal (BBS7) determines if the memory module or a peripheral is to respond. The remaining time for the bus is defined as data time.

At the end of address time, the BDIN signal is taken low, and hand-shaked with a reply signal (BRPLY) from the memory card 225 ns (max.) later. In sequence, 125 ns (max.) after BRPLY goes low, data is brought from memory to the bus; 150 ns (min.) after BRPLY has gone low the processor returns BDIN to its high state; BRPLY returns to high; BSYNC returns high. Data remains on the bus for 100 ns (max.) after BRPLY goes high, and a new cycle may be initiated after 300 ns (min.).

## 2.2.2 WRITE CYCLE OVERVIEW

The write cycle operates on the same principle as the read cycle with a slight difference in timing. Data is available on the bus immediately after address time, then the handshaking between BDOUT and BRPLY takes place as before. The BWTBT is also brought into play during the write cycle: If BWTBT is high, a full word is written; if BWTBT is low, a byte is written in conjunction with the BDAL00 signal (BDAL00 high, bits 00-07; BDAL00 low, bits 08-15). The memory module is selected according to the address and BBS7, as in the case of a read cycle.

#### 2.2.3 OTHER CYCLES

This concludes the overview of the two main cycles in the NS23P memory system. The read-modify-write and refresh cycles will be described in detail in Section 2.5. No overview is provided since the read-modify-write cycle is essentially a read followed by a write cycle.

Figure 2-5. NS23P Block Diagram

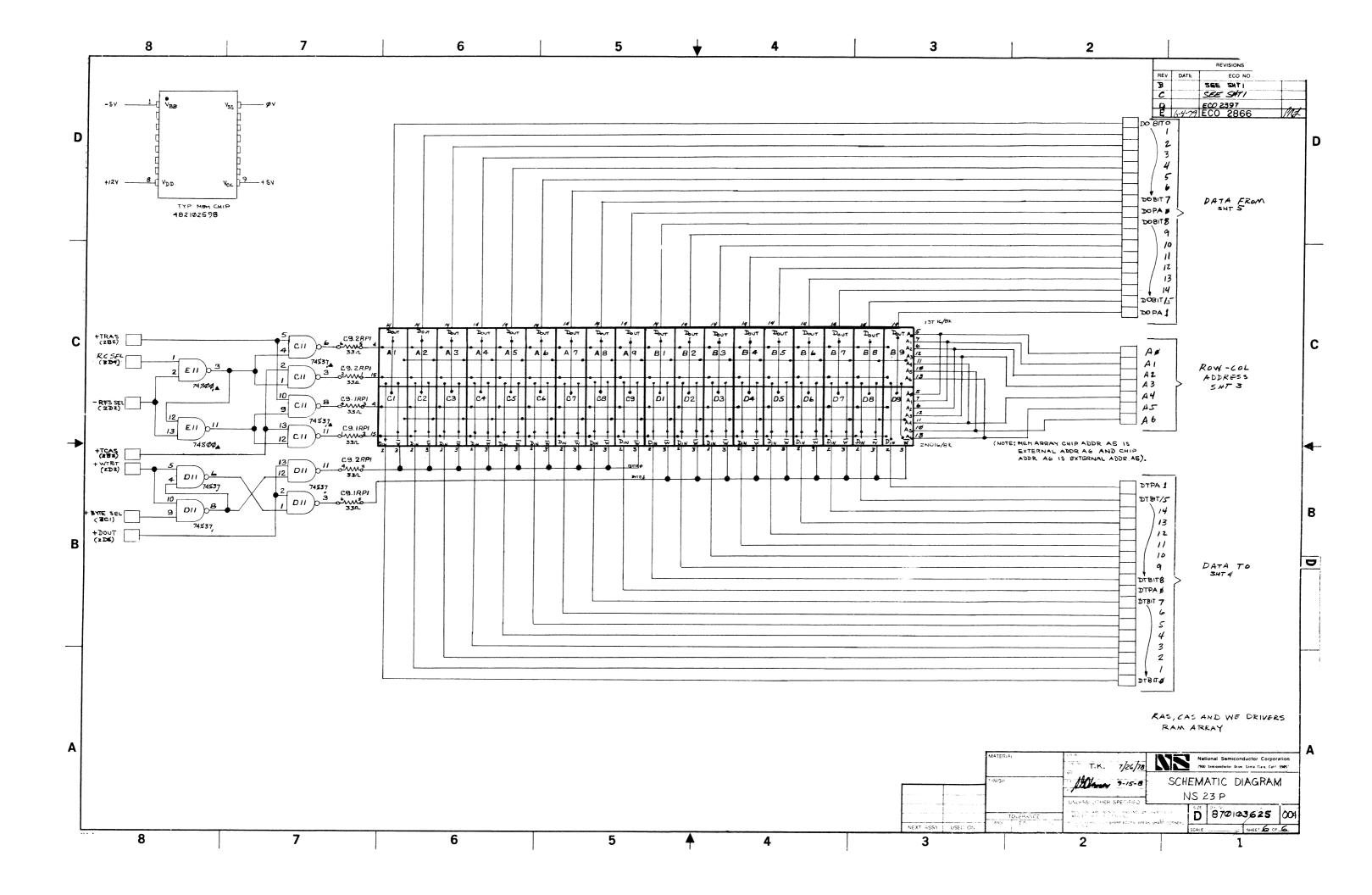

## 2.3 DC POWER CIRCUITRY

DC voltage is brought in as +12 volts at input pin AD2 and BD2 as shown on sheet 1 of Figure A-1 (see Appendix A). Part of the +12 volt supply is run through a capacitive filter and directly to the memory array. A second part of the +12 volt supply is run through a dc to dc converter at IC location All, where -5 volts is generated. This -5 volts is led out at pin BK1 where it is backplane-jumpered back in at pin BL1. Alternatively, a -5 volt source may be brought in directly at pin BL1 (no jumper). In either case, the -5 volts at BL1 is run directly to the memory array; it is used nowhere else.

A +5 volt source is brought in at pins AA2, BA2, and BV1, filtered, then run to both the memory array and the logic circuitry.

Provision has been made for battery backup power. If the system is so configured, the +12 volt input will be jumpered to the battery input at pin AS1, and the +5 volt jumpered to pin AV1. If battery power is used, the +5 volt battery supply is run only to that portion of the logic circuitry needed to maintain refresh (+5 volts is not required on the memory chip itself for data retention). For reference, those IC's that use the +5 volt battery source are indicated by a triangle at the IC gates on the schematic.

### 2.4 MEMORY ORGANIZATION

The standard memory capacity of the memory card is 32,768 words by 18 bits ( $32k \times 18$ ), which can be assigned in 4k increments anywhere within the LSI-ll 128k word address space. Optional capacities are available from a minimum of 4,096 words by 16 bits ( $4k \times 16$ ) to the maximum of  $32k \times 18$ .

Also available as an option is switch-settable reserved I/O space such that 4k, 2k, 1k, or 512-word address locations in the upper portion of the address range can be reserved for device addresses.

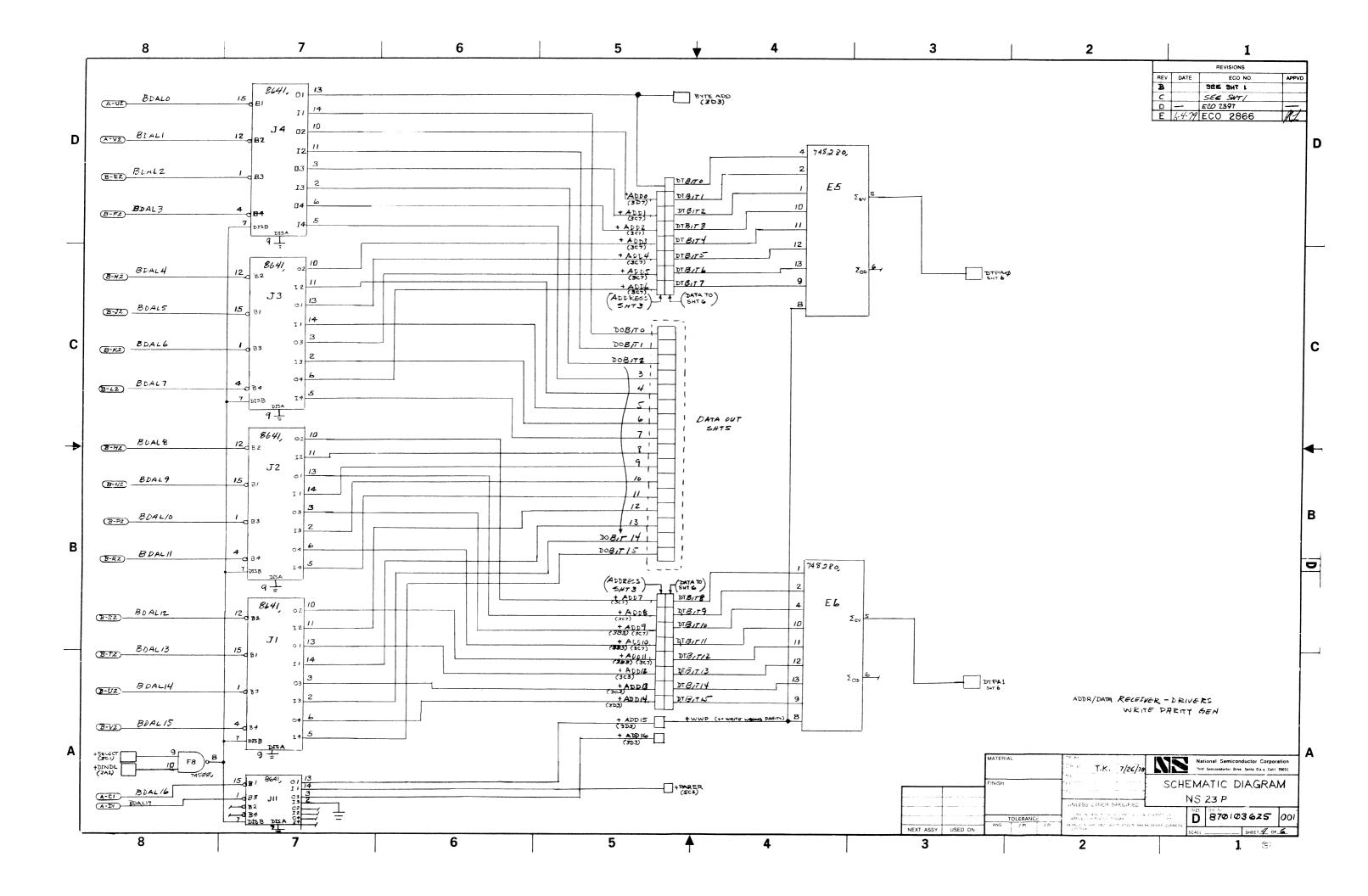

## 2.5 DATA PATHS

This section consists of an expansion of the discussion of the read and write cycles in Section 2.2, as well as a detailed description of the read-modify-write cycle not described there. In this section, the schematic diagrams applicable to each operation will be used rather than the block diagram.

### 2.5.1 READ CYCLE/PARITY CHECK

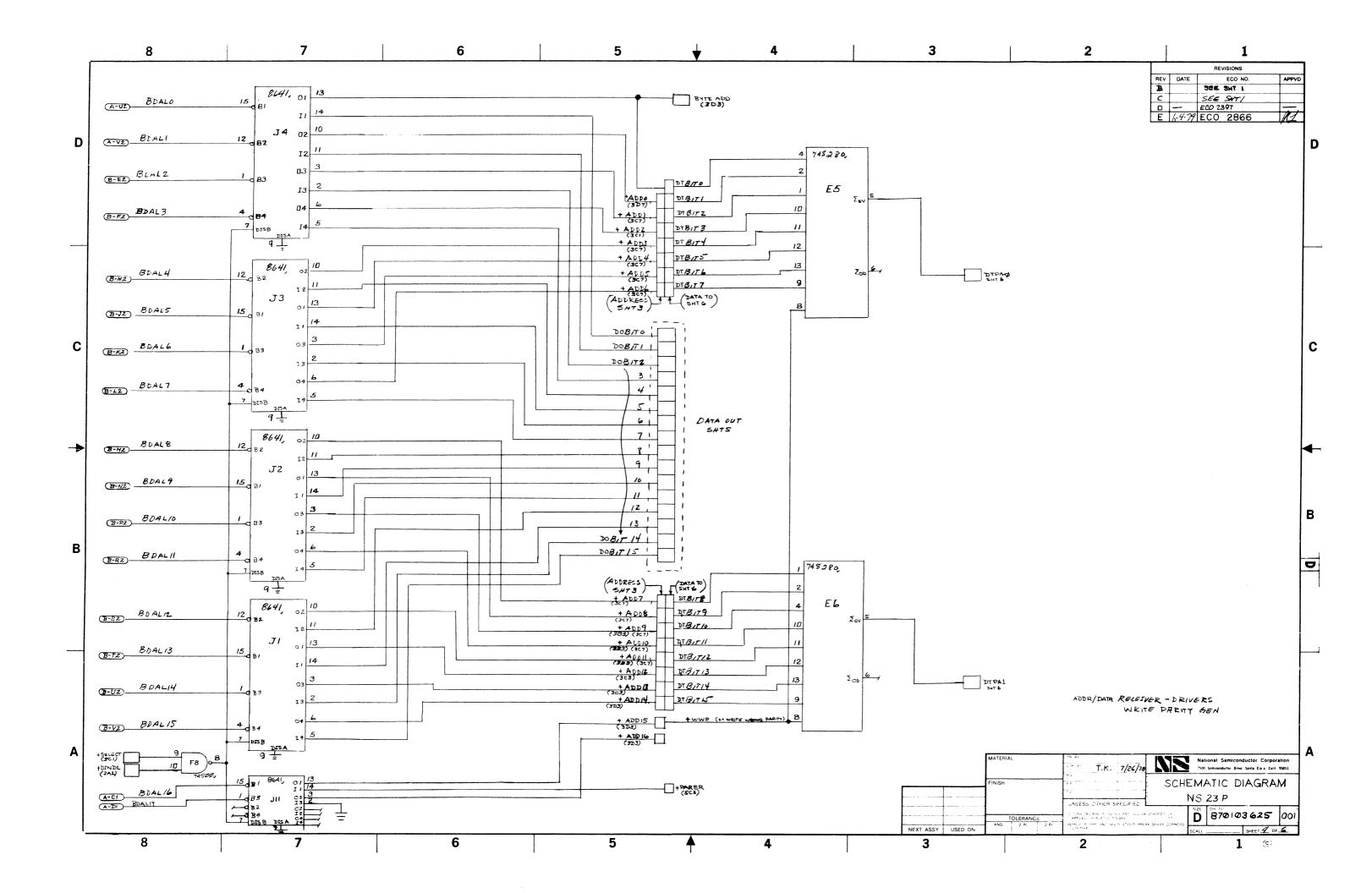

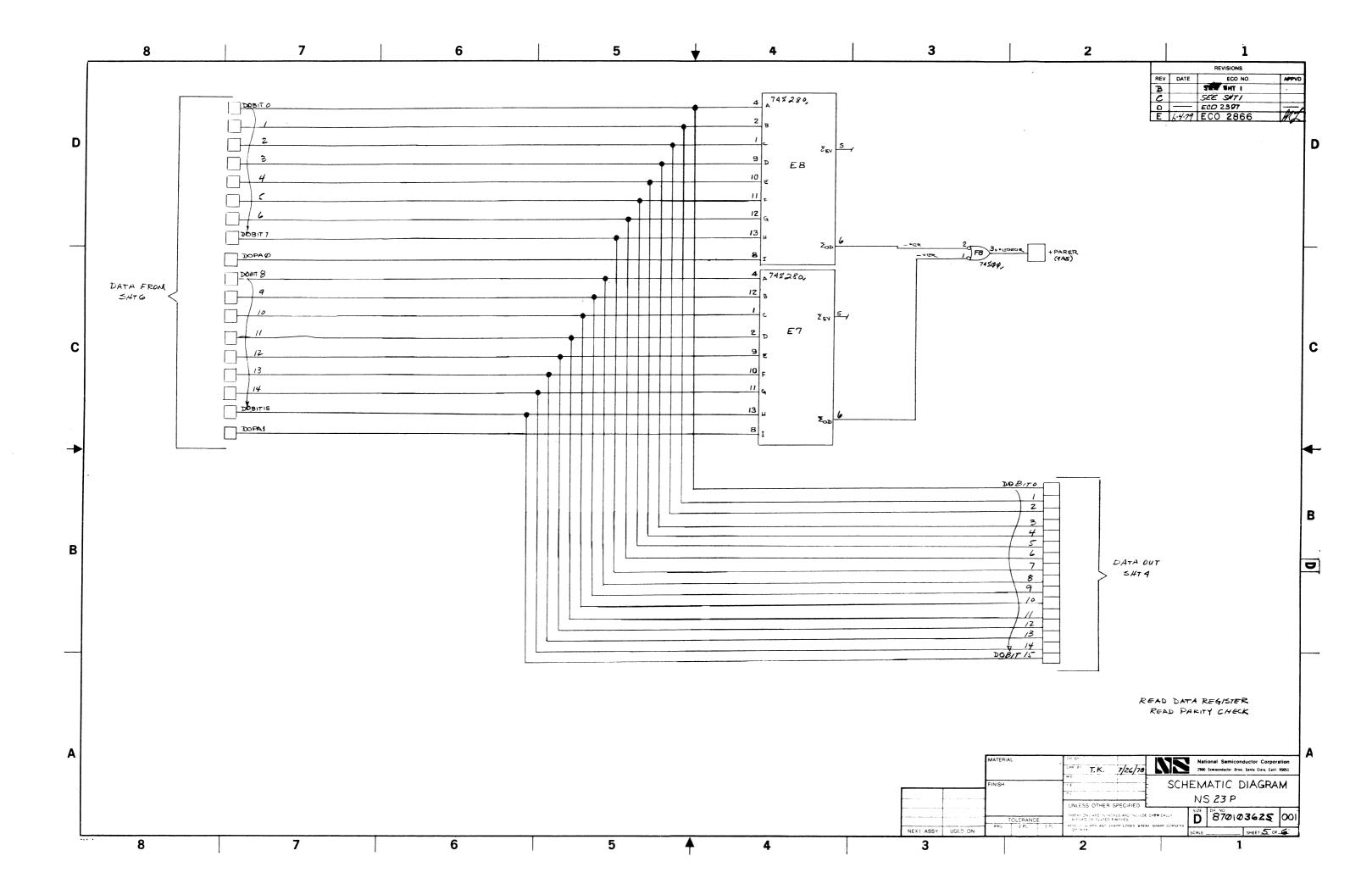

As shown on sheet 6 of Figure A-1 in Appendix A, the data leaves the memory chips at pin 14 and is routed to two sources.

First, parity is checked (see Figure A-1, sheet 5). All of the data bits 0 through 15, including the parity bits, are brought into two 74S280 parity checkers (E7 and E8). Output pin 6 of E8, which is the parity check for the low byte on data bits 0 through 7, must always be high for the correct parity check to be performed. If an incorrect parity is developed in any of the data bits (including the parity bit), then this output will go low, signaling the parity error as a high output at pin 3 of gate F8. This high signal is the parity error signal that goes back to the driver and ultimately to the BDAL 16 line.

The data output from the memory elements also goes to IC's J4, J3, J2 and J1 (Figure A-1, sheet 4) running in the transmit mode, and to the bus via the BDAL 0 through 15 lines. If the parity error is active, it is input at (IC) J11 pin 14, and the output appears on the BDAL 16 line.

#### 2.5.2 WRITE CYCLE/PARITY GENERATION

During a write cycle, data is brought in to the 8641 transmitter/

receivers J4, J3, J2, and J1 on lines BDAL 0-17 from the

bus. The receivers invert the data and distribute it to pin 2

of the memory array and to the parity generation circuits, IC's

E5 and E6 (Figure A-1, sheet 4).

E5 develops the parity bit for the low-order byte and E6 the parity bit for the high-order byte. The BDAL 16 line, when set (active low), sets the input at E5-13 and E6-13 high and, in effect, writes parity opposite to that developed on each of the bytes individually for diagnosite check of the parity function.

Data may also be written as a byte. If BWTBT is issued low, the BLALO is interpreted as a byte select address. This signal, input at J4 pin 15, is output at pin 13 and run to F4 pin 13 (Figure A-1, sheet 3), where the output at pin 12 is latched with the leading edge of the SYNC signal. This term then runs to Dll pin 9 (Figure A-1, sheet 6), which in addition to gates Dll with output pins 3 and 11 form the write enable inputs to the memory array according to conditions established at the interface.

#### 2.5.3 READ-MODIFY-WRITE

The read-modify-write cycle is a combination of a read cycle and a write cycle, differentiated from the individual functions only in its timing. While the memory treats the read-modify-write cycle as two internal cycles, to the processor or the external world, it is one cycle. The cycle timing will be discussed in greater detail in paragraph 2.6.1.4.

## 2.6 TIMING AND CONTROL

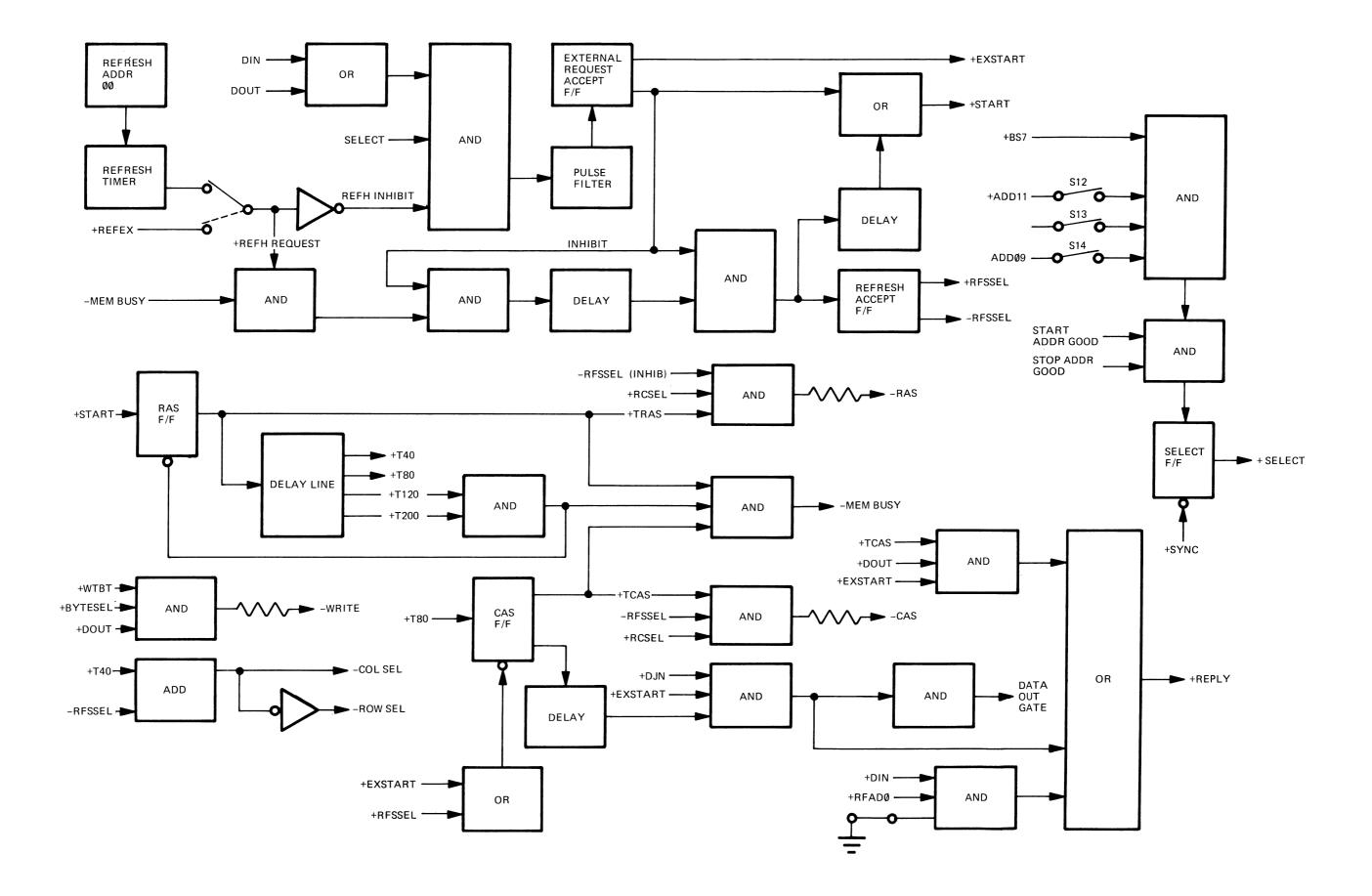

This section consists of a discussion of the timing and control involved in the external request, read, write, read-modify-write, and refresh cycles of the NS23P. Refer to the Timing and Control block diagram (Figure 2-6) for a more detailed breakdown of the timing and control section.

## 2.6.1 CYCLE TIMING

Except for an internal refresh cycle, timing and control are initiated through the external cycle flip-flop (Figure A-1, sheet 2, zone D4) Hll pins 8, 9, and 10, and the gates at pins 11, 12, and 13. Internal refresh control is provided by flip-flop J6

through output pins 9 and 8.

Row address select timing (TRAS) is provided by IC ElO, a 74S74 D-type flip-flop with output pins 5 and 6. Column address select timing (TCAS) comes from IC ElO, output pins 9 and 8.

The 74Sl0 IC gates F9 and H9 are the reply functions for read and write, and for refresh replay if active.

IC Fll controls a digital delay line for address timing. It is digital in that it accepts TTL signals as input and produces buffed TTL signals as output and requires no terminating resistors.

The discrete circuitry composed of a 100-ohm resistor, a 15pF capacitor and two 4.7k resistors in zone D5 smooths the output from the IC gate H9 pin 6. Its function is to allow the external flip-flop to be set and prevent fault settings of that flip-flop that may occur if a refresh request and external request are made coincidentally.

The arbitration circuitry for coincidental refresh and external requests is made up of gates H10 pins 12 and 13 and output pin 11, H10 pins 4, 5, and 6, a resistor-capacitor delay network made up of a 4.7k resistor and 10pF capacitor, and IC E9 pins 11, 12, and 13, and permits only one request to be honored at any time.

## 2.6.1.1 External Request

An external request is made on the external lines DIN or DOUT, run through a NOR gate at F6, and applied as an input at gate H9 pin 5. When H9 output pin 6 goes low, the external request flipflop is set with H1l output pin 10 going low, and H10 output pin 3 going high. The H10 pin 3 output becomes input to the row address select flip-flop E10, which sets its output pin 5 high and begins the row select timing (TRAS) and the delay line at F11. At time T40, 40 ns after the row select has been initiated, output pins 11 and 6 of the row-column address multiplexer F8

Figure 2-6. Block Diagram Timing and Control

deselect the row address and select the column address. At time T80 the clock input pin 11 of E10, the column select timing flip-flop, is set and begins the column address select term to the memory array (TCAS).

## 2.6.1.2 Read Cycle

In a read cycle, the output of the column address select flip-flip ElO pin 8 goes low. This sets F5 pin 5 low, output pin 6 high through a 100-ohm resistor 330pF capacitor delay, and inputs at IC F9 pin 1. This signal along with the DIN input signal at F9-2 sets the F9 output pin 12 to low which connects to F9 input pin 11. F9 output pin 8 goes high forming the reply term REPLY for the response of the memory to the DIN signal for a read cycle. Figure 2-7 shows the internal timing of these events.

## 2.6.1.3 Write Cycle

The timing for a write cycle is very similar to the read cycle, except that the column address select term (TCAS) is not used to produce reply. REPLY is generated by Nanding, + DOUT with + EXSTART, producing a low output at H9-12. The H9 pin 12 output is input at F9 pin 10 and output as the REPLY term for a write cycle. Figure 2-8 shows the internal timing of these events.

## 2.6.1.4 Read-Modify-Write

As mentioned in paragraph 2.5.3, the read-modify-write cycle is no more than a read cycle followed by a write cycle. Figure 2-9 shows the internal timing of this cycle.

## 2.6.1.5 Refresh Cycle

To begin a refresh cycle, the one-shot refresh timer J7 (Figure A-1, sheet 3, zone A7) times out with IC J7 output pin 10 set low. If the internal refresh jumper has been selected, that output runs to the input at gate J8 pin 11 and, if the refresh is not killed from the external world, J8 output pin 13 goes high, generating the refresh request signal REFRQ. Refer to figures 2-10 and 2-11 for the internal refresh and external refresh timing events, respectively.

The REFRQ signal is routed to three places (Figure A-1, sheet 2): J6 pin 13, J8 pin 2, and H8 pin 1. The incoming high signal at J6 pin 13 enables the refresh flip-flop clear input. J8 pin 2 sends J8 output pin 1 low, disabling any select inputs from the external world at gate H9 pin 3. When the high signal is presented at H8 pin 1 and the memory is not busy at pin 2, the output pin 3 goes high, which runs to input at H10 pin 12. If an external cycle is present or not being honored, as determined by H10 pin 13 being high, the H10 output pin 11 goes low, the H10 output pin 6 goes high, then is run through a 50 ns delay network composed of a 4.7k resistor and a 10pF capacitor. With a slow rising edge that forms at the delay, the signal is input at E9 pin 13 and, when the threshold is reached, E9 output pin 11 goes low and the output at F5 pin 8 goes high, clocking the refresh flip-flop J6 at its clock input pin ll. When J6 output pin 9 goes high and pin 8 goes low for the complement, indicating that a refresh cycle is being performed, the refresh select (RFSSEL) disables the row-column address multiplexer and enables the refresh address driver. An additional time delay is introduced through gate H8 pin 10 by a 4.7k resistor and 10pF capacitor network; this is then input to E9 pin 1, allowing time for those multiplexers to change state and set up the refresh address to the memory chip.

NOTE: THE MINIMUM TIMING IS SHOWN

Figure 2-7. Read Cycle (DATI) - Internal Timing Diagram

Figure 2-9. Read-Modify-Write Cycle (DATIO-B) - Internal Timing Diagram

Figure 2-10. Internal Refresh Cycle

# TIME - NANOSECONDS

NOTE: THE MINIMUM TIMING IS SHOWN

Figure 2-11. External Refresh Cycle

When E9 pin 3 goes low, H10 pin 3 goes high, beginning the timing chain by setting the output of E10 pin 5 high to start the first refresh cycle. The TRAS flip-flop E10 output pin 5 going low, cleared by the timing terms input to E11 pins 4 and 5 and output E11 pin 6 going low, sending E10 pin 1 low, forms the refresh address clock at E9 pin 8. This rising edge changes the least significant refresh address, address 0, to memory. When -MEMBUSY becomes unbusy at H8 pin 2 going high, this again begins the second refresh timing edge, proceeding through gate H10 pin 11, E9 pin 11, H10 pin 8, E9 pin 3, then finally through H10 pin 3, and back to the RAS flip-flop E10 pin 3.

When the second refresh cycle has been completed, the 74S74 flip-flop J6 (Figure A-1, sheet 3, zone B8) output pin 6 goes high, that triggers the one-shot timer J7 pin 4, which forms a slight delay. Its output at pin 7 then triggers the one-shot time J7 at pin 12, and its output deselects the refresh request. When 15 microseconds elapse, the time constant for the IC J7, the dual refresh cycle begins again.

If jumper W4 (Figure A-1, sheet 3, zone A3) is closed for external refresh, the external request begins with the refresh request signal (+REFEX) input to gate H6 pin 1, which gets inverted to a low at gate H6 pin 3 then becomes +REFRQ at gate J8 pin 13, just as with the internal request.

### 2.6.2 RESERVED I/O

Under the standard card configuration, signal BS7 to the memory looks at the upper 4k, as I/O reserve; however, the user may gain more active read-write memory by switch-selecting only the upper 2k, lk, or 512-words as peripheral or I/O reserve.

The reserved I/O switches are shown as S12-S14 at location F3, Figure A-1, sheet 3, zone B3. Closing the switches limits the I/O reserve by routing address terms ADO11, ADD10, or ADD9 through the switches to gate F7 output pin 6 to form an additio-

nal arm of the module select term. The address terms ADD11, 10, and 9, as well as BS7 must be in their active state.

## 2.7 MEMORY ADDRESSING

Low order addressing is done by the three 74S373 IC's El, E2, and Fl (Figure A-1, sheet 3, zone 6). Inputs to these IC's form the row and column addresses. External addresses are derived from the DAL01-14 lines; internally input signals to El ADD0-5 and AP12 become the row address, and input signals to E2 ADD 6-11 and AP13 become the column address. Refresh addressing is performed by IC Fl, as a driver, in conjunction with H7, the address counter, and is done entirely internally.

IC's El, E2, and Fl have their outputs paralleled to function as a tri-state driver, and are time-multiplexed to switch in and out as needed. When an external cycle is performed, the row select term that is input active low to El pin 1, causes the outputs of El to be enabled; the outputs of E2 and Fl are disabled and the row address is driven to memory. When the column address is issued active low to E2 pin 1, the inputs to El and Fl remain high, and the column address is sent to the memory array. Similarly, at refresh time, -RFSSEL sends pin 1 of Fl low, and El and E2 turn off. The outputs A0-A6 are run through 33 ohm series resistors to damp out any oscillation that might occur in signal transitions to the array.

IC's El and E2, in addition to being multiplexed drivers, are also the row-column latch for external address. The latch term is the G input at El pin ll, and is derived from the bus sync signal (BSYNC). The output of the refresh driver Fl is not latched; it is enabled only at pin l by the output of the refresh select flip-flop J6 pin 8.

Refresh address counter H7 provides five of the six address terms driven to memory. The sixth term, refresh address (RFADO), the least significant address, comes from D-type

flip-flop J6 pin 6. J6 pin 6 toggles from its high state to its low state, addressing once when RFADO is low and once when RFADO is high, thus providing the dual refresh (whether refresh is internal or external). The clock input to J6 pin 3 is the control signal +RFACK generated in the timing control system. J6 is enabled at pin 1 by +RFSSEL, which is active high when refresh is enabled. When the memory is not performing a refresh, +RFSSEL goes low and clears J6, placing the output at pin 5 low. Refresh counter H7 is also clocked at pin 1 by J6 output pin 5.

The higher order address terms are sent to IC's H3, H4, H5 pin 10, and H5 pin 5. H3, a 74LS283 4-bit full adder, in conjunction with H5, a 74S08 with input pins 4, 5, and output pin 6, and H6, a 74S86, pins 4, 5, and output pin 6, form a 5-bit binary adder and produce the start address control term of the output of H3 pin 9 (upper right hand quadrant of Figure A-1, sheet 3). This term, run through switch S11 to IC F7 pin 10, selects and determines whether the address term presented to it on the bus is above or equal to the selected address toggled into switches S1-S5 at E3.

IC H4, in conjunction with H5 pin 9, 10, and 8, forms a 5-bit adder that performs the stop address function by comparing the external address with the address set in E3 switches S6-S10. The output of H4 pin 9 is the carry term which, when active high, sends H6 pin 8 and F7 pin 12, active low, and determines that the external address is outside the selected range. Similarly, the output of H3 pin 9, when switch S11 is activated, sets F7 pin 10 high and determines that the external address is within the selected range.

If the external address is within the selected range, if refresh is not being initiated, if the dc power is on, and if the bank select has not been asserted, then F7 output pin 8 goes low and J8 output pin 4 sends a high signal to input pin 14 of F4, the select latch, which sends its output pin 15 high forming the

signal +SELECT and allowing the memory to perform an external cycle.

#### SECTION 3

### INSTALLATION

This section contains the basic information for installing the NS23P memory card.

### 3.1 TOOLS REQUIRED

A ball-point pen or small stylus may be needed to set the switches mounted on the memory card. Otherwise, no special tools are required for installation.

## 3.2 UNPACKING AND INSPECTION

The memory card should be unpacked with care and examined for physical shipping damage (i.e., broken, bent or dented parts).

## NOTE

If physical damage is apparent, do not attempt to install or operate the memory card.

## 3.3 CONFIGURATION

The NS23P card has a switch selectable option for the address range to which the memory responds and a switch selectable option for the I/O reserve address range to which the memory does not respond.

## 3.3.1 ADDRESS RANGE SELECTION (EXAMPLE)

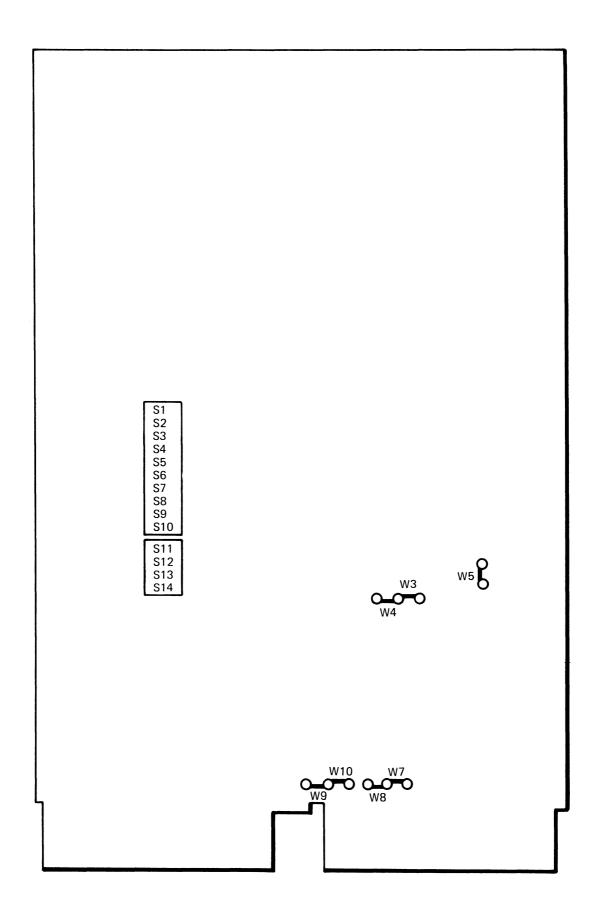

Set switches S1-S5 and S11 for the desired start address; set switches S6-S10 for the desired stop address. The location of the switches is illustrated in Figure 3-1; settings are listed in Table 3-1.

For example, to install the NS23P 16k memory card within the address range of 4k to 20k. The start address is 4k  $(20,000)_8$  and the stop address is 20k  $(117,776)_8$ . Set switches as follows:

| Start-4k |     | Stop | =20k |

|----------|-----|------|------|

| Sl       | OFF | s6   | OFF  |

| S2       | OFF | s7   | OFF  |

| S3       | OFF | S8   | ON   |

| S4       | OFF | S9   | OFF  |

| S11      | ON  | S10  | OFF  |

### 3.3.2 RESERVING I/O SPACE

The upper portion of system address is reserved for peripheral devices, normally for the uppermost 4k bank. The NS23P has the capacity to reduce this space to 2k, 1k or 512 words according to switches S12, S13, and S14. The switches should be set as follows:

| <u>S12</u> | <u>513</u> | <u>S14</u> | Reserved I/O | Space | (Words) |

|------------|------------|------------|--------------|-------|---------|

| OFF        | OFF        | OFF        | 4k           |       |         |

| ON         | OFF        | OFF        | 2k           |       |         |

| ON         | ON         | OFF        | lk           |       |         |

| ON         | ON         | ON         | 512          |       |         |

The locations of the switches are shown in Figure 3-1.

### 3.3.3 ADDITIONAL CONFIGURATION JUMPERS

The NS23P also has factory settable jumpers for the following options: 16k/8k RAMs, internal/external refresh, external refresh RPLY active/inactive, and battery back-up active/inactive. Locations of these jumpers are shown in Figure 3-1. Definitions of jumper installation/removal are shown in Table 3-2.

Figure 3-1. Switch and Jumper Locations

Table 3-1. Address Range Switch Programming

| ABSOLUTE | S5  | S4 | S3 | S2 | S1 | S11 | START |

|----------|-----|----|----|----|----|-----|-------|

| ADDRESS  | S10 | S9 | S8 | S7 | S6 | -   | STOP  |

| 0k       | 1   | 1  | 1  | 1  | 1  | 0   |       |

| 4k       | 0   | 0  | 0  | 0  | 0  | 1   |       |

| 8k       | 1   | 0  | 0  | 0  | 0  | 1   |       |

| 12k      | 0   | 1  | 0  | 0  | 0  | 1   |       |

| 16k      | 1   | 1  | 0  | 0  | 0  | 1   |       |

| 20k      | 0   | 0  | 1  | 0  | 0  | 1   |       |

| 24k      | 1   | 0  | 1  | 0  | 0  | 1   |       |

| 28k      | 0   | 1  | 1  | 0  | 0  | 1   |       |

| 32k      | 1   | 1  | 1  | 0  | 0  | 1   |       |

| 36k      | 0   | 0  | 0  | 1  | 0  | 1   |       |

| 40k      | 1   | 0  | 0  | 1  | 0  | 1   |       |

| 44k      | 0   | 1  | 0  | 1  | 0  | 1   |       |

| 48k      | 1   | 1  | 0  | 1  | 0  | 1   |       |

| 52k      | 0   | 0  | 1  | 1  | 1  | 1   |       |

| 56k      | 1   | 0  | 1  | 1  | 0  | 1   |       |

| 60k      | 0   | 1  | 1  | 1  | 0  | 1   |       |

| 64k      | 1   | 1  | 1  | 1  | 0  | 1   |       |

| 68k      | 0   | 0  | 0  | 0  | 1  | 1   |       |

| 72k      | 1   | 0  | 0  | 0  | 1  | 1   |       |

| 76k      | 0   | 1  | 0  | 0  | 1  | 1   |       |

| 80k      | 1   | 1  | 0  | 0  | 1  | 1   |       |

| 84k      | 0   | 0  | 1  | 0  | 1  | 1   |       |

| 88k      | 1   | 0  | 1  | 0  | 1  | 1   |       |

| 92k      | 0   | 1  | 1  | 0  | 1  | 1   |       |

| 96k      | 1   | 1  | 1  | 0  | 1  | 1   |       |

| 100k     | 0   | 0  | 0  | 1  | 1  | 1   |       |

| 104k     | 1   | 0  | 0  | 1  | 1  | 1   |       |

| 108k     | 0   | 1  | 0  | 1  | 1  | 1   |       |

| 112k     | 1   | 1  | 0  | 1  | 1  | 1   |       |

| 116k     | 0   | 0  | 1  | 1  | 1  | 1   |       |

| 120k     | 1   | 0  | 1  | 1  | 1  | 1   |       |

| 124k     | 0   | 1  | 1  | 1  | 1  | 1   |       |

| 128k     | 1   | 1  | 1  | 1  | 1  | 1   |       |

1 = Switch CLOSED

0 = Switch OPEN

### 3.4 INSTALLATION

The memory card is placed into the backplane's connector slots A and B, or into connector slots C and D; in both cases, as close to the CPU as possible. The memory card's components should face row 1. Positions of components and connector slots are shown in Figure 3-2.

The following precautions should be observed during installation:

- Turn off memory power before installing or removing the memory card to avoid damage.

- Do not attempt to insert the memory card into slot one on the backplanes. Slot one is reserved for the LSI-ll processor on both backplanes.

- If the DDV11-B expanded backplane is being used, insert the memory card into the AB connectors of the backplane.

- The REV11 DMA refresh must be the highest priority DMA device on the bus when this option is being used. If not, refresh may not operate properly and loss of memory data may occur.

- When systems with expansion boxes are being used in addition to the REV11 DMA refresh board, install a REV11-C board (no termination resistors) into row 2A & B (the highest priority row), then install a TEV11 termination board in the last row of the bus.

## 3.5 VERIFICATION

After the NS23P memory card has been installed, apply memory power and verify operation by running system diagnostics to test the memory.

Table 3-2. Option Jumpers

| Jumper    | Status | Function                                                      |

|-----------|--------|---------------------------------------------------------------|

| W3<br>W4  | I<br>R | Internally controlled on-board Refresh                        |

| W3<br>W4  | R<br>I | Externally controlled Refresh                                 |

| W5<br>W6  | I<br>R | Refresh reply disabled for Externally controlled Refresh.     |

| W5<br>W6  | R<br>I | Refresh reply enabled for Externally controlled Refresh.      |

| พ7<br>พ8  | I<br>R | Configuration for +5V power For non-battery Back-up System.   |

| W7<br>W8  | R<br>I | Configuration for +5V power For battery back-up systems.      |

| W9<br>W10 | I<br>R | Configuration for +12V power For non-battery back-up systems. |

| W9<br>W10 | R<br>I | Configuration for +12V power For battery back-up systems.     |

Note: See assembly drawings sheet 2, and Table 3-2A below, for jumper locations and information.

I = Install

R = Remove

Table 3-2A. Option Jumpers

| w3         | =  | J | to | K |

|------------|----|---|----|---|

| W4         | =  | Н | to | J |

| <b>W</b> 5 | =. | M | to | N |

| <b>W</b> 7 | =  | E | to | F |

| W8         | =  | D | to | E |

| W9         | =  | A | to | В |

| W10        | =  | В | to | С |

|            |    |   |    |   |

Figure 3-2. Module Installation

- (TBD)

- MOS/CORE memory exercizer for 0 to 124k with or without parity bits.

#### SECTION 4

### MAINTENANCE AND TROUBLESHOOTING

### 4.1 MAINTENANCE

The NS23P memory card does not require routinely scheduled maintenance checks. However, systems diagnostics for both the NS23P memory card and the LSI-ll Microcomputer System should be performed occasionally to verify correct operation.

## 4.2 TROUBLESHOOTING

If problems occur, check the following:

- Are the address range switches and the I/O reserve switches set properly?

- Are the option jumpers installed/removed for the appropriate features?

- Are all power supplies turned on? Make sure that +5V and +12V power is applied to the backplane.

- Has the DMA priority daisy chain been maintained? Verify that there are no empty slots between the first and last board.

- Are the system cables installed correctly? Check that the cables are connected at both ends.

# Appendix A

# Reference Drawings

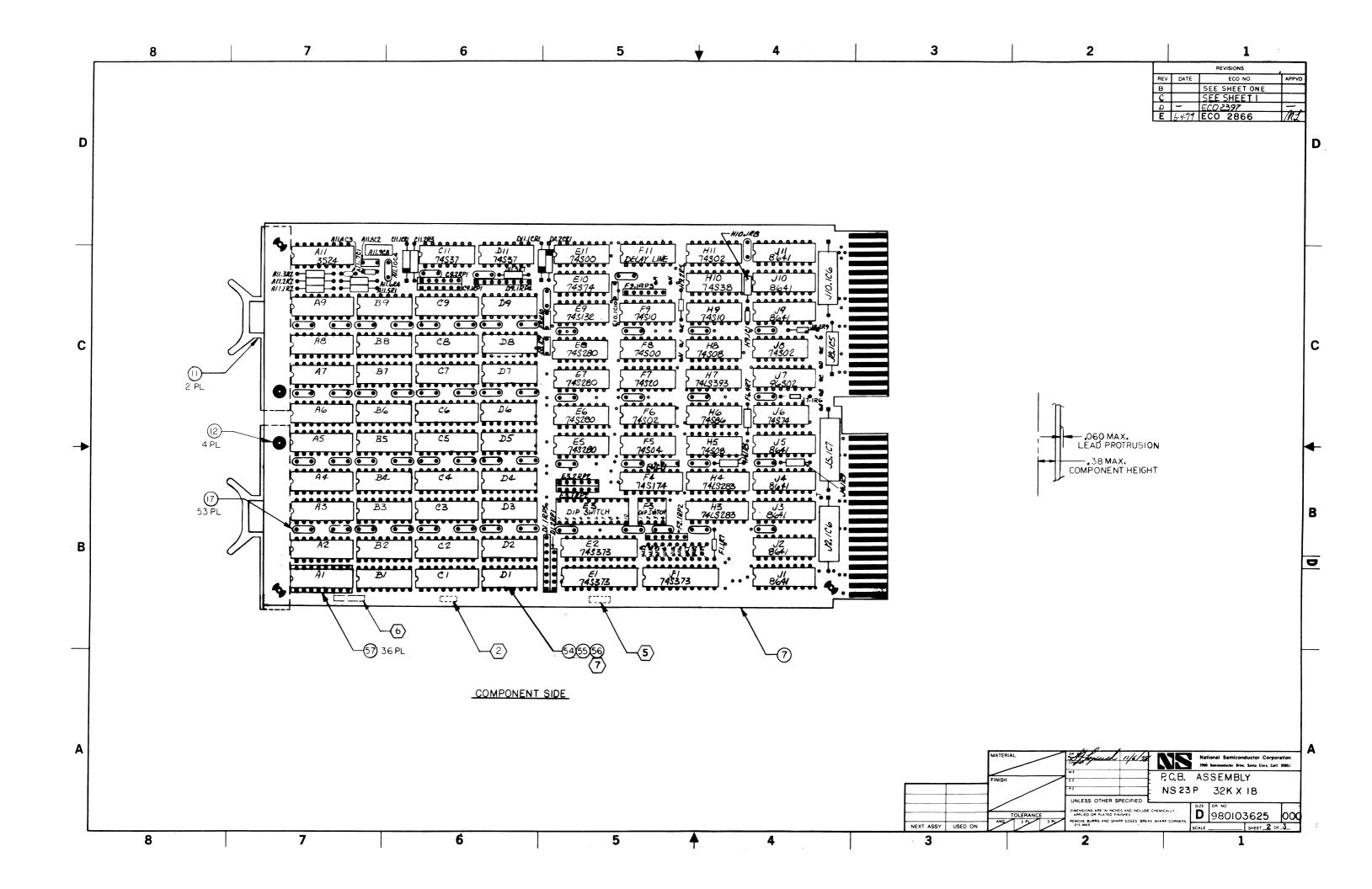

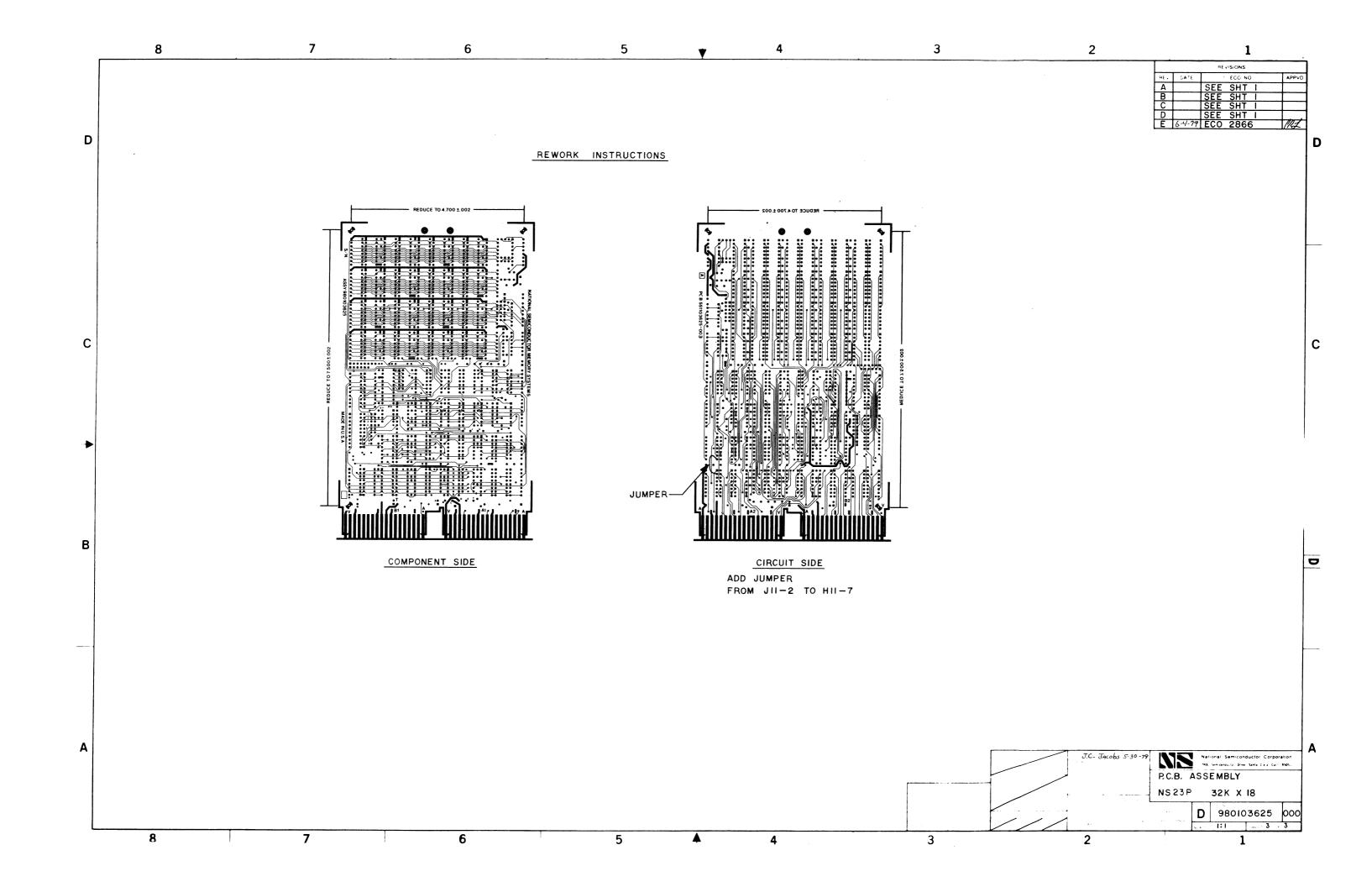

This appendix contains the required reference schematic and assembly drawings for the NS23P memory.

Figure A-1 870103625-001 Schematic Figure A-2 980103625-000 Assembly

| OF<br>MEAS          | . 02     | EACH<br>INCH  | OE OE   |       | ULK<br>S REQU<br>THER | Š       | KEY<br>(1) | D        | • WITH<br>• WITH<br>• REFE | RENC       | Œ     | KEY .                |          |               |              | RELI  | EASED F | OR ASSEMBLY   |               | 03625-00          |

|---------------------|----------|---------------|---------|-------|-----------------------|---------|------------|----------|----------------------------|------------|-------|----------------------|----------|---------------|--------------|-------|---------|---------------|---------------|-------------------|

| ITEM/<br>FIND<br>NO |          | ì             | UANTI   | TY PE | A ASSE                | MO L    | Ì          | 000      | UNIT<br>OF<br>ME AS        | KEY<br>(1) | (2)   |                      | RT NUMBE |               |              | ŤI    | TLE/DES | CRIPTION      | REF<br>DESIG. | REMARKS           |

| 1                   |          |               | Т       | Т     |                       | Г       | Π          |          |                            |            |       |                      |          | ,             |              |       |         |               |               |                   |

| 2                   |          |               | T       | T     | T                     |         |            |          |                            |            |       |                      |          | -             |              |       |         |               |               |                   |

| 3                   |          |               |         | Τ     | T                     |         | Π          | 0        | 04                         | R          |       | 87010                | 362      | 5-001         | SCHEN        | ITAN  | C       |               |               |                   |

| 4                   |          |               |         | T     |                       | Г       | Π          |          |                            |            |       |                      |          |               |              |       |         |               |               |                   |

| 5                   |          | T             |         | Τ     | Т                     |         |            | 0        | 04                         | S          |       | 4261                 | 0362     | 5-001         | PRODU        | CT ST | PEC ¢   | INSTAL, PRO   | c.            |                   |

| 6                   |          | T             | Т       | Τ     | T                     |         |            | 0        | 04                         | S          |       | 4251                 | 3625     | - ∞ı          | TEST S       | PECIF | ICAT    | 104           |               |                   |

| 7                   |          |               |         | T     |                       |         |            | 1        | 04                         | D          | 1     | 55110                | 362      | 5-00 <b>3</b> | P.C. BO      | DAR   | D       |               |               |                   |

| 8                   |          |               |         | Т     | 1                     |         |            | 0        | 04                         | D          |       | 60010                | 0158     | -005          | WIRE,P       | VCy#3 | 30,50   | LID, GRN      |               | W3,4,5,11-19      |

| 9                   |          |               |         | Τ     | T                     |         |            |          |                            |            |       |                      |          |               |              |       |         |               |               |                   |

| 10                  |          | Т             | T       | Т     | Т                     | Г       | Π          | 0        | 04                         | D          |       | 60010                | 0155     | -005          | WIRE,        | PVC,  | #24,    | SOLID, GRN    | 1             | . W7-W10          |

| 11                  |          | T             | T       | T     | Ī                     |         | T          | 2        | 04                         | ۵          |       | 74010                | 0100     | 5-001         | HANDL        | E     |         |               |               |                   |

| 12                  |          |               |         | Ι     |                       |         | Π          | 4        | 04                         | Ω          |       | 28310                | 1130     | -003          | RIVET        | , 1/8 | × 3,    | /16           |               |                   |

| $\bar{\omega}$      |          |               | $\perp$ |       |                       |         |            | 11       | 04                         | А          |       | 28310                | 2019     | -001          | WIRE-WE      | RAP P | ost,    | .025 SQ       | A,B,C         | D, E, F, H, J, K, |

| 14                  |          |               |         |       |                       |         |            | 2        | 04                         | D          |       | 15110                | 1308     | -025          | CAP., C      | ER,I  | 000     | pf, 100V, ±10 | 0% CI         |                   |

| 15                  |          | T             | T       | T     |                       |         |            |          | 04                         | ۵          |       | 151101               | 308-     | 037           | CAP, CE      | R,.0  | λωF,    | 50V, + 80:    | z c2          |                   |

| 16                  |          | $-\mathbf{I}$ | $\perp$ | Ι     |                       |         |            | =        | 04                         | D          |       | 15100                | 0048     | -001          | CAP, CE      | R,.   | μF,     | 50V, + 80     | % C3          |                   |

| ASSY                |          |               |         |       |                       |         |            |          | NOTE                       | \$         |       |                      |          |               |              |       |         |               |               |                   |

| USAGE<br>REF        | $\vdash$ | +             | +       | +     | 1                     | _       |            |          |                            | RE         | v     | В                    | C        | D             | E            |       | TITLE   |               |               |                   |

|                     | П        | #             | I       |       |                       |         |            |          | ENG.                       | СН         | G NO. | 3034F                |          |               | EC 0<br>2866 |       | 1       | NS 23 F       | >             |                   |

|                     | $\vdash$ | +             | +       | +     | +                     |         | -          | $\vdash$ | СНС                        | DA         | TE    |                      |          |               | 9 6-4-79     |       | 1       |               |               |                   |

| WRITTE              |          |               | DATE    | D€    | SIGN                  |         | 0          | ATE      |                            | AP         | PR    | 100                  | Se       | THIA          | Int          |       |         | 32K X         | ıα            |                   |

| SGO<br>CHECKE       | D 8 Y    | 9-            | DATE    | 2     | 80                    | l<br>ma | 112        | 2        | 1                          | Y          | 1     | Mationa<br>2900 Somi |          |               | Corporatio   |       | SIZE    | 98010         |               | 5-000 of <u>5</u> |

| UNIT<br>OF<br>MEAS | 02  | • E A<br>• IN<br>• FE | Сн       | 06   | • 80<br>• AS | REQ      | D    | KEY<br>(1) | D        | · WITH<br>· WITH<br>· REFE | REN                                                                                                             | CE         | KEY . |         |          |                  | REL  | EASED FOR A             |          |               | 3625-0 <b>0</b>              |

|--------------------|-----|-----------------------|----------|------|--------------|----------|------|------------|----------|----------------------------|-----------------------------------------------------------------------------------------------------------------|------------|-------|---------|----------|------------------|------|-------------------------|----------|---------------|------------------------------|

| FIND<br>NO         |     | 1                     | OUA<br>T | NTIT | YPER         | ASSI     | EMBL | ٧.         | .0α      | OF<br>ME AS                | KEY                                                                                                             | KEY<br>(2) |       | AT NUMB |          |                  | Ť    | ITLE/DESCRIP            | TION     | REF<br>DESIG. | REMARKS                      |

| 17                 | _   | 1                     | 1        | H    | +            | +        | 1    | +          | 53       | _                          | Ь                                                                                                               | 1          | 1510  | 0005    | 5-001    | CAP, CE          | R .  | 474F. 50                | v + 80°  | C4            | <del> </del>                 |

| 18                 | _   | t                     | 1        | 1    | T            | T        | +    | +-         | 1        | 01                         | 6                                                                                                               | <u> </u>   |       |         |          | CAP, CE          |      |                         |          |               |                              |

| 19                 |     | T                     |          |      |              | †-       |      | +          | 2        | 01                         | D                                                                                                               | 1          |       |         |          | CAP, TAI         |      |                         |          |               |                              |

| 20                 |     | T                     | 1        |      | $\vdash$     |          |      | T          | 1        | 01                         | D                                                                                                               |            |       |         |          | CAPTA            |      |                         |          |               | <u> </u>                     |

| 21                 |     |                       | Τ        | Г    | $\vdash$     | T        | 1    |            | T        | 01                         | D                                                                                                               | $\vdash$   |       |         |          | CAP, TA          |      |                         |          |               | KEMET<br>T 330 D 226M - 035/ |

| 22                 |     |                       |          | Г    |              |          |      | Γ          |          |                            |                                                                                                                 | T          |       |         |          |                  |      |                         |          |               | 1                            |

| 23                 |     | Τ                     | Г        | Г    |              |          |      | T          | 1        | 01                         | D                                                                                                               |            | 15110 | 1308-   | 001      | CAP, CE          | R,10 | ) <sub>P</sub> F, 100 V | 1, ± 10% | C9            |                              |

| 24                 |     |                       |          | Γ    | T            |          | Γ    | T          | 2        | 01                         | D                                                                                                               |            | 15110 | 1308    | -003     | CAP, CE          | R,15 | pF,100                  | V, ± 10% | CIO           | CKOSBXISOK                   |

| 25                 |     |                       |          |      | Γ            |          | Γ    |            | 1        | 01                         | D                                                                                                               |            | 15110 | 1 308   | -019     | CAP, CEF         | ٦,33 | 30 pF, 10               | 0V,±10%  | CII           | CKOPBY331K                   |

| 26                 |     | Γ                     | Ι.       |      |              | Γ        | Г    | Г          | Г        | Г                          |                                                                                                                 |            |       |         |          |                  |      |                         |          | T             |                              |

| 27                 |     |                       |          |      | Γ            |          |      |            | 1        | 01                         | D                                                                                                               |            | 4741  | 02565   | -038     | RES, FIL         | _M,  | 2.21K, /                | 8W, 17   | RI            | MIL-R-10509                  |

| 28                 |     |                       |          |      |              |          |      | Ι          | 3        | 01                         | D                                                                                                               |            |       |         | -073     | 4 4              |      | 5.11K,                  | 4 4      | R2            | SINF                         |

| 29                 |     |                       |          |      |              |          |      | L          | 1        | 01                         | D                                                                                                               |            |       |         | -117     |                  |      | 15.0K,                  | •        | R3            | . 1502F                      |

| 30                 |     |                       |          |      | L            | L        | L    |            | 1        | 01                         | D                                                                                                               |            | 47410 | 2565    | -166     | , FIL            | м,   | 51.1K,                  | ,17      | R4            | RN850 5112F                  |

| 31                 |     | L                     |          |      | L            |          |      |            | 2        | 01                         | D                                                                                                               |            | 47010 | 1134    | -039     | · • ,cc          | , 10 | OR,                     | ±5%      | R5            | A-8<br>BB-161-5              |

| 32                 |     |                       |          |      |              |          |      |            | 1        | 0                          | Ω                                                                                                               |            | 4701  | 01134   | -089     | RES, CC          | , 12 | 2K, /81                 | ٧,±5%    | R6            | 88-123-5                     |

| ASSY<br>SAGE       |     |                       |          |      |              |          |      |            |          | MOTE                       | s                                                                                                               |            |       |         |          |                  |      |                         |          |               |                              |

| REF                |     |                       |          |      |              |          |      |            |          |                            | RE                                                                                                              | v .        | B     | 10      | 0        | E                |      | TITLE                   |          |               |                              |

| - [                |     |                       |          |      |              |          |      |            |          | ENG.                       | Сн                                                                                                              | G NO.      | SEE   | SEE     | ECO 2907 | ECO<br>2866      |      | <b>1</b> N              | S 23     | Р             |                              |

| ŀ                  | -   | -                     | Н        |      |              | $\vdash$ | -    | Н          | $\dashv$ | CHG                        | 0,                                                                                                              | TE         | 10.1  | +       | _        | 64-79            |      | 1                       |          |               |                              |

| RITTEN             | 84  |                       | D        | ATE  | DES          | IGN      |      | D          | ATE      |                            | 40                                                                                                              | PR         |       |         | _        | VRZ.             |      | 1 3                     | 2K X     | 18            |                              |

| HECKEC             | 8 * |                       | D        | ATE. | APP          | ROVE     | D    | D          | ATE      | 1                          | Mational Semiconductor Corporation 200 Semiconductor Drin, Scott 10051  SIZE  SIZE OF MATERIAL NO 980103625-000 |            |       |         |          | 000 su 2<br>or 5 |      |                         |          |               |                              |

| UNIT<br>OF<br>MEAS | . ( | 01 • E<br>07 • I<br>03 • F | NCH     | 05                                               |      | JLK<br>S REOK<br>THER | 0             | KEY<br>(1) | 0   | · WITH<br>· WITH<br>· REFE<br>· SPEC | OUT<br>REN                                                                                       | CE       | KEY . |         |             |          | RELE        | ASED F  | OR ASSEMBLY |               | 3625             |      |

|--------------------|-----|----------------------------|---------|--------------------------------------------------|------|-----------------------|---------------|------------|-----|--------------------------------------|--------------------------------------------------------------------------------------------------|----------|-------|---------|-------------|----------|-------------|---------|-------------|---------------|------------------|------|

| FIND<br>NO         | F   | _                          | OUA     | MTIT                                             | Y PE | ASSE                  | <b>***</b> ** | Ť          | loo | UNIT<br>OF<br>ME AS                  |                                                                                                  | (E)      |       | T NUMBE |             |          | T1          | TLE/DES | CRIPTION    | REF<br>DESIG. | REMA             | ARKS |

| 49                 | t   | +                          | +       | ┢                                                | +    | +                     | ✝             | ┿          | +   | 04                                   | -                                                                                                | +        | 4800  | 00083   | - 001       | DIODE    | · IN        | 9141    | 3           | CRI           | <del> </del>     |      |

| 50                 | t   | +                          | +       | 1                                                | +    | +                     | <del> </del>  | t          | ╁   | ř٠                                   | +                                                                                                | $\vdash$ | 1000  | ,0000   | - 551       | DIODE    | , ,,,,      |         |             | 10111         | <del> </del>     |      |

| 51                 | t   | +                          | +-      | <del>                                     </del> | +    | +                     | 1             | 1          | 1   | 04                                   | D                                                                                                | †        | 48210 | 4567    | -002        | REG. PU  | LSE W       | /IDT    | MODULATO    | PR            | LM 352           |      |

| 52                 | t   | +                          | †       |                                                  | 1    | T                     | t             | +          | +   | ř                                    | ۲                                                                                                | t        |       |         |             |          |             |         |             | +             | LFISSZ           | 40   |

| 53                 | t   | +                          | +       |                                                  | t    | T                     | 1             |            | 1   | 04                                   | Ь                                                                                                | $t^-$    | 61110 | 4536    | -005        | DELAYLI  | NE AC       | TIVE.   | 200NS, 5-T  | AP            | 90LAHA 1         | enes |

| 54                 | t   | $\top$                     | 1       |                                                  | t    | T                     |               |            | 0   | 04                                   | 1                                                                                                | 1        |       |         |             | 1.C. 16  |             |         |             | +             | 7                | -    |

| 55                 | t   | $\top$                     | +       |                                                  | t    | 1                     |               |            | lō  | 04                                   | Г                                                                                                | $\vdash$ |       |         |             |          |             |         | SOONS       | +             | 闭                |      |

| 56                 | t   | 1                          | 1       |                                                  | T    | T                     | 1             | T          | 0   | 04                                   | 1                                                                                                |          |       |         |             |          |             |         | 1,200NS     | _             | ( <del>7</del> ) |      |

| 57                 | T   | T                          |         |                                                  | T    |                       |               |            | 36  | 01                                   | D                                                                                                | Т        | 21410 | 2685    | -003        | SOCKE    | T, DIL      | , 16    | -PIN        | 1             |                  |      |

| 58                 | Г   |                            | 1       | 1                                                |      |                       |               | į`         |     |                                      |                                                                                                  |          |       |         |             |          |             | ,       |             | 1             |                  |      |

| 59                 | r   | T                          | T       | Г                                                | Г    |                       |               | 1          | T   | 01                                   | D                                                                                                |          | 48210 | 2062    | -001        | I.C. 96  | 502         |         |             |               |                  |      |

| 60                 | T   | T                          | T       |                                                  | T    | Τ                     | Г             |            | 8   | 01                                   | D                                                                                                |          | 48210 | 3697    | -001        | I.C. 86  | 41          |         |             | _             |                  |      |

| 61                 | Γ   | T                          | Ι       |                                                  |      |                       | Γ             | Π          | 2   | 01                                   | D                                                                                                |          | 48200 | 00079   | 1-001       | I.C. 74  | 500         |         |             |               |                  |      |

| 62                 | Γ   |                            | Т       |                                                  | П    | П                     | Γ             | Π          | 3   | 01                                   | D                                                                                                |          | 48200 | 00334   | 1-001       | I.C. 74  | 502         |         |             |               |                  |      |

| 63                 | Г   |                            | Т       |                                                  | Γ    |                       |               | Г          | 1   | 01                                   | D                                                                                                |          | 4820  | 20180   | - 001       | I.C. 74  | S04         |         |             | 1             |                  |      |